## Tightly-Coupled and Fault-Tolerant Communication in Parallel Systems

Inauguraldissertation zur Erlangung des akademischen Grades eines Doktors der Naturwissenschaften der Universität Mannheim

> vorgelegt von Dipl.-Inf. David Christoph Slogsnat aus Heidelberg

> > Mannheim, 2008

Dekan: Prof. Dr. Matthias Krause, Universität Mannheim

Referent: Prof. Dr. Ulrich Brüning, Universität Heidelberg

Koreferent: Prof. Dr. Reinhard Männer, Universität Heidelberg

Tag der mündlichen Prüfung: 4. August 2008

#### Abstract

The demand for processing power is increasing steadily. In the past, single processor architectures clearly dominated the markets. As instruction level parallelism is limited in most applications, significant performance can only be achieved in the future by exploiting parallelism at the higher levels of thread or process parallelism. As a consequence, modern "processors" incorporate multiple processor cores that form a single shared memory multiprocessor.

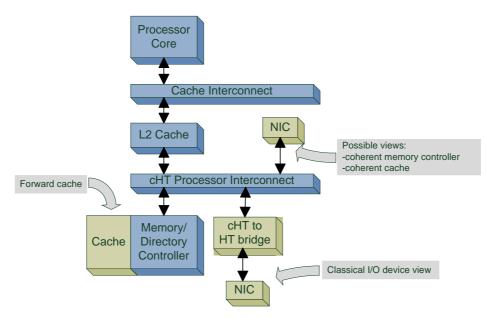

In such systems, high performance devices like network interface controllers are connected to processors and memory like every other input/output device over a hierarchy of peripheral interconnects. Thus, one target must be to couple coprocessors physically closer to main memory and to the processors of a computing node. This removes the overhead of today's peripheral interconnect structures. Such a step is the direct connection of Hyper-Transport (HT) devices to Opteron processors, which is presented in this thesis.

Also, this work analyzes how communication from a device to processors can be optimized on the protocol level. As today's computing nodes are shared memory systems, the cache coherence protocol is the central protocol for data exchange between processors and devices. Consequently, the analysis extends to classes of devices that are cache coherence protocol aware. Also, the concept of a transfer cache is proposed in this thesis, which reduces latency significantly even for non-coherent devices.

The trend to the exploitation of process and thread level parallelism leads to a steady increase of system sizes. Networks that are used in such large systems are very susceptible to both hard and transient faults. Most transient fault rates are constant per bit that is stored or transmitted. With increasing system sizes and higher clock frequencies, the number of faults in time increases drastically. In the end, the error rate may rise at a level where high level error recovery becomes too costly if lower layers do not perform error correction that is transparent to the layers above. The second part of this thesis describes a direct interconnection network that provides a reliable transport service even without the use of end-to-end protocols. Also, a novel hardware based solution for intermediate routing is developed in this thesis, which allows an efficient, deadlock free routing around faulty links.

#### Zusammenfassung

Der Bedarf an Rechenkraft von Computer-System wächst ständig. Insbesondere auf dem Massenmarkt wurde dieser in der Vergangenheit vor allem durch Einprozessorsysteme gedeckt. Die parallele Abarbeitung von Operationen ist dabei ein wesentlicher Faktor zur Geschwindigkeitssteigerung. Da die Parallelität auf Instruktionsebene in den meisten Anwendungen sehr beschränkt ist, sind weitere Leistungssteigerungen nur möglich, wenn auch die Parallelität auf Prozess- und Thread-Ebene genutzt wird. Daher bestehen heutige Prozessor-Chips meist aus mehreren Prozessor-Kernen, die einen gemeinsamen Speicher mit einem globalen Adressraum nutzen.

In solchen Systemen sind hochperformante Netzwerkschnittstellen genauso über eine Hierarchie von Verbindungsnetzwerken und Bussen mit dem System verbunden wie klassische Eingabe/Ausgabe Geräte. Um die Kommunikationsleistung zwischen Prozessor und Netzwerkschnittstelle zu verbessern, ist es erforderlich diese Verbindungsstruktur zu optimieren. Ein solcher Ansatz ist die Entwicklung von Geräten, die über das HyperTransport Protokoll direkt mit dem Prozessorchip verbunden werden können. Eine Umsetzung dieses Konzeptes wird in dieser Arbeit vorgestellt.

Darüber hinaus werden in dieser Arbeit weitere Möglichkeiten zur Verbesserung der Kommunikation untersucht. In heutigen Computersystemen ist das Cache-Kohärenz Protokoll das zentrale Protokoll, welches den Datenaustausch zwischen den Kernkomponenten des Rechners regelt. In dieser Arbeit werden Klassen von Geräten vorgestellt, die direkt als Kommunikationspartner an diesem Protokoll teilnehmen. Als bedeutende Neuerung wird außerdem das Konzept des Transfer Caches in dieser Arbeit entwickelt und vorgestellt, welches die Kommunikationslatenz zwischen Gerät und Prozessor bedeutend verbessert.

Die bessere Ausnutzung der Parallelität auf der Ebene von Prozessen und Threads führt außerdem zu ständig komplexer werdenden Systemen. In Netzwerken, die solche Systeme verbinden, muss mit dem häufigen Auftreten von statischen und transienten Fehler gerechnet werden. In einem solchen System können die Fehlerraten dabei auf ein solches Maß steigen, dass eine ausschließlich in höheren Softwareebenen erfolgende Fehlerbehandlung sehr ineffizient wird. Mit einer Fehlerbehandlung direkt in Hardware kann dieses Problem umgangen werden. In diesem Sinne beschreibt der zweite Teil dieser Arbeit ein fehlertolerantes Verbindungsnetzwerk, welches eine fehlertolerante Übertragung auf der Ebene 8b/ 10b kodierter serieller Links sicherstellt. Eine weitere Komponente des Protokolls ist ein neuartiger hardwarebasierter Mechanismus, der über ein "intermediate routing" eine effiziente und blockierungsfreie Lösung darstellt, um Pakete um fehlerhafte Komponenten herumzuleiten.

## Contents

| CHA | PTER 1 Introduction 1                        |

|-----|----------------------------------------------|

| 1.1 | The Extoll Project                           |

| 1.2 | Physical Implementation                      |

| 1.3 | Graphical Representations                    |

| 1.4 | Methodologies                                |

| 1.5 | A Theoretical Model for cHT/HT Performance   |

| CHA | PTER 2 Communication in Parallel Computers13 |

| 2.1 | Caches                                       |

| 2.2 | Parallel Computing Architectures             |

| 2.2 |                                              |

| 2.2 |                                              |

| 2.2 |                                              |

| 2.2 | .4 Send-Receive                              |

| 2.3 | Device Integration Design Space              |

| 2.3 |                                              |

| 2.3 | .2 Device Virtualization                     |

| 2.4 | Cache Coherence for Shared Memory Systems    |

| 2.4 |                                              |

| 2.4 |                                              |

| 2.4 |                                              |

| 2   | .4.3.1 MOESI                                 |

| 2   | .4.3.2 MESIF                                 |

| 2.4 | .4 Directory-Based Protocols                 |

| 2.4 | .5 Serialization of Conflicting Accesses     |

| 2.5 | Introduction to x86 Systems                  |

| 2.5 | -                                            |

| 2.5 | .2 AMD                                       |

| 2.6 | Examples of Parallel Systems                 |

| 2.6 | .1 Sun UltraSPARC T2                         |

| 2.6 | .2 Cray T3E                                  |

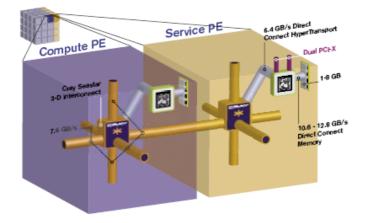

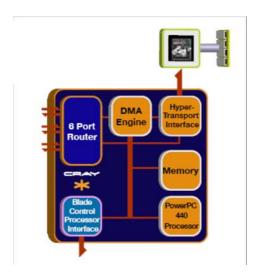

| 2.6 | .3 Cray XT3 and XT4                          |

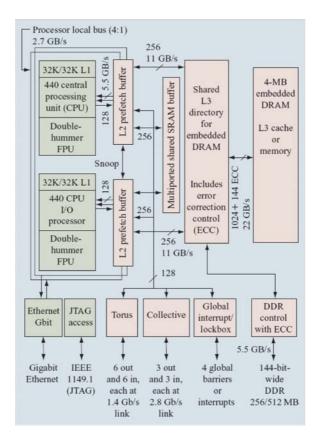

| 2.6 | .4 IBM BlueGene/L                            |

Ι

| 2.6.5  | NIs on Standardized Peripheral Interfaces                  | 4 |

|--------|------------------------------------------------------------|---|

| СНАРТ  | <b>TER 3</b> Improving Device to Processor Communication 6 | 5 |

| 3.1 Hy | yperTransport Devices and Accelerators                     | 6 |

| 3.1.1  | The HyperTransport Protocol                                | 7 |

| 3.1.2  | I/O in HTX Systems                                         | 0 |

| 3.1.3  | Ordering in PIO7                                           | 1 |

| 3.1.4  | Ordering PIO Write Requests                                | 3 |

| 3.1.5  | Ordering PIO Read Requests7                                | 6 |

| 3.1.6  | Potential Incremental Solutions7                           | 6 |

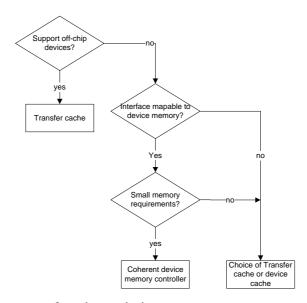

| 3.2 Th | ne Space of Analysis                                       | 6 |

| 3.2.1  | Latency-Sensitive Data                                     | 6 |

| 3.2.2  | Buffering7                                                 | 8 |

| 3.2.3  | Feasible Solutions                                         | 0 |

| 3.3 M  | emory and Interconnect Bottlenecks                         | 1 |

| 3.3.1  | Influence of the Cache Coherence Protocol                  | 5 |

| 3.3.2  | Summary                                                    | 7 |

| 3.4 De | evices at the Coherent Interconnect                        | 8 |

| 3.4.1  | Devices with Coherent Caches                               |   |

| 3.5 Th | ne Performance of Coherent Transfers9                      |   |

| 3.5.1  |                                                            |   |

| 3.5.1  | 1.1 Off-SOC Devices                                        | 8 |

|        | 1.2 Devices with Caches in SOCs    10                      |   |

|        | Devices with a Coherent Memory Controller                  |   |

| 3.6 Tr | ansfer Cache                                               | 3 |

| 3.7 Re | esults                                                     |   |

| 3.7.1  | Conclusion                                                 |   |

| 3.7.2  | Related Work                                               | 9 |

#### CHAPTER 4 HT and cHT Prototypes

| 4.1   |                               | 110 |

|-------|-------------------------------|-----|

| 4.1 1 | he HT Core and Interface      |     |

| 4.1.1 | Results                       | 115 |

| 4.2 T | he Coherent HT Infrastructure | 117 |

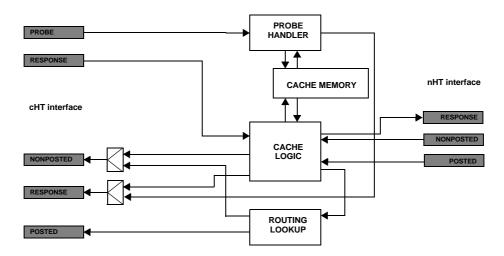

| 4.2.1 | The Coherent Fabric           | 117 |

| 4.2.2 | Units and Crossbars           | 118 |

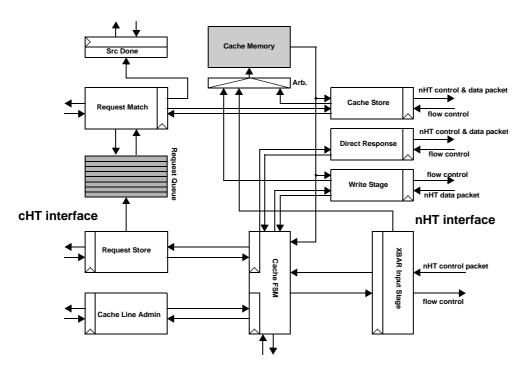

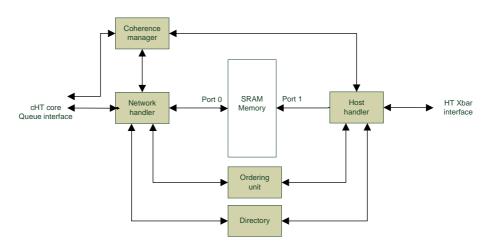

| 4.2.3 | cHT/nHT Bridge                | 119 |

111

II

| 4.2.4  | Cache Design                                                 |     |

|--------|--------------------------------------------------------------|-----|

| 4.2.5  | Transparent Memory Controller in the Device                  |     |

| 4.3 Su | ummary                                                       |     |

|        |                                                              |     |

| CHAP   | <b>FER 5</b> Suggestions for Direct Processor Cache Access   | 125 |

| 5.1 TI | he Design Space                                              |     |

| 5.1.1  | Device - Thread - Processor Relations                        |     |

| 5.2 D  | CA for HyperTransport                                        |     |

| 5.2.1  | Indirect Cache Access via Prefetch Hint                      |     |

| 5.2.2  | Direct Cache Access                                          | 131 |

| 5.3 Re | elated Work                                                  | 135 |

|        |                                                              |     |

| CHAP   | <b>FER 6</b> Reliability in a Direct Interconnection Network | 137 |

| 6.1 Fa | aults                                                        | 138 |

| 6.1.1  | Units                                                        |     |

| 6.1.2  | Soft Error Nature and Rates                                  |     |

| 6.1.3  | Error Correcting and Detecting Codes                         |     |

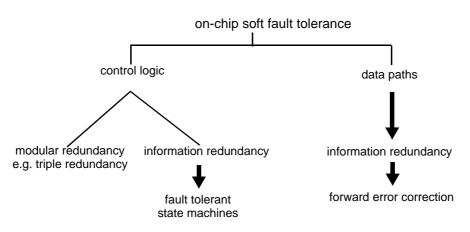

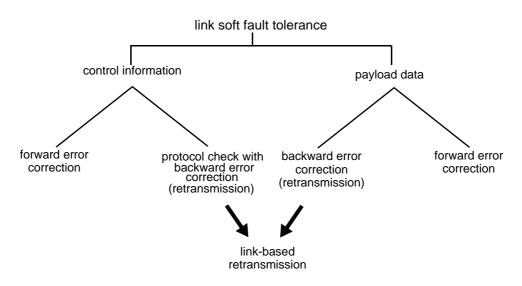

| 6.1.4  | SEU Tolerant Design                                          |     |

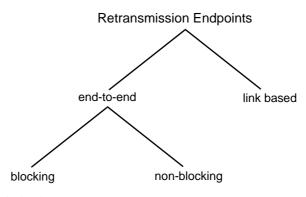

| 6.1.5  | Retransmission Endpoints                                     |     |

| 6.1.6  | Serial Transmission                                          |     |

| 6.1.7  | Faults in Regular Networks                                   |     |

|        | he Extoll Network                                            |     |

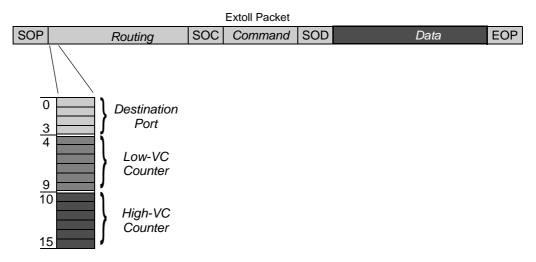

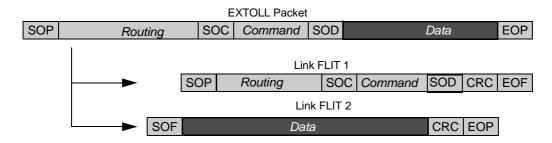

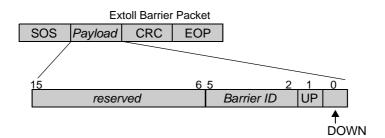

| 6.2.1  | Packet and Flit Protocol.                                    |     |

| 0.2.1  | xtoll Link Error Correction                                  |     |

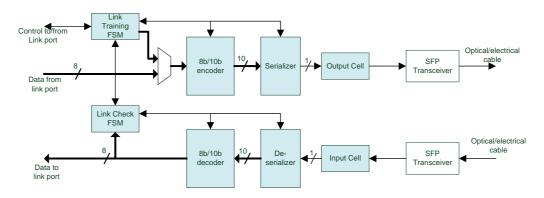

| 6.3.1  | The Physical Link                                            |     |

| 6.3.2  | Protocol Encoding for Serial Links                           |     |

| 6.3.3  | The Logical Link Layer: the Link Port                        |     |

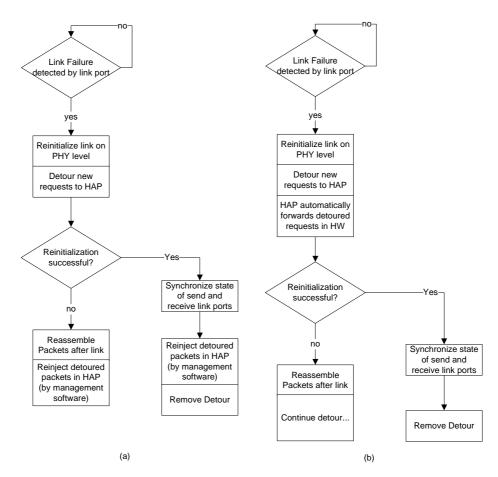

| 6.3.4  | Temporary or Permanent Link Failure                          |     |

| 6.3.5  | The Extoll Switch                                            |     |

| 6.3.6  | The High Availability Port                                   |     |

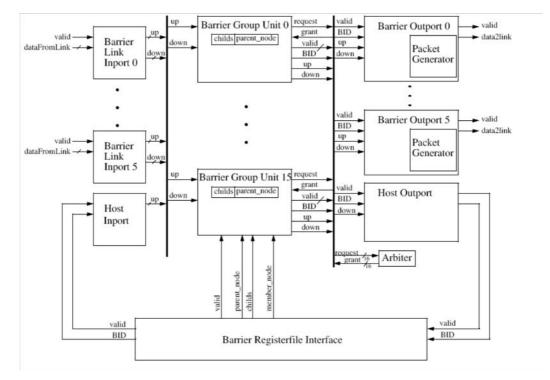

| 6.3.7  | Barrier                                                      |     |

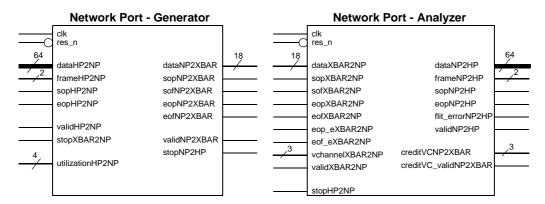

| 6.3.8  | The Network Port                                             |     |

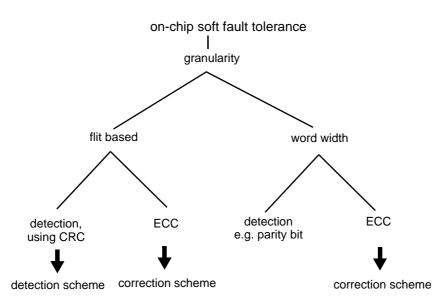

|        | n Chip Protection                                            |     |

|        | Immary                                                       |     |

| 0.5 50 |                                                              |     |

#### **CHAPTER 7** Conclusion

IV

| APPENDIX A Acronyms        | 185 |

|----------------------------|-----|

| APPENDIX B Bibliography    | 189 |

| APPENDIX C List of Figures | 205 |

# 1 Introduction

The demand for processing power is increasing steadily. In many application fields, there can never be enough computing power. Simulations in the field of engineering, like virtual crash tests, or in the field of bioinformatics, as protein folding, are examples for applications that require enormous computing power. But even consumer PCs continue to demand for more and more computing power.

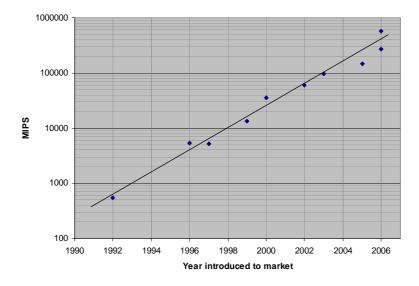

Moore's Law, predicting that the performance of microprocessors doubles about every 18 months, has proven to be true in the past, and will most likely stay true for the near future. One contributing factor to this performance increase are technological improvements. However, the direct influence of technology on computing performance is limited. Architectural improvements are another main source for sustained performance improvements.

In the past, single processor performance has been in the main focus for computer architecture. But even in this case, the exploitation of parallelism at instruction level is a key element.

As instruction level parallelism is limited in single processor applications, further performance increases can only be achieved by exploiting parallelism at the higher levels of thread or process parallelism. As a consequence, modern "processors" incorporate multiple processor cores that together form a single shared memory multiprocessor. While the architecture of the processor cores does not fundamentally differ from the architecture of single processors, architectural research must optimize communication among the processors.

In large parallel systems, which are typically message-passing multicomputers, a network interface controller connects the individual nodes to the network. Classically, the network interface controller is connected to its home node like every other input/output device over a hierarchy of peripheral interconnects. While this is an appropriate solution for slow devices like hard disks, it has become a significant bottleneck for network interface controllers (NIC) and coprocessor devices like field-programmable gate arrays (FPGA).

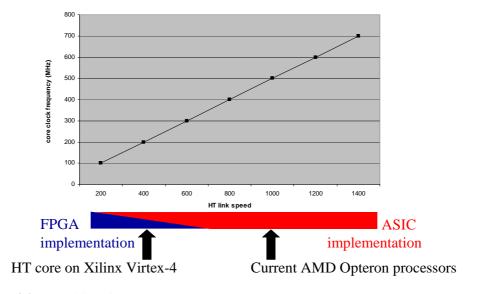

Thus, one target must be to couple coprocessors physically closer to main memory and to the processor of a computing node. This removes the overhead of today's peripheral interconnect structures. Such a step is the direct connection of HyperTransport (HT) devices to Opteron processors. The development of a HyperTransport intellectual property (IP) core and the integration into an FPGA coprocessor environment is part of this thesis.

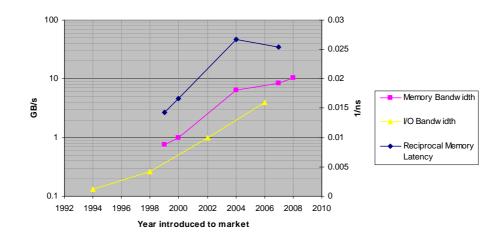

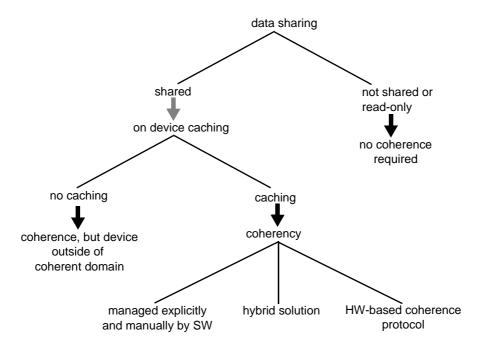

Additionally, the classical assumption that a computing node consists of a single processor with memory and I/O components is outdated. Multi-core processors have turned every computing node into a small-scale shared memory system. The trend towards higher parallelism is obvious: dual core processors are standard even for consumer PCs, and all major vendors are currently introducing four or eight core processors. Research prototypes of multi-socket systems feature up to 80 cores on a single die. Today's network interface architectures do not consider this fact sufficiently.

One area that is being investigated is the virtualization of network interfaces, which provides direct access from the user space to a device for multiple processes and threads at the same time. However, little research has been performed so far to analyze new mechanisms of low-level data transport between devices and processors in these systems. Almost all data transport in a shared memory system is controlled by the cache coherence protocol, which ensures that conflicts of parallel access to the same data objects are resolved. Cache coherence protocols thus determine how efficient and fast data transport in these systems is. Traditionally, NICs and coprocessors are connected to the system over noncoherent protocols, and thus are unaware of the coherence protocol. As a result, processors cannot hide latency by caching device memory that is accessed using programmed I/O (PIO). The second way of data transport from device to processor is direct memory access (DMA). Here, the device writes data into coherent main memory, which allows processors to cache this data. However, this path includes write and read accesses to DRAM, and thus exhibits a relatively high latency.

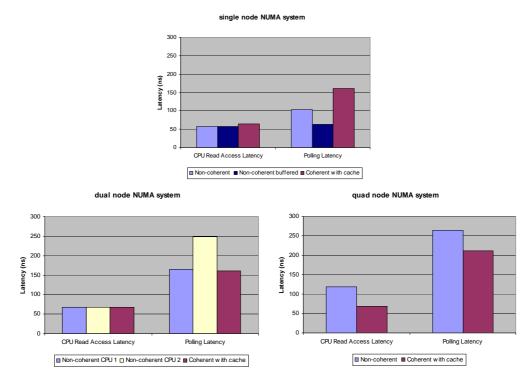

Thus, another target of this thesis is to analyze how this communication path can be improved to exhibit lower latencies. Two types of latency are relevant: a processor's read access latency to data that has previously been produced by the device affects the throughput of the processor. The other important latency is the overall latency of data transport from device to processor, which is important if the process is waiting for the respective data.

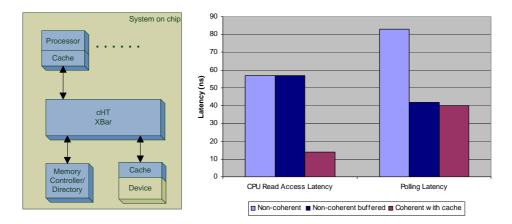

The analysis extends to classes of devices that take part in the cache coherence protocol. Among those are devices with coherent caches, and devices that provide a coherent memory view on device memory. Besides a potential increase in performance and efficiency, coprocessors may functionally benefit from coherent caches.

The growing demand for computing power and the exploitation of thread and process level parallelism does not only increase the size and complexity of single computing nodes. Net-

works of such nodes, mainly supporting message passing, are also increased in their size. The most prominent example is the IBM BlueGene system, featuring 106,496 computing nodes connected over a 3D torus direct interconnection network.

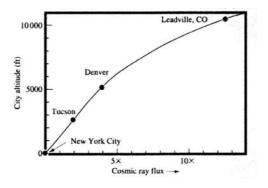

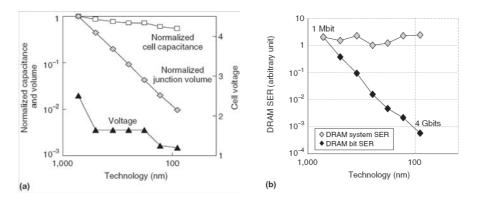

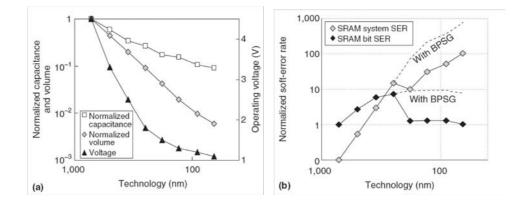

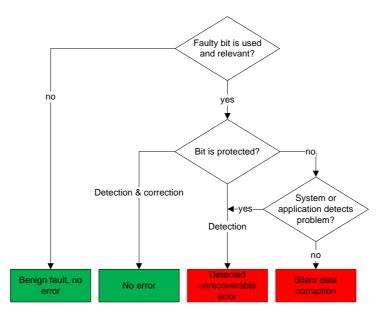

Such large networks are very susceptible to faults. Failures that occur in hardware can be classified into hard failures, where the hardware of a system is physically broken, and transient faults. In a transient fault, the information that is stored in a system is altered, for example due to radiation or Gaussian noise on a channel. Within the last years, transient bit faults have maintained an almost constant fault rate per bit that is stored in static random access memory (SRAM) or transmitted over cable. With an ever increasing complexity and size of computers, the likelihood of transient bit fault per system is increasing steadily. To keep the availability of parallel computers at a high level, error correction and fault-tolerance are becoming a more and more important issue. In the end, the error rate may rise at a level where high level error recovery becomes too costly if lower layers do not perform error correction that is transparent to the layers above.

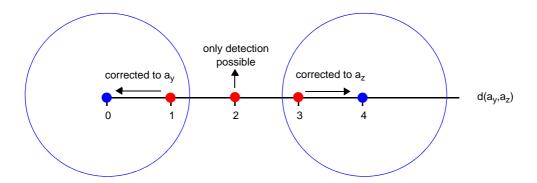

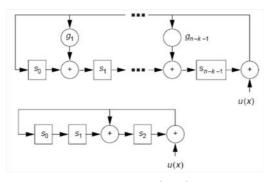

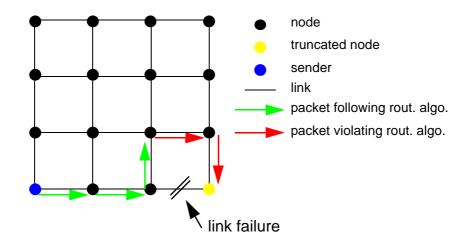

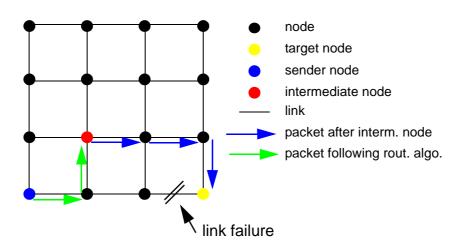

In any cable based network, link bit faults and complete link failures due to hard faults are the most frequent faults. In particular if direct-current-free (DC-free) high-speed serial transmission is used, coding for error correction and detection is difficult. A fault-tolerant network protocol is presented in this thesis. In contrast to state-of-the-art network protocols, errors are corrected directly by hardware on the link and network levels. On the link level, control information is protected using error correcting codes, while data is retransmitted in the case of errors. Besides the correction of erroneous bits and packets, another important topic in direct interconnection networks with a regular topology is that faulty links destroy the regularity of the topology. In this case, nodes become unreachable if deadlock-free routing mechanisms are used that have been optimized for the specific topology. A novel hardware based solution for intermediate routing is developed in this thesis, which allows an efficient, deadlock free routing around faulty links.

The result is a direct interconnection network that provides a reliable transport service even without the use of end-to-end protocols.

The outline of this thesis is as follows. Chapter 2 summarizes the state of the art in parallel computer architecture, and thus is the foundation for the subsequent chapters. Chapter 3 analyzes device to processor communication in HyperTransport based direct network NUMAs. Proposed improvements include devices that take part at the coherent HT protocol, and the completely new concept of a transfer cache. HyperTransport-based prototypes that realize the concepts are described in Chapter 4. A potential future improvement for device to processor communication are direct cache access mechanisms. An outlook on these is given in Chapter 5. With Chapter 6, the focus switches to the other side of the NIC:

the interconnection network. Transient faults that occur in such networks are analyzed, and a fault-tolerant network protocol for Extoll is described. Chapter 7 concludes this work.

#### **1.1 The Extoll Project**

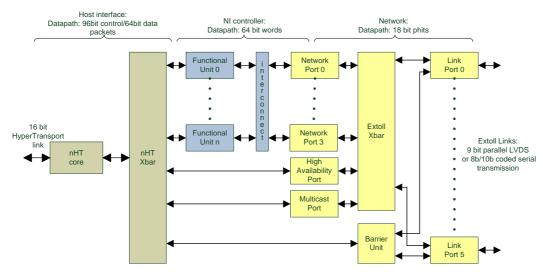

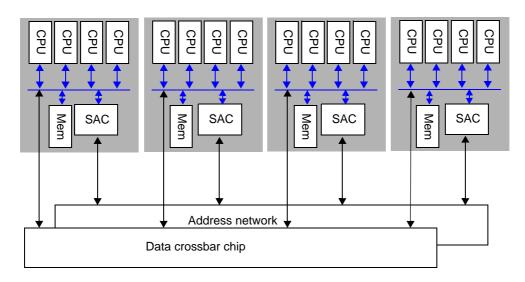

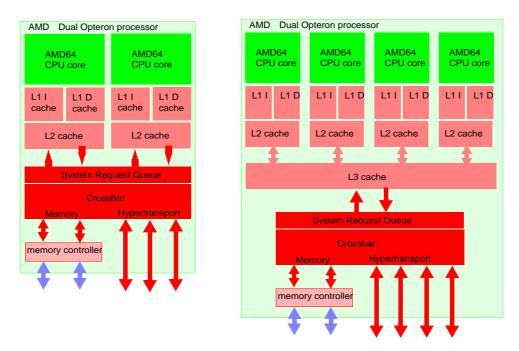

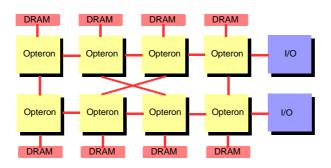

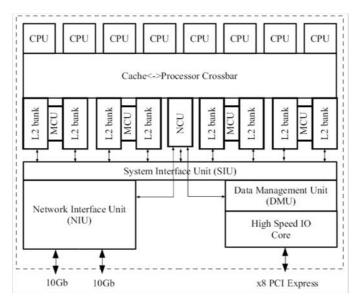

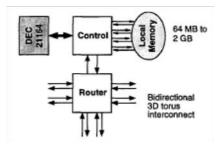

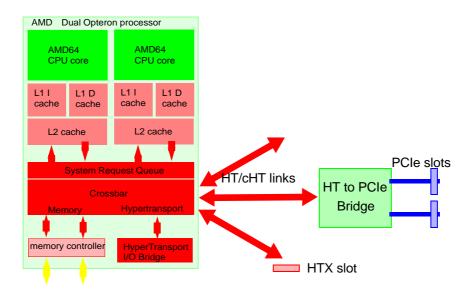

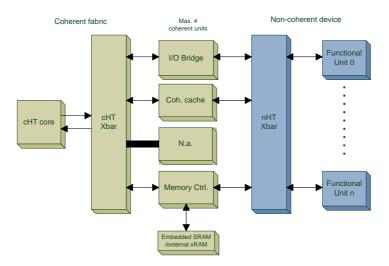

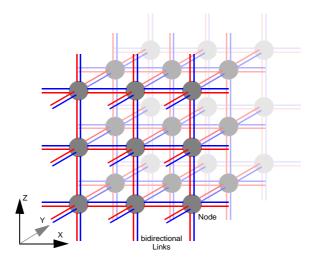

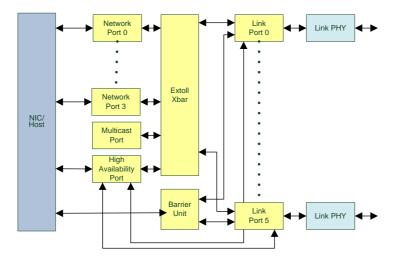

The Extoll project from the University of Mannheim combines different new methodologies in SAN communication into one network. Extoll is based on the Atoll network [26][27]. Just like Atoll, Extoll combines both the network interface and a part of the network into a single chip. Although centralized switch resources are supported, Extoll is designed as a direct network. Every NIC has a crossbar and 6 bidirectional network links, thus, a 3D torus topology is recommended for Extoll.

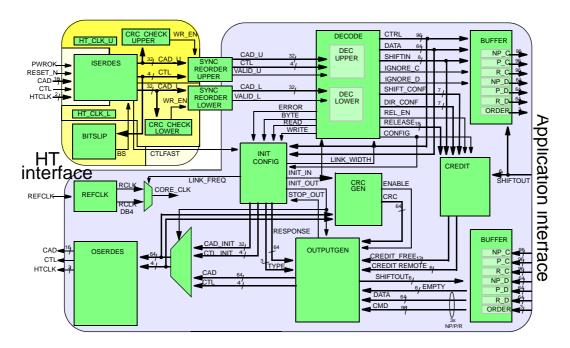

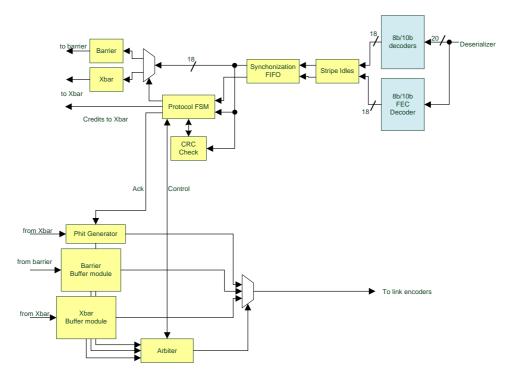

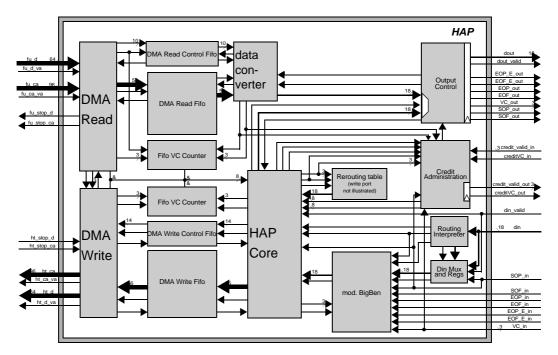

Figure 1-1. Block diagram of the Extoll NIC

The following aspects of Extoll are improvements to Atoll, and at the same time new contributions to the design of efficient SANs:

- Closer coupling of NIC, processors and memory. The design space analysis for such a closer coupling is performed in Chapter 3, the specification of the current implementation is described in Chapter 4.

- A virtualization of the NIC to allow direct user-level communication for a high number of processes or threads at the same time [121].

• Improved routing schemes in the network, including a mechanism for congestion avoidance [123].

Improved fault tolerance, including link-level error detection and retransmission of packets and link-level forward error correction of control flits. The High Availability Port (HAP) allows a rerouting of packets in the case of temporary or permanent hardware failures. The Extoll network itself, and in particular fault tolerance in the network, are described in Chapter 6.

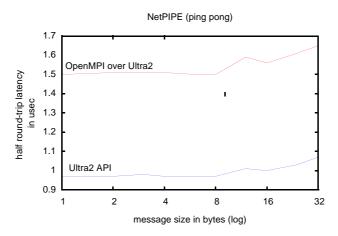

The actual network interface controller logic is implemented in a set of functional units (FU) that execute communication instructions. One communication paradigm in Extoll is message based communication with short messages that are smaller than one cacheline. This communication mechanism is implemented in the non-virtualized ULTRA functional units, which will be described later in more detail.

The other communication paradigm in Extoll is communication in a fully virtualized device. It allows a large number of processes and threads to access a device directly using user-level-communication. Here, send-receive and put/get communication is supported. A superscalar functional unit executes the communication instructions. Multiple such units may be used in implementations to parallelize work. It is still a topic of research how an I/O memory management unit (IOMMU) and translation lookaside buffers (TLB) are integrated into Extoll to allow an efficient translation of virtual into physical addresses. A context cache keeps the most recently used contexts for the processes, which are loaded into the FUs on a user process request.

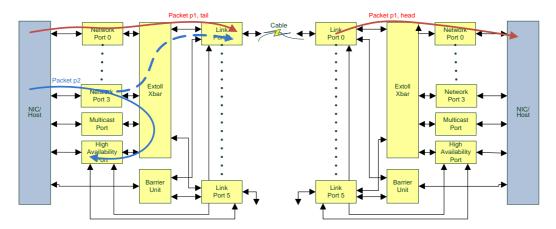

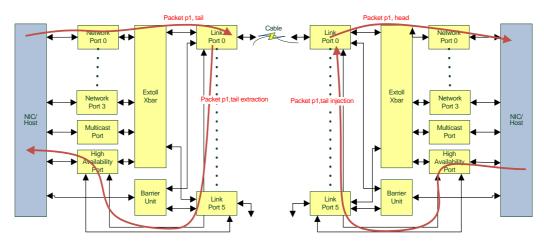

The right hand side of Figure 1-1 implements the Extoll interconnection network. The network port is the instance that translates packets into and from the network protocol format. Virtual channels and lanes are used to decrease the impact of head of line blocking and to avoid deadlocks in the system [123].

Extoll supports a direct interconnection network (IN) by integrating a crossbar-based switch for a 3D torus network. Such a direct IN provides distributed routing resources. This

means that the routing resources automatically scale with the number of nodes in the network. Between every two crossbars, a credit based flow control is used.

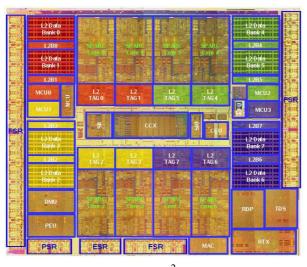

**Current Implementation**. The first offspring of the Extoll project is the design depicted in Figure 1-2. This is also the design which is used for the optimizations using a coherent protocol. With only two links, it looks more like a conventional NIC that requires centralized switching resources. The Ultra unit is the only functional unit. In ULTRA communication, a process sends a message by writing the message to the device using PIO writes. On the receive side, ULTRA writes messages into a user-space queue in main memory using a DMA write.

Figure 1-3. The HTX board

#### **1.2 Physical Implementation**

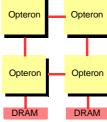

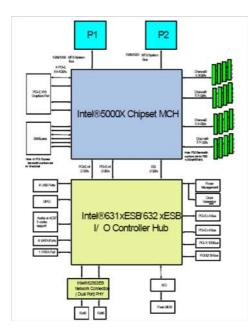

The hardware platform for the Extoll NIC prototype is the HTX board [128]. It contains an HyperTransport expansion (HTX) connector and a Virtex-4 FX FPGA which can be programmed via JTAG or USB. For communication, six small form factor pluggable (SFP) serial transceivers are on the board that are connected to the high-speed serial transceivers of the FPGA, featuring bit rates of up to 4 Gbit/s. Alternatively, the board can be equipped with two bidirectional parallel connectors. The HTX-Board can be plugged into any motherboard providing an HTX slot. The initial verification has been performed using the Iwill DK8-HTX motherboard, equipped with two AMD Opteron 246 processors.

#### **1.3 Graphical Representations**

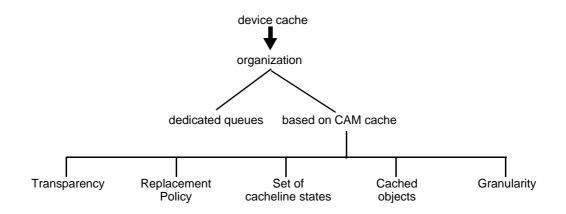

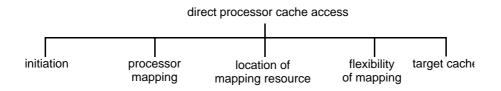

**Design space diagrams**. An important goal of this work is to analyze and explain design spaces and design choices. A graphical representation of different computer architectures is the design space diagram (see Figure 1-4), which has been introduced by Sima [4]. The diagram shows the different aspects in the design space, as well as the design choices for every such aspect.

Figure 1-4. Design space diagram

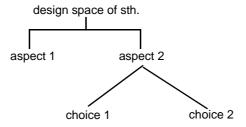

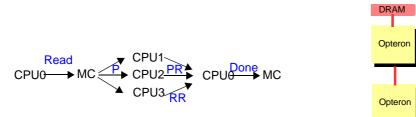

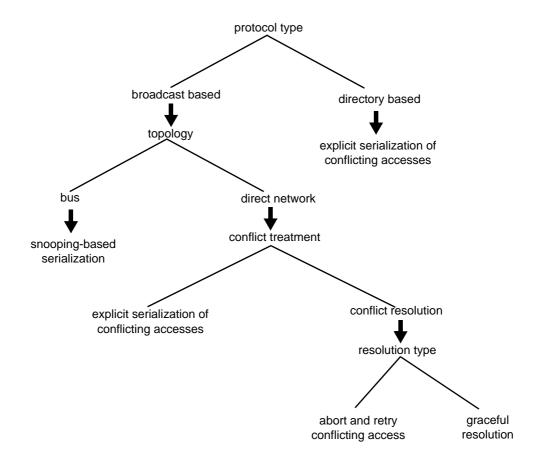

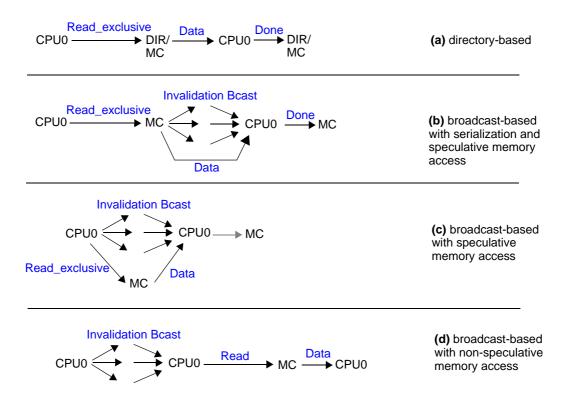

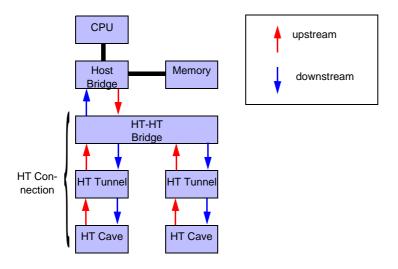

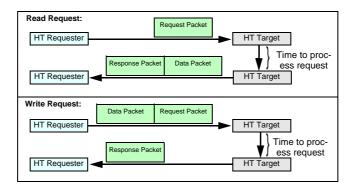

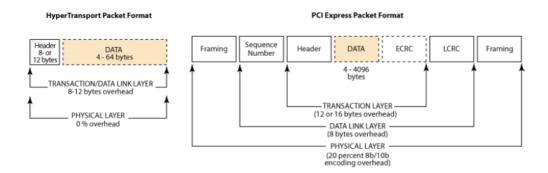

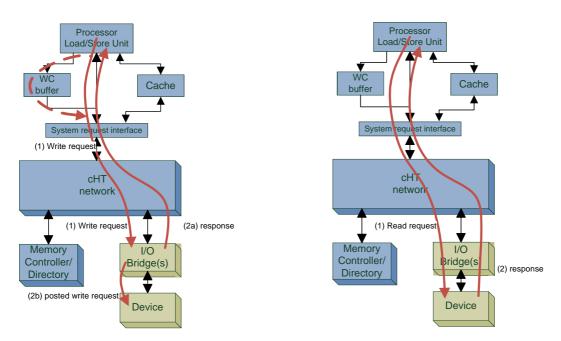

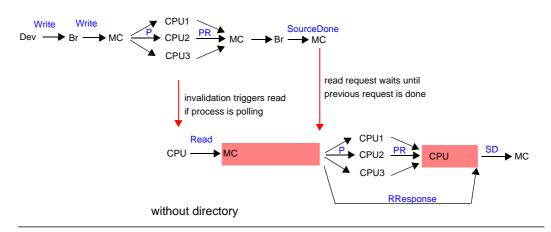

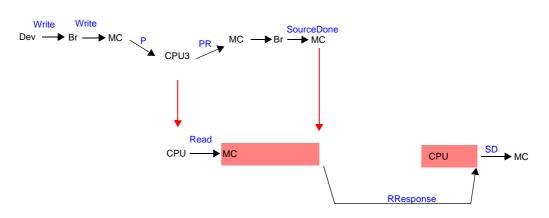

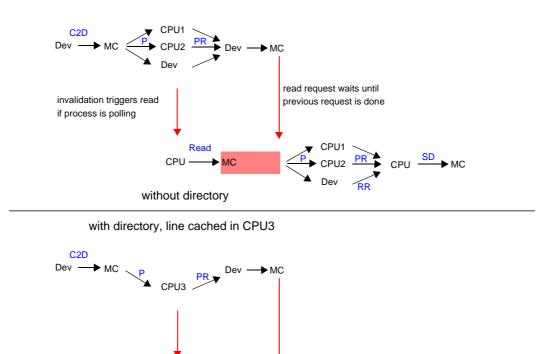

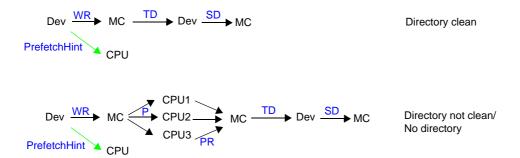

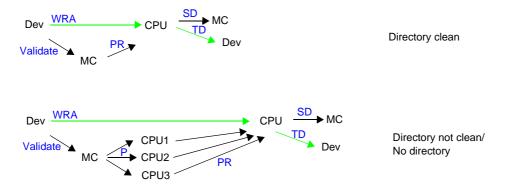

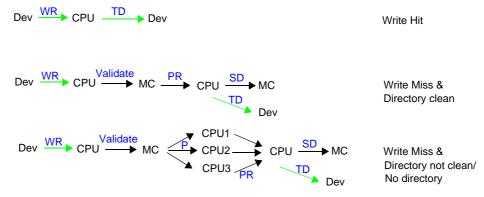

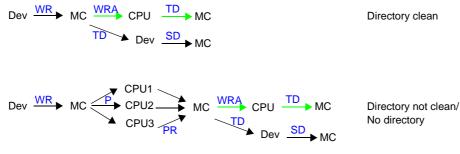

**Flow diagrams**. In modern NUMA architectures, nodes are interconnected through a packet-based direct network. Every transaction on the system consists of a sequence of packets that is exchanged between a number of master and slave devices. Flow diagrams are being used to visualize the path of packet flow, as shown in Figure 1-5. Most diagrams refer to the packet flow in Opteron based systems that are interconnected with a coherent HyperTransport fabric. As the coherent HyperTransport (cHT) protocol is confidential, flow diagrams are based on publicly available information only [108][44].

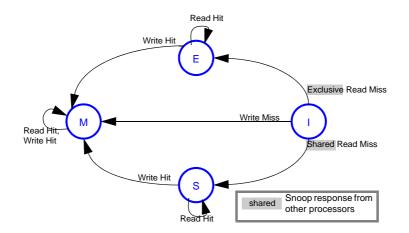

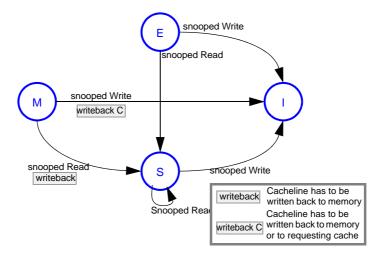

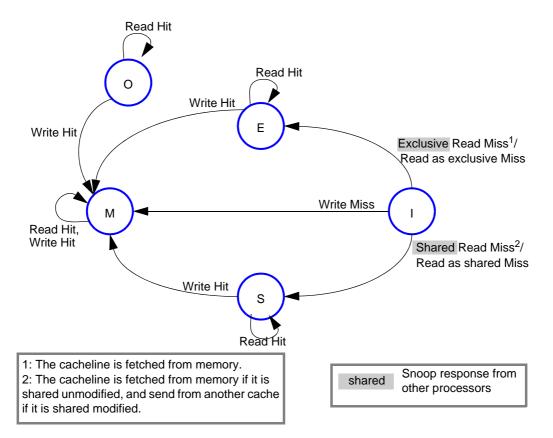

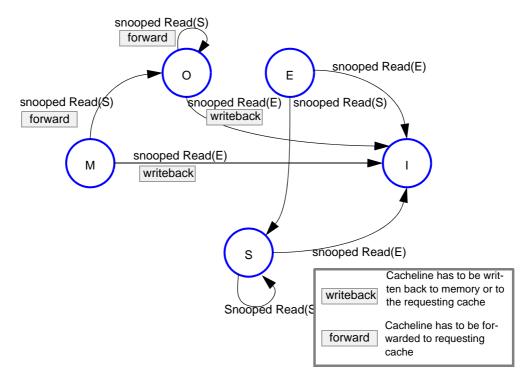

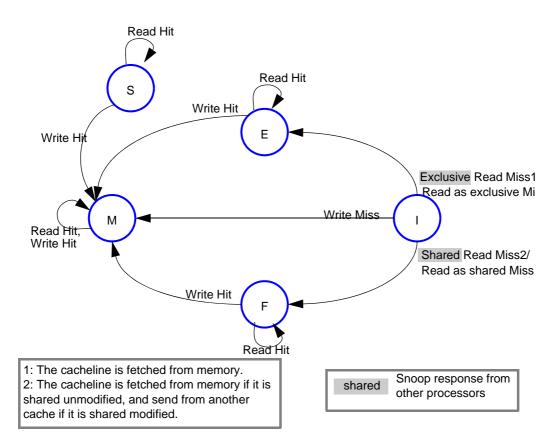

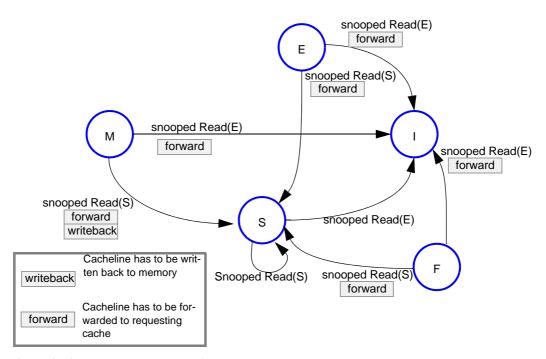

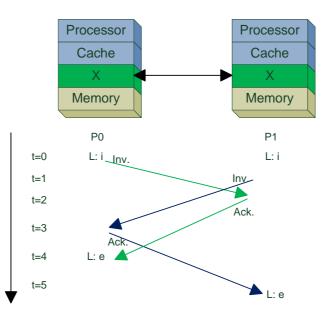

**Cache coherence state diagrams**. Cache coherence protocols can be seen as state machines. When describing them, there are two alternatives: in every protocol, every memory location is in a determined state. For example, the state may be invalid, that means not being cached at all. So, one way of describing the protocols is to describe how this global state of a memory location is affected by the cache actions.

The second way of describing the protocols is from the cache viewpoint: every cacheline entry in a cache is in a determined state too. The protocols can therefore be described by showing how these states are affected by the cache actions. State diagrams, as shown in Figure 1-6 and Figure 1-7, are a good way to describe these state transitions. Separate state diagrams are required for the caches that issued a request and those caches which are snooping the request. To be able to describe a protocol this way, by convention both a present

cacheline entry with the state invalid and a non-present cacheline entry will be called invalid.

Figure 1-5. Flow diagram

Figure 1-6. MESI state diagram for a requesting cache

Figure 1-7. MESI state diagram for a snooping cache

#### **1.4 Methodologies**

New designs or design variants of a device in a computer system must be evaluated for their benefits and in particular for their performance. As the performance of a device usually depends on the hardware and software of the whole system, this evaluation is a complex task. The methods for the exploration of a system are shown in Figure 1-8.

The idea for a specific design can be expanded to a **theoretical model**. In this model, the performance of the system's inherent mechanisms can be estimated. Usually, only worstor best-case estimations can be made in complex systems. A theoretical model cannot deliver good results for complex traffic patterns which influence transactions in the system in the form of background traffic. The theoretical model is based on assumptions about the behavior of system components. If these assumptions are right, a theoretical model can be efficiently used to estimate at least the order of magnitude of the performance of the choices in the design space.

An **architectural simulation** is an effort to increase the precision of performance estimates for a design. In the best case, the simulation is a cycle-accurate one-to-one image of the system, so that simulation results match results in the real system. At the same time, a simulation environment is usually being implemented faster than the real device or a prototype, and changes to the system as part of a design space exploration are possible with less effort. Nevertheless, architectural simulation is not free of problems:

• The only way to ensure the correctness of a simulator is to verify it against the real system - which is difficult if the system does not exist yet.

The implementation of a simulation framework is very time-consuming, with limited reuse potential for the actual system implementation. This may increase the time-to-market for a product significantly. Thus, simulators are often being reused to reduce this problem.

growing confidence

Besides these general problems, the computer architecture research community faces additional problems:

- Frequently used simulators like RSIM [16] simulate older architectures, it is thus not clear how mechanisms would behave in modern systems. As many of these simulators simulate processor instruction sets that aren't used any more, it is difficult to compile applications for use with the simulator. As a result, a small set of older benchmarks is being run on the simulators. Again, it is questionable whether this is good practice.

- Most scientific publications do not give many details about what functionality has been implemented in the simulator. Also, the source code is usually not contributed to the community. This prevents other researchers from verifying and comparing results.

- Also, publications frequently do not describe a feasible hardware implementation of

proposed new features. Thus, assumptions that have been made about the hardware

implementation cannot be verified. Also, it is not clear how feasible and expensive a

hardware implementation would be. Due to the intrinsic differences between software

and hardware design, computer architects with little knowledge and experience in hardware design are likely to make false assumptions in this field.

Although architectural simulations are a very powerful tool in general, these deficiencies reduce the significance of simulations as performed and presented in today's research com-

munity. Under these circumstances, it is not clear why most simulations that are performed are more accurate than a "order of magnitude" estimation made based on a good theoretical model. Although the experienced computer architect can avoid most of the above mentioned problems, the lack of an up-to-date simulation framework and a both critical and supportive community is a major problem.

A **prototype implementation** is the only bullet-proof exploration and verification technique. However, the development of the prototype is very expensive and time consuming. Thus, prototypes are not well suited for the exploration of a multitude of different design choices. If the prototype does not run at the same speed as the final product, for example because it is implemented in an FPGA, while the product is supposed to be an application specific integrated circuit (ASIC), performance of the final system must be extrapolated from the prototype performance.

Due to the problems of simulation frameworks described above, this thesis combines the usage of a theoretical model with prototype implementations. Assumptions about the performance of subcomponents are mostly based on implementations in the prototype system, and therefore ensure that the theoretical model can be safely applied for the comparison of design space alternatives. The following subsection details these system parameters.

#### **1.5 A Theoretical Model for cHT/HT Performance**

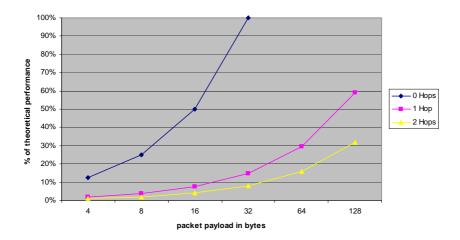

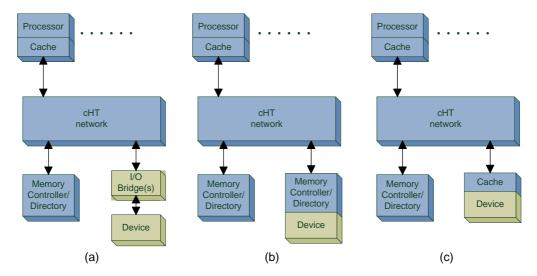

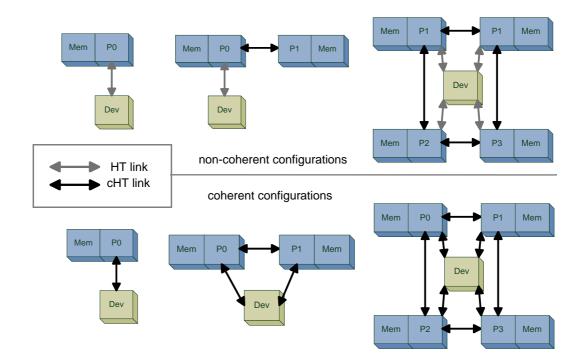

The in-depth analysis of efficient data transport from device to processor in Chapter 3 is performed for directly interconnected NUMA systems that are interconnected using the HyperTransport protocol. The model considers the influence of all components of the HT fabric, as well as attached memory and caches. The HT components are the switches, links, coherent caches, coherent memory controllers and I/O bridges as depicted in Figure 2-28 on page 57. Processor core internal paths are not considered.

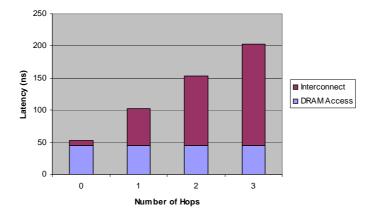

Actions that take place in these components have a certain latency, the relevant ones are depicted in Figure 1-10. Except for the memory access delay, all latencies depend on the clock frequency of the HT fabric, only the DRAM latency is fixed. The parameters in the table are given for HT1000 and are derived from the FPGA prototype implementations. Virtual-cut-through routing is being assumed in the cHT network.

Figure 1-9 shows an example calculation of a processor's coherent read access to memory that is homed on the same node, and no other cache holds the respective cacheline. The resulting value is best-case. In a real system, background traffic and congestion will negatively influence this latency.

DRAM

T

Т

Read to local memory with probe broadcasting:

$Latency_{Read} = t_{xbar} + max(t_m + t_{xbar}, t_{probeg} + 2(2t_{link} + 3t_{xbar}) + t_{pm} + t_{probec}) = 114ns$

Figure 1-9. Four-node example

| Name                      | Abbrev.             | Latency in ns |                                 |

|---------------------------|---------------------|---------------|---------------------------------|

| Memory Access Delay       | t <sub>m</sub>      | 45            | Read delay of memory controller |

|                           |                     |               | including DRAM latency          |

| Probe Hit Delay           | t <sub>ph</sub>     | 4             | Probe requests hits in probed   |

|                           |                     |               | cache. Cache must deliver data  |

| Probe Miss delay          | t <sub>pm</sub>     | 2             | Probe requests hits in probed   |

|                           |                     |               | cache. Probe response must be   |

|                           |                     |               | sent                            |

| Probe generate delay      | t <sub>probeg</sub> | 2             | Time to generate a probe        |

|                           |                     |               | broadcast or a directed probe   |

| Probe collect delay       | t <sub>probec</sub> | 2             | Time to process responses after |

|                           |                     |               | last response has been received |

| Response processing delay | t <sub>rpr</sub>    | 4             | Time to process a read          |

|                           |                     |               | response containing data        |

| Link delay                | t <sub>link</sub>   | 21            | One-way latency of HT links     |

| Xbar delay                | t <sub>xbar</sub>   | 4             | Delay of HT Switch              |

| Bridge delay              | t <sub>br</sub>     | 4             | Delay of cHT/HT bridge          |

Figure 1-10. System parameters for HT1000

## 2 Communication in Parallel Computers

This chapter summarizes the state of the art in parallel computer architecture, and thus is the foundation for the subsequent chapters.

After a short overview about caches in Section 2.1, an introduction to parallel computers is given in Section 2.2, including an overview about the communication patterns in parallel systems. Section 2.3 analyses the design space of network interface (NI) locations within a node. This work concentrates on a realization of tightly-coupled NIs and devices under consideration of the cache coherence protocols in shared memory nodes. Therefore, Section 2.4 discusses cache coherence protocols in depth.

The prevalent type of computing nodes are based on the x86 architecture, which is mainly due to the good price to performance ratio of these off-the-shelf systems. Section 2.5 introduces such server systems. Section 2.6 gives an overview of parallel systems that have been implemented in order to illustrate of the most important mechanisms in parallel architectures.

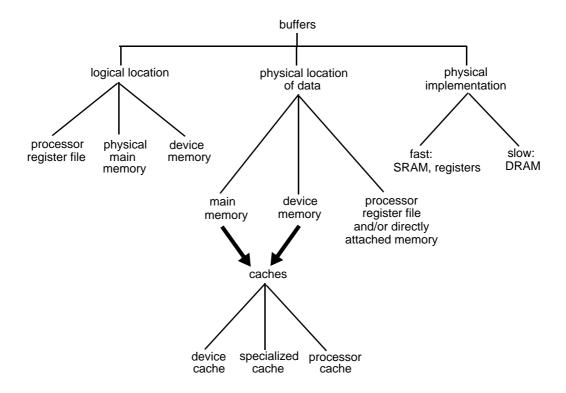

#### 2.1 Caches

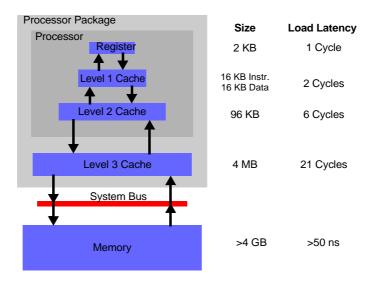

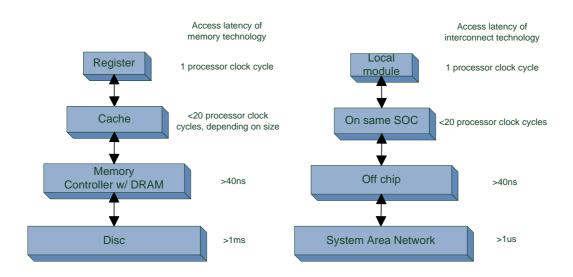

The memory hierarchy in a single processor system consists of the register file at the top of the hierarchy, followed by a number of levels of caches. At the bottom of the hierarchy, there is the main memory. This hierarchy is depicted in Figure 2-1. As can be seen from the figure, speed and size of a memory component are contrary to each other: large memory components are generally slower than smaller ones. Thus, the only reason to use caches is to hide the latency and bandwidth restrictions of main memory accesses.

The terminology used in this thesis is as follows: Every location in a cache can hold a datum called *cache block*. Usually, such a cache block consists of multiple data words. Many current processors have a cache block size of 64 bytes. The term *cacheline* is frequently used as a synonym for cache block. It is not only used for the cache block located in the cache, but also when such a datum is transferred in the system.

Figure 2-1. The memory hierarchy of the Intel Itanium processor [5]

The second component belonging to a cacheline is the control field. It holds information about the current state of the cacheline, for example its cache coherence protocol state (see Chapter 4.3). The union of cacheline, tag and control field is called *cache entry*.

A cacheline is indexed by a part of the address. The higher part of the address, which is not used for indexing, has to be saved in a tag field with the cacheline, so that cachelines can be uniquely identified. The group of cache blocks that can be accesses with the same index is called a *set*. If the number of cache blocks in a set is 1, the cache is called a *direct mapping cache*. If all cache blocks are in one single set, the cache is called *fully associative cache*. In all other cases, the cache is called an *n-way set-associative cache*, where n specifies the number of cache blocks per set.

#### **2.2 Parallel Computing Architectures**

The interface between every shared memory node and the rest of the system is called the network interface controller (NIC). The communication patterns for which a NIC should be optimized strongly depend of the architecture of the parallel computer. This chapter will thus briefly describe the different types of parallel computer architectures, thereafter, the communication paradigms of the most common systems are described.

**Flynn's taxonomy** [3] distinguishes computer architectures by looking at the parallelism in the data and instruction streams. Four classes exist: Single Instruction - Single Data (SISD), Single Instruction - Multiple Data (SIMD), Multiple Instruction - Single Data (MISD) and Multiple Instruction - Multiple Data (MIMD). Although this classification scheme is still in use, it has some major weaknesses: The class of MISD systems has never really been populated. The original proposal of the sequential von Neumann computer [1] [2] is a typical SISD system. Due to the trend towards multi-core processors and simultaneous multi threading, the class of SISD systems is emptying.

Arrays of processing elements are a typical example for SIMD architectures. Most present parallel systems are MIMD computers. An MIMD computer usually consists of a number of processing units working independently of each other, each with its own instruction and data stream. MIMD architectures are more versatile than SIMD architectures, since they are not reduced to one single stream of instructions. Therefore, MIMD architectures can generally exploit more parallelism. MIMD architectures can be differentiated into shared memory and message passing architectures. This distinction is based on the hardware mechanisms of communication. It does not specify the communication paradigm that is used by user applications, as this may be different than the mechanism that is used in hardware.

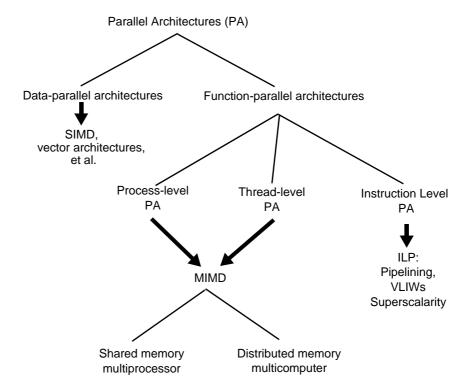

**Sima's taxonomy** [4] classifies parallel architectures into data parallel architectures and function-parallel architectures. Data parallel architectures are vector, associate and neural, SIMD and systolic processors. Functional-parallel architectures can be distinguished based on the level of parallelization. Instruction-level parallelism (ILP) can be exploited within every single processor by means of pipelining, superscalar designs or very-long-instruction-word (VLIW) processors. According to Sima, the process-level and thread-level parallel architectures combined form the same class as MIMD.

**Shared Memory Architectures**. In a shared-memory architecture, every processor is connected to every memory via the system interconnect. Although the physical memory modules may be distributed throughout the system, they form one global memory space which can be addressed by all processors.

Figure 2-2. Classification of parallel architectures according to Sima

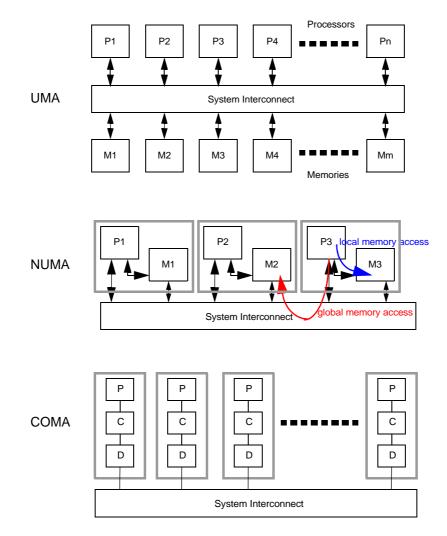

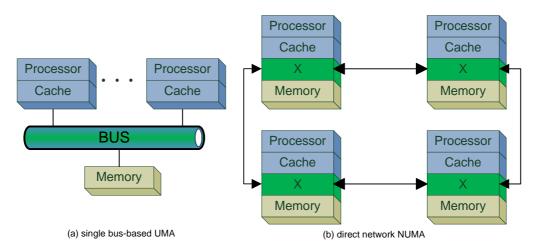

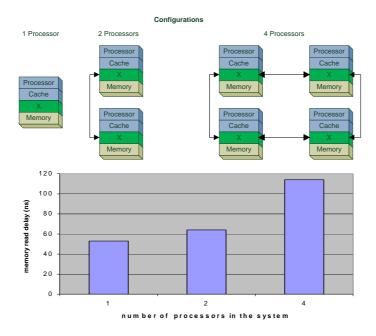

A closer evaluation of shared memory systems reveals different access models: the uniform memory access model (UMA), the non-uniform memory access model (NUMA), and the cache-only memory access model (COMA), as shown in Figure 2-3.

UMA architectures consist of n processors and m physical memories. Processors are interconnected with all memories so that processors can access all memories in the very same way. In particular, access latencies and bandwidths are the same for every processormemory path. The scalability of this topology is limited: with a growing number of processors and memories, the complexity of the interconnect is increasing as well. Thus, larger systems will exhibit higher memory access latencies.

In NUMA architectures, physical memory is assigned to every processor, which this processor can access directly without having to use the global system interconnect. To access any other memory, the system interconnect has to be used. Thus, accesses to the local memory will typically exhibit a lower latency than global accesses. Also, the bandwidth to the local memory may be higher.

Figure 2-3. UMA, NUMA and COMA architectures

The motivation for NUMA systems is that in most parallel applications, the largest part of the accessed memory is privately used by one thread, only a part of the memory is really shared among threads. If the operating system in a NUMA machine allocates the memory of a process or thread on the same processor as the process or thread is running on, most memory accesses of the processes or threads should target the local memory. As a result, NUMA systems are much better scalable. Firstly, a larger system interconnect affects only a part of all memory accesses. The latency and bandwidth of local memory accesses is independent of the system size. Secondly, the load on the system interconnect is much lower.

The third category of shared memory systems are COMA architectures, in which all memories are converted to caches. A memory word in a cache-only architecture does not have a permanent home address in one of the memories. Instead, it can be in any of the caches at any time. Particularly, it can be in more than one cache at a time. Processors have direct access only to the local caches. The access on memory words residing in a remote cache is performed implicitly by the cache-coherence mechanism.

Another criterion for shared memory system is the one of symmetry. In a symmetric multiprocessor (SMP), all processors do have the same capabilities including I/O access and running the operating system. In asymmetric multiprocessing, processors are designated to special purposes: Master processors are able to execute the operating system and to perform I/O. Slave processors cannot perform I/O access, but only execute code under supervision of the master processors.

Often, shared memory systems use a hierarchy of interconnects, and may use different coherence mechanisms at the different interconnect levels. The NUMA implementations ExtendiScale [108], AzuzA [98] or Dash [97] show that significantly more has to be done at the interface between nodes and the network than just routing. Optimizations include for example remote caching, address remapping and probe filtering. Thus, such a system will comprise a shared memory network interface controller (SM-NIC). The fundamental difference between NIC and SM-NIC is that a NIC has to be addressed explicitly, while communication over the SM-NIC happens implicitly based on the address of requests.

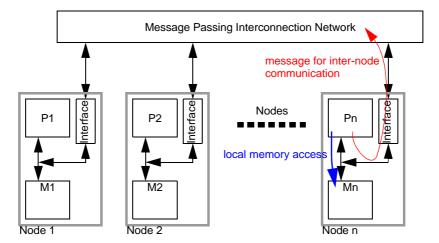

**Distributed Memory Architectures**. The architecture of a distributed-memory system is depicted in Figure 2-4. In this type of system, memory is not globally shared. Instead, the system consists of so called nodes, which consist at least of one processor, local memory and an interface to the interconnection network. For inter-node communication, messages are passed between the nodes. The nodes of such a system are computers acting autonomously. Therefore, these systems are also called multicomputers.

Today, most large parallel systems are distributed memory architectures. However, the nodes typically consist of small UMA or NUMA shared memory multiprocessor systems. Cluster computers that are constructed using off-the-shelf AMD or Intel processors (see Section 2.5) and SAN interconnection networks (see Section 2.6.5) are typical examples for this type of system. In these systems, any communication with other nodes requires explicit communication with the NIC.

Figure 2-4. Distributed memory architecture

A NIC is required due to the fundamental differences between intra-node and inter-node interconnects. A node can be integrated in a small physical space, i.e. on board level. Communication paths on chip are in the range of micrometers, off-chip in the range of centimeters. In contrast, the interconnect between the nodes has to connect nodes that may be meters apart from each other, connected by cables instead of traces on a printed circuit board (PCB). Particular problems are:

- The high latency of the transmission over longer distances requires sophisticated flowcontrol mechanisms over every single cable.

- Bandwidth in the interconnect is limited, due to the high costs of adding bandwidth compared to on-chip or on-board interconnects. Thus, congestion and the need for node-to-node flow control are a serious issue.

- A significant bit error rate requires such errors to be corrected, using retransmissions or forward error correction. Also, a large network must cope with the failure of components, as cables and nodes.

Thus, the separation into a node with network interface controller, and the interconnection network between the nodes is very useful.

#### 2.2.1 Communication Paradigms

A different point of view on this problem simply distinguishes communication primitives that may be present in such a system, which are:

- · Remote memory access using remote load/store operations,

- Message passing using a send-receive semantic,

- Remote memory access (RMA) using a put/get semantic.

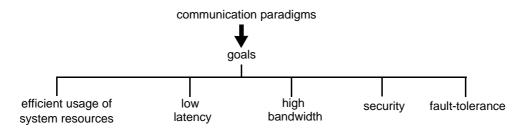

Figure 2-5. Goals of all communication paradigms

Remote loads and stores and the RMA mechanism are both one-sided communication mechanisms. This means that only one process is actively participating in the communication. Thus, this kind of requests always involves access to remote memory: communicating processes are coupled by using shared memory. In contrast, message passing using a send-receive semantic is a two-sided communication mechanism, as both communication processes are involved. A system may support both message passing and shared memory mechanisms at the same time.

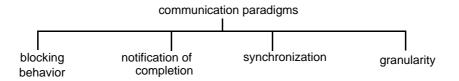

Figure 2-6. Aspects of communication paradigms

Figure 2-5 shows the general goals of all communication paradigms. It depends on the application rather than on the specific paradigm how these goals are weighted. The para-

digms differ in the aspects shown in Figure 2-6. The next three sections will analyze the paradigms with regard to these aspects.

#### 2.2.2 Remote Load/Store

The remote load/store mechanism is the type of communication that is used in shared memory systems. It is based on load and store instructions of the processor instruction set. Typically, there is no differentiation between remote and local instructions, so that they are treated the same way as every other load instruction.

A processor's load instruction classically loads one value from memory into one register, a store instruction stores the content of one register to memory. Thus, load and store instructions work on one single processor-native data object that typically has a size of 32 or 64 bits. Vector instructions may work on larger data types. However, current implementations in processors as the different types of SSE [23] or AltiVec [24] support only up to 128bit loads and stores. If such an instruction misses in a cache, the cache will create a read or write request with the size of a cacheline in this cache to the next level in the memory hierarchy.

A remote read/write may thus use the cacheline size of the last cache hierarchy, or a multiple of it. The largest unit of data transport is used for virtual shared memory (VSM) systems. These are message-passing based distributed memory systems that emulate remote loads and stores in software. Due to the high overhead for remote memory accesses in these systems, the granularity of remote accesses is typically one page [25].

Remote loads and stores are blocking operations. A load that has been issued blocks until the response data arrives. In particular, a thread or process cannot be retired. However, the processor may execute other instructions if they do not have data dependencies with the stalled load, and if this does not violate memory ordering constraints.

Similarly, a store may block other memory requests. Most memory consistency models employ strict ordering among stores.

Shared memory programming models as OpenMP [75] may allow a differentiation of remote and local memory. Thus a compiler can optimize parallel code by inserting early prefetch instructions for remote memory loads. A manual optimization by the programmer would also build up on prefetch instructions. A prefetch instruction is basically a hint to load a specified memory block into the cache in a non-blocking way. However, finding the right point in time for a prefetch is difficult. If a prefetch is started too early, a succeeding write to the address by another processor will lead to an invalidation of the cache entry that has been allocated by the prefetch, which results in the same situation is if no prefetch had been executed. In the worst case, a prefetch is executed at the same time while another pro-

cess is writing to the same memory location. In this case, the write is delayed, as the prefetch of the cacheline cancels the writer's write permission to the cacheline temporarily.

The notification of completion happens implicitly, due to the blocking behavior of loads and stores.

In a shared memory system, the cache coherence protocol makes changes to shared data visible to the whole system immediately. Thus, a certain grade of synchronization is already performed by the underlying hardware. However, many applications require mutual exclusions to access critical sections of the parallel application.

A non-coherent implementation of remote loads/and stores is possible as well. In this case, changes become only visible if they are written back using a remote store, and cached copies are invalidated. An application of this scheme are systems with a very relaxed ordering scheme, as for example transactional memories [8].

#### 2.2.3 Put/Get

Communication using put and get operations is often called remote memory access (RMA) communication. In analogy to the remote load operation, a get request is used to access remote memory. However, there is a number of fundamental differences to the load operation:

The most fundamental difference is that put and get operations do not operate on processor registers, but on main memory or a dedicated set of registers that is not part of the processor register set. For example, implementations of MPI [73] and the Extoll put/get unit use main memory. The T3E (see Section 2.6.2) uses a set of memory-mapped device registers.

Put and get can be implemented as non-blocking operations. The request for a get starts the operation that is performed asynchronously to the process. Before the process can access data that has been transferred using a get, it has to check for completion of the operation. The third and last difference is that the put/get semantic does not support an automatic hardware coherence. Instead, this must explicitly be managed by the application.

The notification of completion may occur in three different ways, depending on the implementation. One possibility is a blocking put/get operation, which only returns if the operation completed. A second possibility is a nonblocking get, where read accesses to the local get destination are blocked until data is available. Such a mechanism is implemented in the T3E (see Section 2.6.2). The third and most popular solution is a test for completion that is performed by the user process. An MPI implementation will typically be based on notifications of completion, which are inserted by the device into a notification queue that resides in main memory. The process then has to check this queue to retrieve the status of the operation. For a get operation, a notification is generated if all data has been written to the requestor's destination. For a put operation, there are two points in time at which a notification may be generated. A first notification may be generated if all user memory that relates to a specific put operation can safely be reused by the requester. The second notification is generated if the put operation completed at the target, so that it is globally visible.

The synchronization in the RMA scheme can be done using mutual exclusions. MPI, for example, uses the notion of memory windows. A window is a part of the address space that is accessible via puts and gets by remote processes. These windows can be locked explicitly for mutually exclusive access. Another method of synchronization is the use of epochs. An epoch is framed by a barrier at the beginning of the epoch and a barrier when the epoch ends. A process enters a barrier operation only if all puts and gets it has issued in the previous epoch, i.e. since the last barrier, have finished. So, puts and gets from different epochs cannot collide.

#### 2.2.4 Send-Receive

In the send-receive scheme, a processes explicitly send messages to other processes. The target process can obtain the message data by an explicit receive operation. Thus, send-receive is a two-sided communication mechanism. Besides the two sided scheme, message passing communication may also support n-sided communication using broadcast, multicast and other collective operations. The send-receive paradigm offers a wide variety of operations that differ in their behavior. User-level libraries as MPI offer the whole variety of function calls to the user.

The standard send and receive functions are blocking. The send function returns if the message has been successfully send from the sending processes perspective. This means, that the user can safely reuse buffer space that contains the message data. It does not mean that the message has arrived on the remote node. A receive function returns after the message has been received. Nonblocking send and receive functions may return immediately, the user application has to explicitly check if the operation succeeded before accessing the respective data. Another type of send is the synchronous send. This function only returns if the receive operation for that message has been called.

The underlying hardware does not have to directly implement all these sending mechanisms, instead they can be emulated. A nonblocking send function can be implemented in the message passing library using a blocking send hardware mechanism: first, all message related user data is copied into a buffer. Then, a separate thread performs the actual blocking send operation. Synchronous sends are usually implemented using a rendezvous protocol. The sender first sends a request to the receiver, when the receiver calls the corresponding receive operation, it sends back an acknowledgement. Only after this acknowledgement has been received, the sender may start sending the actual message.

In order to uniquely identify messages, they carry a user-application tag and information to distinguish processes.

Efficient implementations of the send-receive make use of nonblocking send-receives, as this allows the overlapping of communication and synchronization. Also, blocking sends and receives are prone to race conditions that may lead to deadlocks. Thus, in the general case, the NIC has to generate a notification that is checked explicitly by the user application. As the synchronization is explicitly performed by the send and receive operations, no other mechanisms are used to synchronize bidirectional communication. For global synchronization, barriers may be used.

#### **2.3 Device Integration Design Space**

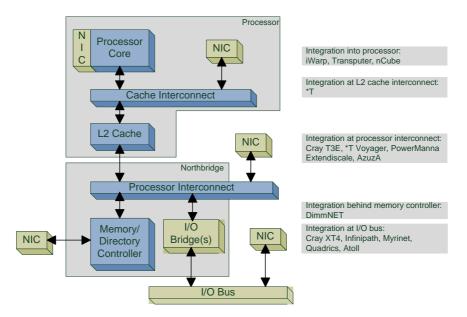

This chapter analyzes at which locations in a node a NIC or SM-NIC may be located. The overview presented in Figure 2-7 makes use of the same scheme that originally has been introduced by Bruening [28].

The closest coupling can be reached if the NIC is integrated into the processor core. Examples for such implementations are the iWarp [11] and Transputer [12] computers, as well as a suggestion by Henry & Joerg [83]. Communication in these systems is performed by writing to or reading from a special set of registers. In these implementations, the register set is connected to the network over a FIFO queue. A general problem with these approaches occurs if packets arrive that are destined to a process other than the one that is currently loaded in the processor. Gang scheduling together with draining the network on every process switch is used in most such closely coupled systems to resolve this problem. Henry & Joerg suggest to interrupt the currently active process and to schedule the process that is the destination for the packet. Also close to the processor core are NICs that are attached to the cache interconnect, as the \*T [94] for example.

While such a close coupling of computation and communication may be desirable, it is very difficult to propose realistic implementations. The cache interconnect and the processor core of commercial processors are usually neither physically or legally accessible. They are within the processor chip, confidential, proprietary, not compatible with other processors and also may change frequently.

The coherent processor interconnect is the typical network interface location for shared memory systems that have a global memory address space. Supercomputers in the early and mid nineties were frequently of that type [99]. One major vendor of this type of systems has

25

been Sun Microsystems, an overview of their system architectures is given in [15]. Another prime example of shared memory systems is the Dash architecture [97], a more recent example is the Horus chip of the Extendiscale architecture [108]. \*T-Voyager acts like a snooping processor at the processor interconnect to allow coherent shared memory communication between nodes.

This processor interconnect is also the closest location to the processor that is physically accessible, as it is designed to support inter-chip communication. It is also less confidential. Some message passing NICs, as in the PowerManna [76] or in the T3E were attached to this interconnect as well. They implement the functionality of I/O devices.

Figure 2-7. Device integration design space

The I/O bus is the standard interface for devices, including NICs and accelerators. I/O buses like PCI Express are standardized, and available on different platforms. Thus, there are numerous examples for such systems, as the Cray XT3 and XT4. Also, I/O buses allow the development of NICs that may be used in all host systems that support the I/O bus. Examples for such NICs are Atoll, Infinipath, Myrinet and Quadrics.

The MEMOnet NIC architecture [77] is one of the few examples for a memory controllerattached NIC. This architecture shall leverage the fact that a processor can access memory with higher bandwidth and lower latency than a device connected over a PCI bus. The MEMOnet NIC is implemented on a DIMM. Besides the NIC itself, SDRAM memory is also included on the DIMM.

The sending of a message to the NIC makes use of the PIO mechanism: A send memory region maps to the DIMM module. The processor writes message header and data to this region. Thus, as for any PIO operation, the memory region must be uncacheable so that writes are directly written to the memory controller and thus to the memory module.

A serious problem of this architecture is the passive nature of memory modules. The NIC cannot issue interrupts. The receive process can only work as follows: Messages that have been received are written to the SDRAM that is embedded on the memory module. A process can then access the received data just as it would for a classical memory-mapped PIO device.

**Analysis in this work**. Due to the low feasibility of processor integrated NICs, this work focuses on NIC implementations on the I/O bus and the processor interconnect. Also, it focuses on the integration into a node that is a small-scale shared memory system. This is due to the fact that such systems just recently started to prevail on the market, as technological and architectural solutions to increase the performance of single processor cores have been exploited. Section 2.4 will describe shared memory systems in detail, as this is the basis to analyze integrations of devices in such systems.

#### **2.3.1 Process-Device Interaction**

Most of today's architectures know two different basic types of memory: main (physical) memory and I/O memory.

Traditionally, I/O space can be accessed by device drivers and the operating system, leveraging the PCI software model. This model is used by virtually all of today's devices, as in PCI-X, PCI-Express (PCIe), HT2 and HT3 devices. In the user space communication scheme, I/O space is mapped into the virtual memory space of applications. This avoids operating systems calls and memory copy operations between user and operating system memory spaces.

Process-device interaction can be differentiated into synchronization and data communication. There exists a very typical basic scheme of communication between process and device. To submit a job to a device, the process inserts a job descriptor into a dedicated queue. This queue is necessary to decouple the operation of processor and device. The job descriptor may contain all data that is required for the device to process the job. It may also be the case that the job descriptor contains direct or implicit pointers to additional data required for the job. In any case, this is a classical producer-consumer situation. Synchronization in this process is necessary to determine the fill level of the queue. Communication in the other direction, i.e. from device to process, works the very same way. This path may be used for example to submit the result of a job that has been previously issued to the device. In a network interface device, data that has been received from the network is forwarded this way.

For data communication in today's x86 systems, there exist two mechanisms, which both include the required synchronization:

**Programmed Input/Output (PIO)**. In this communication pattern, data is moved between applications and devices by explicitly performing processor memory operations. Before moving data to a device, the processor has to check whether the device is capable to hold the data. If there is enough free space, data is written by I/O writes into the address space of the device. Address bits of the device address space may be used to submit additional control information to the device. For example, one bit of the address might be used to mark the end of a data packet. Data transfer in the other direction is performed in a similar fashion. First, the process checks for new data by performing I/O reads to a status register. If this is successful, the processor can issue subsequent I/O reads to read the data from the device. This interface is called register-mapped interface.

**Direct Memory Access (DMA)**. Data is not copied by the processor, but by a DMA engine that is external to the processor. Usually, the DMA engine is part of the device. For processor to device communication, a job descriptor that specifies source and target of the copy operation must be set up by the processor. Then the processor triggers the DMA engine, which is typically done using an I/O memory access to a register of the DMA engine. A typical location for the job descriptors is a queue in main memory. For data transport in the other direction, the device performs the DMA and creates a notification that is also in main memory. The processor uses PIO accesses to check for new entries in the queue. This interface is a descriptor-based interface.

It can be noted that both communication methods currently rely on PIO concerning the synchronization of data transport. In essence, there are three basic types of data movement used:

- Synchronization using I/O read and write accesses from processor to device

- PIO data transport between processor and device

- DMA data transport between device and memory

A fourth possibility is not used in the classical approach, but will be introduced in the following sections:

• Synchronization over memory

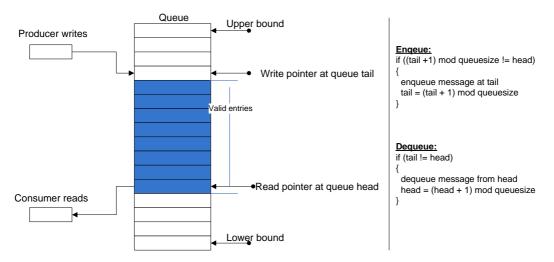

**Queue Organization**. In order to decouple the producer and the consumer of data, buffers are required. The hardware representation is a first-in-first-out (FIFO) buffer. This structure cannot be implemented efficiently in software, where data always resides in main memory. Therefore, pointer-based wrap-around queues as shown in Figure 2-8 are used.

Figure 2-8. Pointer-based wrap-around queue

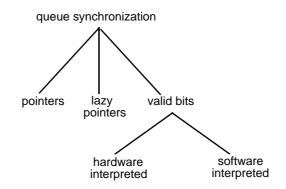

The basic pointer scheme has the disadvantage that pointers have to be exchanged between consumer and producer for every access to the queue. Queue pointers are usually communicated using memory operations to memory-mapped I/O space of the device.

Improvements to the scheme are depicted in Figure 2-9. Lazy pointers improve the enqueue operation: for an enqueue, it is sufficient to know that enough free space is in the queue. It is not necessary to know the amount of free space precisely. Thus the producer has a copy of the read pointer that is potentially stale. This copy has to be updated only if the free space in the queue is under a certain threshold. For the write pointer, the lazy pointer does not work. Not updating the write pointer means that the consumer is not notified of new entries in the queue, which results in a higher latency.

Another improvement are valid bits that are embedded in every queue entry. The softwarebased approach, which is implemented in the \*T-ng [95] for example, embeds valid bits in the data object that represents a queue entry, i.e. the valid bits are part of the queue payload. Thus, the processor can read a queue entry speculatively, and determine whether the entry is valid or not. In one scheme, a bit with the value '0' means invalid, '1' valid. The producer sets this bit to '1' in every entry it enqueues, the consumer has to reset this bit to '0' after it has consumed the entry. In this scheme, the consumer does not need to observe the write pointer at all. The drawback of this approach is that the consumer has to write to the queue entry, causing additional memory traffic. Sense reverse avoids this problem by changing the meaning of the sense reverse bit for every pass through the queue, so that the bits in the entries do not have to be changed.

A general drawback of software-based valid bits is that they consume entry payload. This may not be a major problem if the queue entries are control information, but it may be a severe limitation if queue entries contain payload data.

Hardware-interpreted valid bits have been implemented for example in the Cray T3E (see Section 2.6.2 on page 60). The advantage of hardware-interpreted bits is that they allow advanced notification mechanisms, as explained in the next paragraphs. Also, they do not reduce the payload that can be used by software.

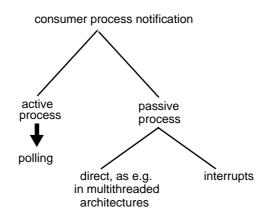

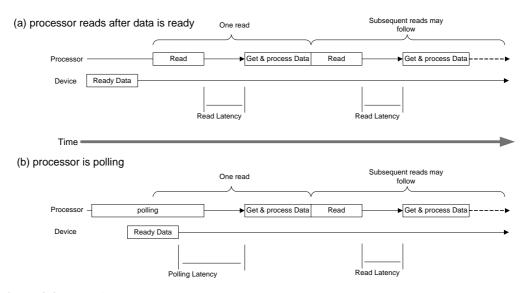

Figure 2-9. Queue synchronization design space

**Process Notification** (see Figure 2-10). A process has to be notified that a queue entry has been added by a device, and thus should check queue pointers or valid bits. Most devices use interrupts for signaling to the processor. However, today's interrupt mechanisms only signal that something happened, they do not carry any information about what happened in a device. Interrupts are signaled to a processor, which usually calls the interrupt handler of the operating system or the device driver. Thus, interrupt signaling involves a much higher latency than polling mechanisms and is less useful for tightly coupled coprocessors.

In the polling scheme, a process is continuously reading on a synchronizing data structure, as a queue pointer for example, to detect a change. The downside of this method is that the process occupies processor resources, and may cause traffic on the path between processor and device. Another option is to suspend the execution of the thread until a change

occurred. In the Cray T3E, a load to a memory location whose hardware valid bit is '0' stalls, thus stalling the process. However, the processor is blocked by the process. SMT processors as the Sun T2 (see Section 2.6.1) or HEP [32] avoid this blocking, as the processor resources are still available for the other threads running on the processor.

Figure 2-10. Consumer process notification design space

The ATOLL NIC [26] [29] introduced a mechanism to mirror device registers into main memory, so that a process can access those instead of the real device registers. Coherence is maintained by updating the main memory image, called replicator page, periodically. The main advantage of this method is that a polling process will only access the cache instead of continuously generating I/O traffic. A very crucial issue is the update frequency. A low frequency increases the latency until a process gets hold of a value change of a device register. A high frequency in the best case has the same latency as a PIO access, but will generate unnecessary bus traffic.

# 2.3.2 Device Virtualization

Virtualized devices allow user-space access to the device for multiple processes at the same time. Three major challenges have to be solved:

- How is the context of a process, i.e. status registers and queues handled, and where is the home of these data structures?

- How can requests from processes be controlled so that they do not overflow the device?

- How can the device reliably protect processes from each other?

If a virtualized device supports a large number of contexts, the corresponding data structures cannot efficiently be held on the device. A solution to this is to make main memory to the home of all context information. The device caches these contexts.

At the same time, it must be ensured that device buffers do not overflow with requests from different processes. To allow processes to determine whether they can submit a request to the device, an submission of such a request must be an atomic operation as read-modify-write. Many systems do not support these operations on the I/O bus. A conditional store buffer [124][120] is an alternative to implement an atomic access to buffers on a virtualized device. Information about the request is encoded in the address bits of a read request to device I/O space. The device answers with a read response, which contains information whether the request insertion into the buffer was successful or not.

Figure 2-11. Address decoding for a read request to a conditional store buffer in Extoll [121]

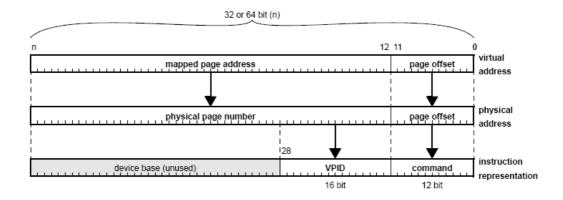

The requesting process can be identified if a process or context ID is encoded in the read request as well. Processes are protected from each other if only that memory-mapped I/O space is mapped into process memory that corresponds to the assigned process ID. An example for such an encoding is the one used in Extoll, as shown in Figure 2-11. It uses 16 bit of the address to decode the virtual process identifier (VPID), and additional 12 bit to decode the command which should be enqueued.

A more detailed description of these problems and possible solutions in the context of Extoll is given in [121].

# 2.4 Cache Coherence for Shared Memory Systems

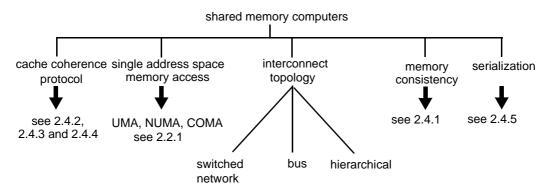

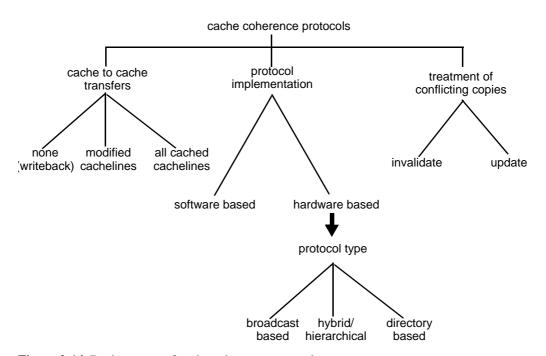

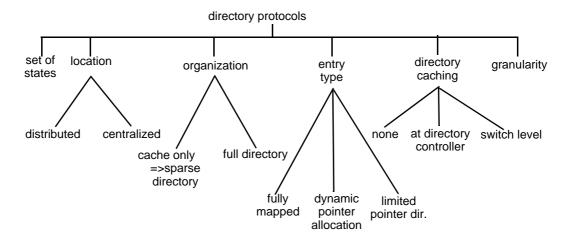

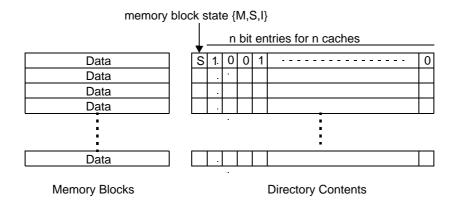

The most important aspect of shared memory systems is the single address space view. A differentiation of the memory access models UMA, NUMA and COMA has already been performed in Section 2.2.1. Other important aspects, shown in Figure 2-12, will be described in the following sections.

Figure 2-12. Design space of shared memory computers

A key point is the memory consistency model of a system. The memory consistency model defines how operations on memory that are performed by one processor in a shared memory system affect the memory as seen by the other processors in the system. The consistency model requires some form of serialization of simultaneous memory requests to the same address.

Processors in shared memory systems usually have private caches. If a processor modifies a cached line, a mechanism is required that keeps these caches coherent. These aspects will be analyzed in detail in the next sections.

Another important criterion is the topology of the interconnect between processor caches and memory. In principle, any type of interconnection network may be used. Bus-based interconnection networks have been very common in the past. Very small scale system may use a single bus as interconnect, while larger systems may use multiple parallel or hierarchical buses, as for example in the NEC AzuzA [98] and Sun's XDBus architecture [14]. Broadcast-based cache coherence protocols can be implemented on buses easily. However, both broadcast protocols as well as busses generally do not scale well. In contrast, the scalability of switched interconnection networks is much better. Today, there is a clear trend towards direct networks of NUMA nodes, as depicted in Figure 2-13. Hierarchical combinations of different interconnection networks are possible as well. For example, the Dash [97] shared memory computer connects clusters of 4 processors with a bus, while the clusters are interconnected using a 2D torus direct network.

Figure 2-13. Common topologies for small scale shared memory computers

### 2.4.1 Consistency Models for Shared Memory

In order to develop parallel applications for shared memory systems, programmers need a solid idea of how memory behaves with respect to reads and writes to memory addresses. The *memory consistency model* of a system is the set of rules that a system employs on memory accesses.

Strict consistency is the most stringent model of memory consistency. It requires that every read or write must be globally visible before any other read or write can be issued. Thus, it imposes a static ordering of memory accesses of all processors. Such a system would not require any other mechanism for synchronization, as it is synchronous by compile time. However, is not applicable to multiprocessor systems at all, as they gain from issuing and executing operations independently of each other.

A realistic model of consistency in multiprocessor systems is the model of sequential consistency. The original definition from Lamport [55] is: "A system is sequentially consistent if the result of any execution is the same if any operations of all the processors were executed in some sequential order, and the operations of each individual processor appear in this sequence in the order specified by its program." A more handy definition has been derived by [56]: "A system is sequentially coherent if the following conditions are true:

(A) All processors issue memory accesses in program order.