# The ATLAS ROBIN – A High-Performance Data-Acquisition Module

Inauguraldissertation zur Erlangung des akademischen Grades eines Doktors der Naturwissenschaften der Universität Mannheim

Vorgelegt von

Dipl. Ing. (FH) Andreas Kugel aus Lindau

Mannheim, Juni 2009

Dekan: Prof. Dr. Felix Freiling, Universität Mannheim Referent: Prof. Dr. Reinhard Männer, Universität Mannheim Korreferent: Prof. Dr. Peter Fischer, Universität Mannheim

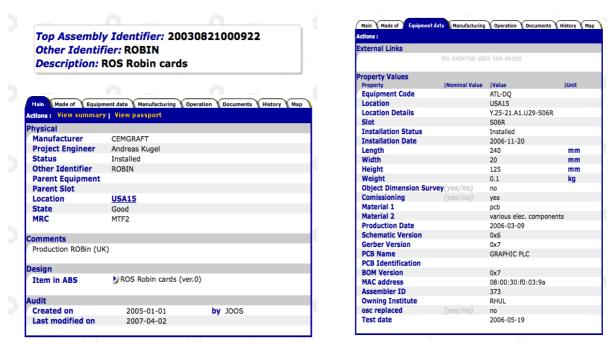

Tag der mündlichen Prüfung: 19. August 2009

# The ATLAS ROBIN - A High-Performance Data-Acquisition Module

#### **Abstract**

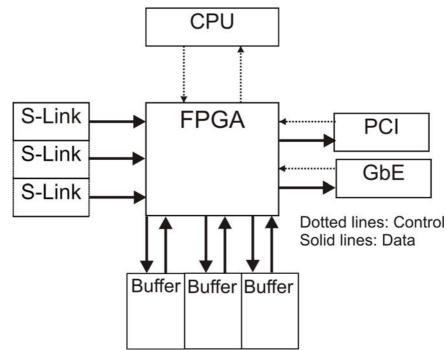

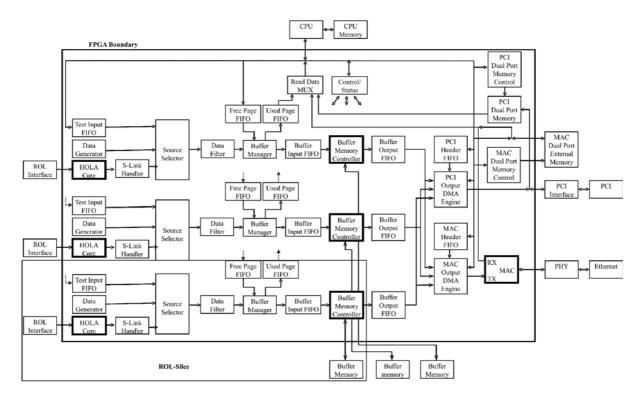

This work presents the re-configurable processor ROBIN, which is a key element of the data-acquisition-system of the ATLAS experiment, located at the new LHC at CERN. The ATLAS detector provides data over 1600 channels simultaneously towards the DAQ system. The ATLAS dataflow model follows the "PULL" strategy in contrast to the commonly used "PUSH" strategy. The data volume transported is reduced by a factor of 10, however the data must be temporarily stored at the entry to the DAQ system. The input layer consists of approx. 160 ROS read-out units comprising 1 PC and 4 ROBIN modules. Each ROBIN device acquires detector data via 3 input channels and performs local buffering. Board control is done via a 64-bit PCI interface. Event selection and data transmission runs via PCI in the baseline bus-based ROS. Alternatively, a local GE interface can take over part or all of the data traffic in the switch-based ROS, in order to reduce the load on the host PC. The performance of the ROBIN module stems from the close cooperation of a fast embedded processor with a complex FPGA. The efficient task-distribution lets the processor handle all complex management functionality, programmed in "C" while all movement of data is performed by the FPGA via multiple, concurrently operating DMA engines.

The ROBIN-project was carried-out by and international team and comprises the design specification, the development of the ROBIN hardware, firmware (VHDL and C-Code), host-code (C++), prototyping, volume production and installation of 700 boards. The project was led by the author of this thesis. The hardware platform is an evolution of a FPGA processor previously designed by the author. He has contributed elementary concepts of the communication mechanisms and the "C"-coded embedded application software. He also organised and supervised the prototype and series productions including the various design reports and presentations.

The results show that the ROBIN-module is able to meet its ambitious requirements of 100kHz incoming fragment rate per channel with a concurrent outgoing fragment rate of 21kHz per channel. At the system level, each ROS unit (12 channels) operates at the same rates, however for a subset of the channels only. The ATLAS DAQ system – with 640 ROBIN modules installed – has performed a successful data-taking phase at the start-up of the LHC in September.

# Der ATLAS ROBIN – Eine Hochleistungs-Datenerfassungsbaugruppe

# Zusammenfassung

Diese Arbeit beschreibt den re-konfigurierbaren Prozessor ROBIN, der ein Schlüsselelement im Datenerfassungssystem des ATLAS-Experiments des LHC am CERN ist. Der ATLAS Detektor liefert Daten über 1600 Kanäle gleichzeitig an das DAQ System. Im Gegensatz zur üblichen "PUSH" Strategie für den Datentransport kommt bei ATLAS eine "PULL" Strategie zur Anwendung, wodurch das zu transportierende Datenvolumen um den Faktor 10 reduziert wird. Dazu müssen die Daten am Eingang des DAQ System zwischengespeichert werden. Die Eingangsstufe nimmt die Daten in 160 ROS Ausleseeinheiten entgegen, die jeweils aus 1 PC mit 4 ROBIN Karten bestehen, jede ROBIN Karte ist wiederum mit 3 Detektorkanälen verbunden. Die Daten werden auf den ROBINs gespeichert. Die Überwachung der Baugruppe geschieht vom PC aus über ein 64-bit PCI Interface. In der Busbasierten Basisimplementierung des ROS erfolgt die Auswahl und Übertragung der Daten ebenfalls über das PCI Interface. Eine lokale Gigabit-Ethernet Schnittstelle übernimmt in der alternativen Netzwerk-basierten Implementierung einen Teil oder den gesamten Datenverkehr, um den PC zu entlasten. Die hohe Leistungsfähigkeit und Flexibilität des ROBIN ergibt sich aus der Kombination eines schnellen eingebetteten Prozessors mit einem hoch integrierten FPGA. In einer effektiven Aufgabenverteilung bearbeitet der Prozessor alle komplexen Verwaltungsaufgaben, die in "C" programmiert sind, während das FPGA sämtliche Datenbewegungen mit mehreren, gleichzeitig arbeitenden DMA Einheiten durchführt.

Das ROBIN Projekt wurde von einem internationalen Team durchgeführt. Es umfasst die Spezifikation des Designs, die Entwicklung der Hardware und der Firmware (VHDL und C) der ROBIN Baugruppe, PC-Software (in C++) für Ansteuerung, Emulation und Test, Produktion und Test von Prototypen sowie die Serienfertigung und Inbetriebnahme von 700 Baugruppen.

Das Projekt wurde unter Leitung des Autors dieser Arbeit durchgeführt. Die Hardwareplattform ist eine Weiterentwicklung eines vom Autor entworfenen FPGA Prozessors. Grundlegende Konzepte der Kommunikationsmechanismen stammen vom Autor, ebenso die "C"-Anwendungssoftware. Ebenfalls wurde die Herstellung der Prototypen und die Serienfertigung inklusive der notwendigen Statusberichte vom Autor vorbereitet und überwacht bzw. durchgeführt.

Die Ergebnisse zeigen, das die ROBIN Baugruppe die hohen Leistungsanforderungen von 100kHz Ereignisrate am Eingang bei gleichzeitig 21kHz Abfragerate – jeweils auf allen 3 Kanälen gleichzeitig – erfüllt. Auf Systemebene liegt der Arbeitspunkte für jede normale ROS-Einheit mit 12 Kanälen bei 100kHz Eingangsrate und 21kHz Abfragerate, jedoch nur für einen Teil der Kanäle. Das ATLAS DAQ System mit 640 installierten ROBIN Baugruppen hat den Datenerfassungsbetrieb zum Start des LHC erfolgreich aufgenommen.

| The ATLAS ROBIN – A High-Performance Data-Acquisition Module |  |

|--------------------------------------------------------------|--|

|                                                              |  |

|                                                              |  |

# **Contents**

| 1 Introduction.                     |    |

|-------------------------------------|----|

| 2 Data Acquisition Systems.         | 11 |

| 2.1 LHC Experiments                 | 11 |

| 2.1.1 CMS                           | 13 |

| 2.1.2 ALICE                         | 17 |

| 2.2 LHCb                            |    |

| 2.3 Summary                         |    |

| 3 ATLAS DAQ.                        |    |

| 3.1 System View.                    |    |

| 3.2 Dataflow                        |    |

| 3.3 ROS                             |    |

| 3.3.1 Event handling.               |    |

| 3.3.2 Configuration and monitoring. |    |

| 3.3.3 Baseline bus-based ROS.       | 32 |

| 3.3.4 Switch-based ROS.             |    |

| 3.4 Summary                         |    |

| 4 FPGA Technology                   |    |

| 4.1 Device types                    |    |

| 4.1 Device types                    |    |

|                                     |    |

| 4.3 Tools                           |    |

| 4.3.1 Specification.                |    |

| 4.3.2 Simulation and test           |    |

| 4.3.3 Synthesis.                    |    |

| 4.3.4 Vendor specific tools         |    |

| 4.4 IP-Cores.                       |    |

| 4.4.1 Embedded processors.          |    |

| 4.4.2 Ethernet MAC.                 |    |

| 4.5 Summary                         |    |

| 5 ROBIN                             |    |

| 5.1 Requirements                    |    |

| 5.2 Project Management.             |    |

| 5.3 Implementation.                 |    |

| 5.3.1 Hardware                      |    |

| 5.3.2 VHDL Firmware                 |    |

| 5.3.3 Software                      |    |

| 5.4 Installation and commissioning  | 89 |

| 5.5 Summary                         | 90 |

| 6 Results                           | 93 |

| 6.1 Stand-alone                     | 93 |

| 6.1.1 PCI access                    | 94 |

| 6.1.2 Network access.               | 96 |

| 6.1.3 Event bookkeeping             | 97 |

| 6.2 System performance              |    |

| 6.2.1 Bus-based ROS.                |    |

| 6.2.2 ATLAS Dataflow.               |    |

| 6.3 Issues.                         |    |

| 6.4 Reliability                     |    |

| 6.5 Summary.                        |    |

| 7 Discussion and Conclusions.       |    |

| 7.1 Performance Assessment.         |    |

| 7.2 Prospects                         | 108 |

|---------------------------------------|-----|

| 7.2.1 Short term developments         |     |

| 7.2.2 Upgrade Phase-1                 |     |

| 7.2.3 Upgrade Phase-2                 |     |

| 7.3 Summary                           |     |

| 8 Appendix                            |     |

| 8.1 Pre-ROBIN hardware                |     |

| 8.1.1 MPRACE-1                        |     |

| 8.1.2 μEnable                         | 112 |

| 8.2 ROBIN configuration parameter set |     |

| 8.3 ROBIN statistic                   | 114 |

| 8.4 ATLAS detector parameters         | 116 |

| 8.5 Glossary                          |     |

| List of figures.                      |     |

| List of tables.                       |     |

| Bibliography                          | 123 |

| BibliographyAcknowledgements          | 129 |

|                                       |     |

#### 1 Introduction

The research objective of Particle Physics is the structure of matter. According to the Standard Model [SMS1][SMS2][DISSFLICK] there are 12 particles which form matter and 4 force carrier particles which describe the interaction between the matter particles. Matter particles are distinguished in quarks and leptons and further into 3 generations. Each generation is composed from a pair of each type of particles. Only the 4 particles of the first generation – the electron with its neutrino and the up and down quarks – build the matter we are aware of. The interactions between particles are called forces and are bound to the the exchange of force coupling particles, the bosons. Two of the forces – gravity and electromagnetism – are quite commonly known. The two others – the weak and the strong force – are related to interactions between and inside nuclear particles, like protons, neutrons and quarks. The strong, weak and electromagnetic force cover a relative strength range of about 1:100, but the strength of the gravity is 43 orders of magnitude smaller than the strength of the strong force. This is the reason why gravity is ignored by many of the Standard Model calculations. We have experimental evidence for the existence of the bosons carrying the first three forces. Differently however for gravity, the boson carrying the mass – the Higgs-boson – is still undiscovered.

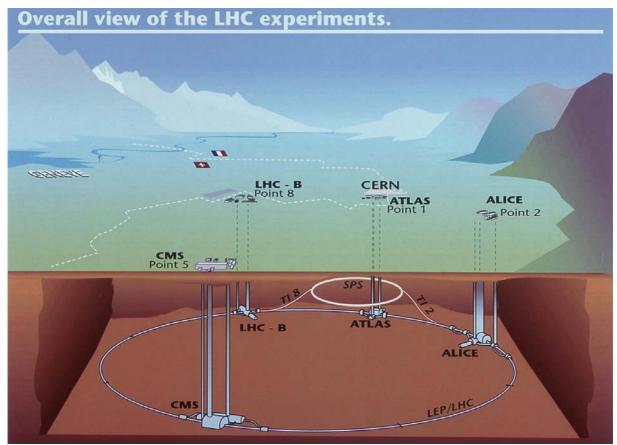

To find the Higgs and to explore other important issues of particle physics – like SUSY [SUSY], CP violations [CPV] or QCD [QCD] – a huge machinery has been developed: the LHC [LHCJINST] at CERN. At the LHC two proton beams are accelerated and are travelling in opposite direction in the LHC ring. At 4 experimental stations, ATLAS [ATLJINST], ALICE [ALICEJINST], CMS [CMSJINST] and LHCb [LHCBJINST], the beams can be focused such that the protons collide with a maximum energy of 2 \* 7TeV, an energy level close to that at the origin of the universe.

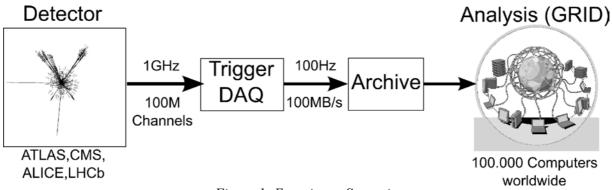

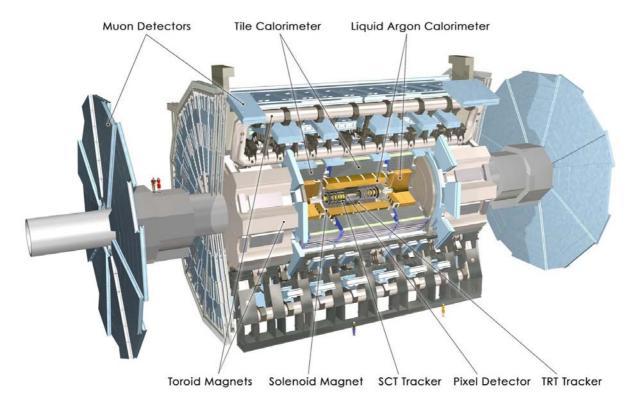

Figure 1: Experiment Scenario

Each of the experimental stations, where ATLAS is the largest of, employ very complex equipment – called a detector<sup>2</sup> – to find all the particles which are produced during and immediately after the collisions. The ATLAS detector is a 44m long, 25m high, 7000t heavy precision measurement instrument consisting of 7 different sub-detectors<sup>3</sup>, generating data on roughly 100 million channels at

<sup>1</sup> This is clearly opposite to the human common sense, which easily accepts gravity as the strongest and most obvious force, while it is not aware of the strong and weak forces.

<sup>2</sup> The "detector" is in fact a collection of different detectors, sensitive for different particles like electrons and muons.

The sub-detectors are: Muon chambers, semiconductor tracker, transition radiation tracker, pixel detector, LAr electromagnetic calorimeters, LAr hadronic calorimeters and tile calorimeters.

a interaction rate of the protons of  $1 \text{GHz}^4$ . The event recording rate however is limited to 200 Hz at an event size in the order of 1 MB. To achieve the required data reduction of  $5 \times 10^6$  a complex and efficient trigger and data-acquisition system (TDAQ) is needed. A simplified view of this general scenario is shown in Figure 1.

Traditionally, trigger and data-acquisition systems in high-energy physics (HEP) utilise custom electronics in many areas, for example to interface to the detectors, to satisfy extreme performance or density requirements or because the electronics is exposed to radiation. There are also several disadvantages to custom electronics, in particular cost, long development times and a long-term dependency on particular know-how and components. Considering the development time of 15 years, the operation time of another 10 years or more and the cost, there was a strong desire to use COTS wherever possible to build the ATLAS TDAQ system. The ATLAS solution to this dilemma in the TDAQ area is to equip standard PCs (the COTS) with custom modules, which provide the missing performance and functionality.

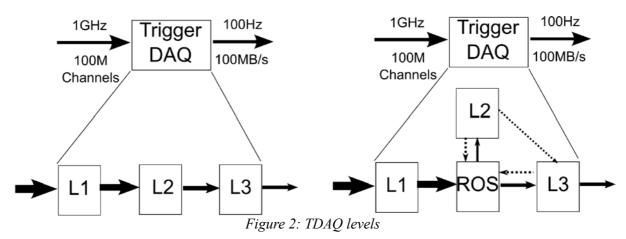

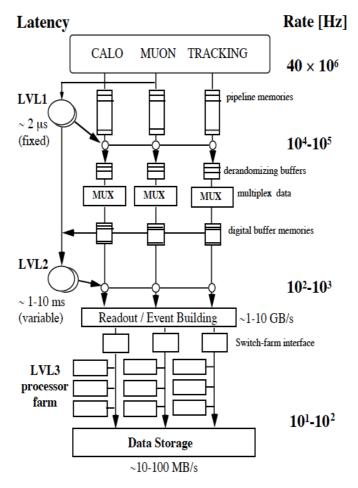

ATLAS TDAQ uses a layered trigger architecture to reduce the amount of data to be transferred. The levels are called level-1 trigger (L1), level-2 trigger (L2) and event-filter<sup>5</sup> (EF), the latter two form the higher-level triggers (HLT). The L1 is closely coupled to the front-end electronics of the sub-detectors and uses custom electronics to get the event rate down to 100kHz. L2 and EF are based on farms of commodity PCs. Unlike many HEP experiments the L2 of ATLAS does not operate on the full detector data volume but reduces the amount of data with two mechanisms – the region-of-interest (RoI) principle and the sequential selection strategy. Figure 2 shows the traditional approach on the left, where data rate and volume are reduced layer by layer while data is pushed through the TDAQ system and the ATLAS approach on the right, where the data is stored after the first step (L1) in the ROS and L2 and EF request only a fraction of the data.

The ROS, again a farm of PCs, implements the buffering capabilities of the DAQ and interfaces to the detector/L1 system on one side and to the HLT system on the other side. The detector/L1 side generates fragments of the event data on 1600 channels and transmits them at the L1-rate of up to

<sup>4</sup> The proton beams are structured in bunches and the bunch crossing frequency is 40MHz. For individual protons the collision rate becomes 1 GHz.

<sup>5</sup> The third trigger level (L3) is called Event Filter (EF) in ATLAS terminology.

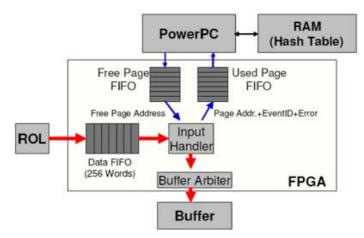

100kHz through unidirectional<sup>6</sup> optical links (ROL) with a nominal bandwidth of 160MB/s. L2 and EF subsequently request portions of the data from the ROS. Typically, L2 requests occur at a higher rate but address only a fraction of the fragments while EF requests occur at a lower rate but address full events. Rate and bandwidth exceed the capabilities of commodity PCs by far.

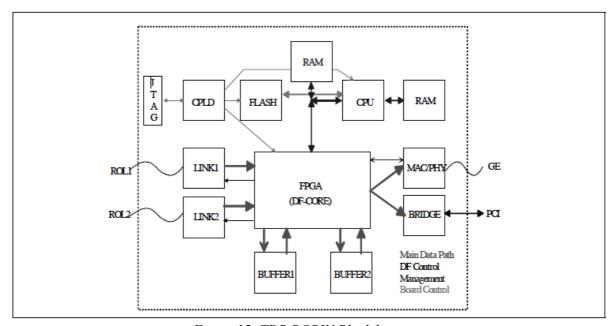

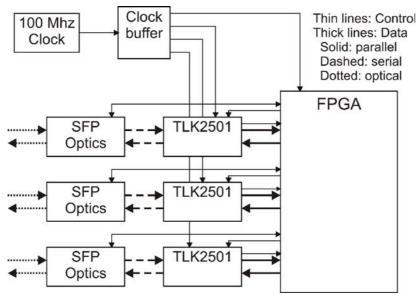

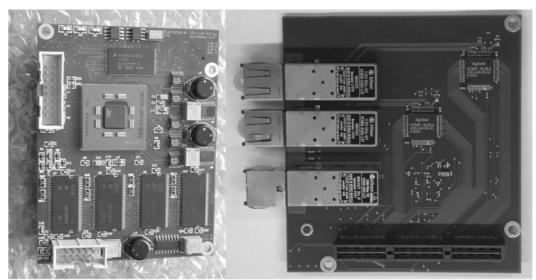

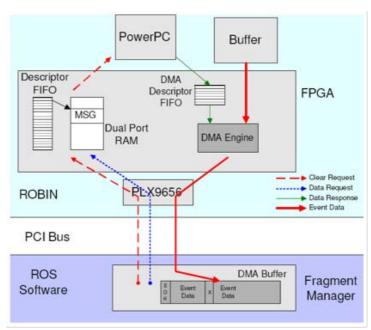

To achieve the required performance, a custom FPGA-based I/O-coprocessor – the ROBIN – was developed. Early studies [DJFROB] showed, that the handling of a single ROL using a combination of re-configurable logic and processor is possible<sup>7</sup>. Subsequent technology studies led to the development of different single channel modules, followed by a dual-channel ROBIN-prototype. The final implementation of the ROBIN concentrates three input channels on a 64-bit PCI card. The architecture and hardware design of the ROBIN is based to a large extent on systems developed previously by the author (MPRACE-1, see 8.1.1) or to which he has contributed significantly ( $\mu$ Enable, see 8.1.2).

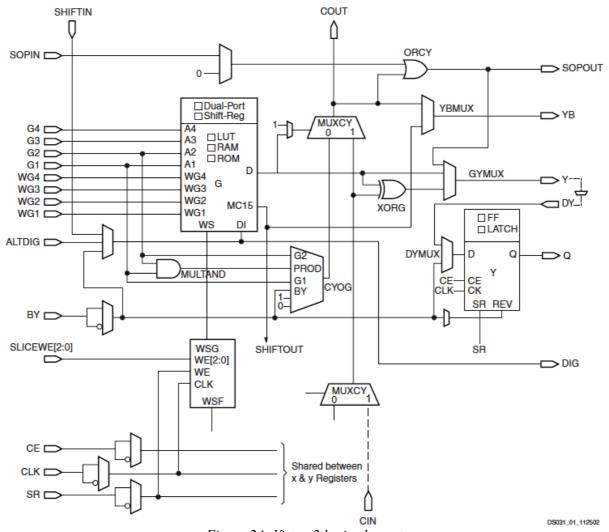

In addition to the baseline readout scenario via the PCI bus it also supports the switch-based readout scheme via an integrated 1G-Ethernet port. Due to the high performance requirements a custom datapath controller is needed, which is implemented in a 2M-gates FPGA. FPGA technology enables to create efficient and optimised I/O interfaces, memory controllers and logic functions in a single device, while keeping flexibility and maintainability. An attached processor implements the management, messaging and monitoring functionality.

This work describes the development, implementation, production and installation of the ATLAS ROBIN. The results show that the ROBIN as a component satisfies the requirements with respect to performance and cost. In addition, the ATLAS ROS, which is the framework for the ROBIN, has demonstrated to reach its performance goals. The low failure rate observed during approximately one year of operation prior to the LHC start-up in September 2008 demonstrates the reliability of the ROBIN.

This thesis is structured as follows:

- Chapter 2 provides an overview of typical HEP data-acquisition systems, with a focus on the CMS experiment.

- The ATLAS Trigger and DAQ system is described in chapter 3.

- Important technological aspects in particular the FPGA technology used for the implementation of the ROBIN are introduced in chapter 4.

- The details of the ROBIN: development, implementation, production and commissioning are described in chapter 5.

- The results from stand-alone and system tests are presented in chapter 6.

- Chapter 7 concludes with an assessment of the achieved goals and an outlook for the upcoming ATLAS operation and upgrade phases.

- The appendix provides information on previous systems and some additional tables relevant for the operation of the ROBIN.

<sup>6</sup> The ROLs are physically bi-directional, but the sole use-case for the return path is flow-control.

<sup>7</sup> The early prototypes didn't have any of the operational monitoring features present on the current ROBINs.

# 2 Data Acquisition Systems

This chapter presents the main issues typical data acquisition system have to cope with. The "PUSH" data transfer model followed by ALICE, CMS and LHCb is introduced and its distinction from the "PULL" model employed by ATLAS. The implementation of CMS – the largest partner experiment to ATLAS – is shown in detail and the characteristic parameters of ALICE and LHCb are presented.

In short, the task of a data-acquisition system is to collect data from an arrangement of sources and to deliver it to a unit which performs storage and typically analysis. In the case of ATLAS and the other LHC experiments the individual DAQ systems have to deal with some or all of the following challenges:

- Large number of input channels

- Large data volume

- High rate of events

- High connectivity and throughput requirements on networks

- High performance requirements for event processing

- Buffering required to compensate latencies

- Low cost, longevity, scalability, etc.

# 2.1 LHC Experiments

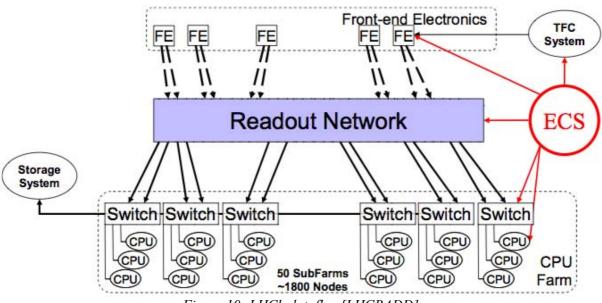

The LHC proton-proton collider is situated at CERN, Switzerland in a 27km long circular, underground tunnel (see Figure 3). There are four main experimental sites: ATLAS, ALICE, CMS and LHCb. ATLAS and CMS are general purpose experiments for the study of proton-proton collisions. ALICE is specialised for the study of heavy-ion collision, LHCb is specialised for the study CP violations in B-meson decays. ATLAS and CMS are the two largest experiments, which pose similarly high requirements on the Trigger/DAQ system: L1-rate of 100kHz, event size of 1MB and a storage rate of 100Hz, in other words an input bandwidth of 100GB/s and an output bandwidth of 100MB/s. ALICE and LHCb have different demands – higher L1-rate at smaller event size or vice versa. The DAQ of LHCb runs at an event rate of 1MHz and an output rate of 2kHz, the average event size is 35kB [LHCBDAQ]. In contrast, ALICE DAQ has a low input rate of around 8kHz but event sizes can be as large as 85MB. ALICE operates in different modes, with and without trigger, the maximum sustained output bandwidth is assumed to be 1.25GB/s.

The experiments ALICE, CMS and LHCb follow the traditional "PUSH" model for data transportation in the DAQ system, although different options have been looked at during the development phases (e.g. so called "phased" readout in LHCb [LHCBTB]). The main characteristic here is the fact, that for every event the entire data volume is unconditionally transported – typically over several layers of different media – to a node which assembles the full event prior to the recording on permanent storage, which is based on a trigger decision. This leads to very high bandwidth requirements on the interconnect infrastructure. Also, low latency transmission is needed to avoid substantial intermediate buffering. In ATLAS and CMS for example the stages feeding the DAQ dataflow system provide

virtually no buffering beyond the 3 to 5µs latency of the L1 trigger. Many networking technologies have been investigated during the development phases of the LHC experiments with an emphasis on Ethernet due to its dominance in the mass market. To overcome the limitations of its technical properties – in particular the missing reliability, which is frequently compensated by reliable protocols like TCP/IP at the expense of long latencies – optimisations had to be implemented by the two experiments. CMS uses a reliable initial network layer to form sub-events which are then transported via a reliable protocol over GE. ATLAS reduces the required network load with the help of the additional L2 and ROS stages, which allows to tolerate an unreliable network. For ALICE and LHCb the total network bandwidth is lower hence better adapted to GE technology. The total connectivity of the dataflow networks is in the order of 1500 ports for ATLAS, CMS and LHCb and 350 ports for ALICE.

Figure 3: LHC at CERN\*

The "PUSH" model was considered by ATLAS initially as well, but then the experiment has made a different choice by implementing a true "PULL" model, in order to take full advantage from the sequential selection scheme and the RoI principle (see section 3.1). Here, the detector data are captured directly after L1 in an intermediate buffer in the ROS which forwards them only upon request to the HLT and DAQ system. This approach reduces the amount of data to be transferred to about 6% of the initial data volume after L1 for the typical case. This reduction in the total throughput of the dataflow enables the use of an all-commodity network infrastructure. The drawback is the increased

system complexity due to the additional flow of control messages (data request and delete messages), the additional intermediate buffering stage and L2 trigger.

All LHC experiments employ a custom component to receive data from the sub-detectors over dedicated links and to feed them – directly or via a PC – into a network infrastructure. Due to the transport model used in ATLAS this component – the ROBIN – has a complexity far higher than that of the other experiments. Technically, the ATLAS ROS could be tuned from its regular operation mode (reducing the data volume by a factor of 10 roughly) up to a full readout mode (forwarding the entire data volume), of course at the expense of additional components. Also, conversion to "PUSH" mode would be viable (however is not foreseen) by re-programming of the existing components.

The "PULL" mode is not viable for the DAQ systems of the other LHC elements, as the network infrastructure is not prepared to handle the required rate of request messages and there is no intermediate buffering capacity available to cover the latencies of the HLT systems. Investigations during the upcoming SLHC upgrade programme will certainly revisit both models for all experiments.

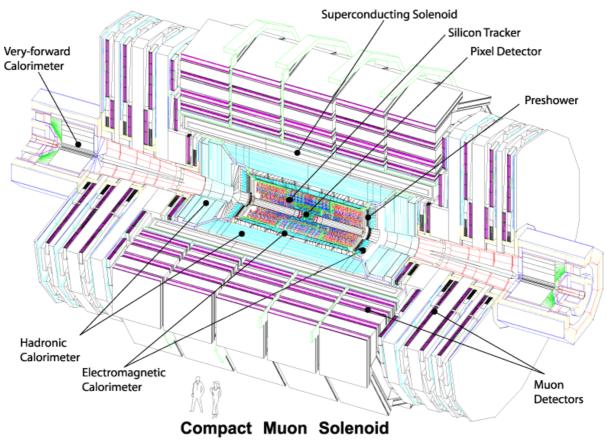

#### 2.1.1 CMS

The CMS experiment is a large multi-sub-detector precision measuring device for charged particles and photons. The momentum of charged particles is measured via the curvature of particle tracks, caused by the bending force of a strong, superconducting magnet. The inner tracking detectors (pixel, silicon strip) and the hadronic and electromagnetic calorimeters are placed inside the 13m long magnet. Four muon-detecting stations are located externally to the magnet. The arrangement is shown in Figure 4. When operating at design luminosity approximately 1.000 particle tracks per bunch-crossing (25ns) will pass the inner tracking detectors. This requires a high resolution of the pixel and silicon strip sensors, leading to high power and hence cooling requirements. However, the resulting installations (cables, cooling pipes) introduces unwanted effects<sup>§</sup>, so the design is a compromise.

#### 2.1.1.1 Trigger

CMS uses a 2-level trigger system. The L1 is implemented in custom hardware and reduces the 40MHz bunch-crossing rate to an L1-event rate of 100kHz. The generated data volume is in the order of 100GB/s, distributed over 626 data sources from the various sub-detectors. This entire data volume has to be transferred to a large computing farm running the HLT algorithms [CMSTRIG]. Subsequently, filtered events are sent at 100Hz to permanent storage.

<sup>8</sup> All material in the detector can cause multiple scattering, bremsstrahlung, photon conversion and nuclear interactions.

Figure 4: CMS Detector [CMSJINST]

## 2.1.1.2 DAQ

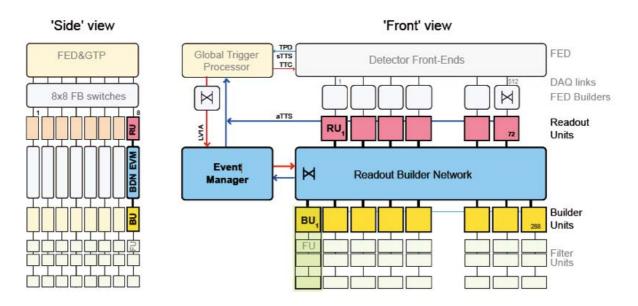

The DAQ architecture responsible for the transport of data is shown in Figure 5. All detector channels – approximately 55 million – are assembled into 626 event fragments of 2kB size in the detector frontend electronics and buffered during the L1 latency of 3.2μs in the front-end-drivers (FEDs). The event fragments are pushed at L1-rate from the FEDs through LVDS cables<sup>9</sup> into 458 front-end read-out links<sup>10</sup> (FRLs). A Myrinet<sup>11</sup> based FED-builder (FB) network creates 72 super-fragment [CMSSFB] streams – each composed of 8 fragments from different FRLs – which are directed to 72 readout units (RUs). Full events are then built by combing the data from all 72 RUs via the readout-builder-network in the builder-units (BUs), which also run the HLT algorithms via the filter-units (FUs) applications. As a pure "push" architecture CMS DAQ does not require any significant buffering of the event fragments but a very large network bandwidth.

This architecture has an inherent scalability provided by the 8x8 switches of the FB layer. Every FB switch can route the fragments from the 8 input links to up to 8 output links, for example based on the L1ID. CMS uses this feature to build a "sliced" DAQ system, where the total performance can be tuned via the number of slices attached to the FB layer (see Figure 5:side view). A single slice consists of 72 RUs, a builder-network switch and 288 BUs/FUs and is able to process 12.5kHz of L1-rate. The

<sup>9</sup> The LVDS links follow the S-Link64 specification [SLINK64]

<sup>10</sup> The canonical number for FRLs is 576. Only FRLs are equipped with 2 input links which connect to FEDs with lower output bandwidth, such that the nominal input bandwidth of 200MB/s per FRL is not exceeded.

<sup>11</sup> http://www.myri.com/open-specs/index.html

full performance of 100kHz L1-rate is obtained with 8 slices, which corresponds to 576 RUs and 2304 BUs.

Figure 5: CMS DAQ [CMSJINST]

#### 2.1.1.3 Readout Builder

The second stage of the CMS event-builder – RUs, builder network and BUs – is made from COTS components: PCs and a Gigabit-Ethernet (GE) network. Due to the layered and sliced architecture the required connectivity is only 72 x 288 per readout-builder network (instead of 512 x 2304 for a full single layer event-builder). However, GE does not match the input bandwidth (200MB/s) on the RUs from the Myrinet FED builder, hence a multi-rail implementation [CMSGBE] with up to 4 GE-NICs per node was chosen, leading to an aggregate bandwidth of 500MB/s. To achieve a high network performance the Ethernet packet size had to be increased to 7kB from the standard MTU size of 1500 byte. Results from a 16RUs x 60BUs test-bed<sup>12</sup> using 2 GE rails show a throughput for an RU well above the required 200MB/s for the standard super-fragment packet size of 16kB. The steering of the super-fragments into the RUs and from the RUs to the BUs is controlled by an event-manager (EVM) which also checks the memory allocation at the RUs and eventually requests to reduce the L1-rate via an interface to the global trigger processor (GTP). The BUs send readout-request to the EVM which in turn provides event-tag information to the RUs, which then send the super-fragments to the indicated BUs.

#### 2.1.1.4 *FED Builder*

The first stage of the CMS event-builder is composed of the FRLs and the Myrinet FB. Myrinet was selected due to the inherently reliable transmission which is achieved by using a physical media<sup>13</sup> with

<sup>12</sup> The test-bed used dual single-core XEONs with 2.6GHz.

<sup>13</sup> Initially, Myrinet used parallel LVDS transmission. The current implementation is based on optical transmission with 2Gbit/s.

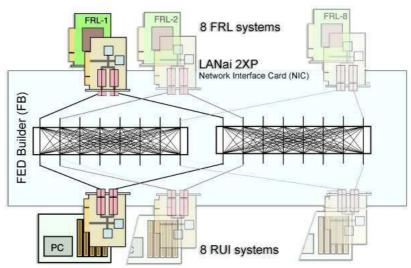

a low error rate, built-in CRC error detection and an efficient flow-control mechanism using a "slac" buffer. Myrinet packets can be of any length. In addition, all Myrinet network adapters and switches are equipped with a user programmable RISC processor which is used by CMS to add custom functionality. The FB connects all FRL sources (up to 512) with all 572 RU destinations via 8x8 port switches 15. The CMS routing strategy implemented on each of the 8x8 switches combines one fragment per input into a super-fragment. Super fragments are sent to the RUs attached to the output ports depending on the event-number and a pre-loaded routing table, which in turn depends on the number of DAQ slices (every output represents a slices). As the FRLs on the input are equipped with dual-link Myrinet NICs the FB is composed from two independent "rails", each connected to one of the FRL outputs. The two-rail structure is shown in Figure 6.

Figure 6: CMS FED-Builder Rails [CMSJINST]

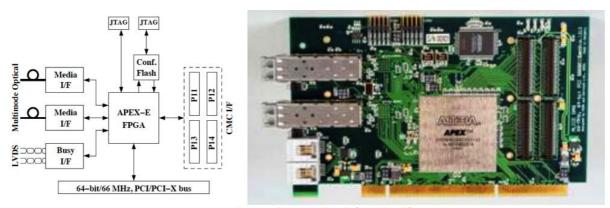

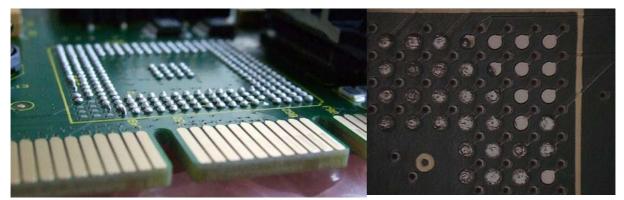

Considering its location at the interface to the detector the FRL is the CMS component which is most equivalent to the ATLAS ROBIN – although it does not provide significant buffering. Furthermore, it has certain technical similarities, namely the combination of FPGA, embedded processor and host CPU. The FRL [CMSFRL] is a single width cPCI<sup>16</sup> card which consists of a custom base module, attached to the cPCI bus plus a commercial dual-port Myrinet network interface adapter (NIC<sup>17</sup>), plugged on to the base module via a standard PCI connector (Figure 7). The main FRL FPGA<sup>18</sup> merges the fragments from the two S-Link64 inputs (with the help of a small amount of external memory), checks the CRC and writes the combined data in blocks of fixed length to the Myrinet NIC. Additionally, the FRL provides monitoring features like fragment size histograms and can take data samples. These auxiliary functions are available via the cPCI bus to the crate controller CPU which

<sup>14</sup> The Myrinet slac buffer is basically a FIFO with low and high watermark indicators, which are used to stop and start incoming transfers.

<sup>15</sup> In practice a larger switch is used to implement multiple independent 8x8 groups.

<sup>16</sup> Compact PCI (cPCI) is the industrial version of PCI, see http://www.picmg.org/test/compci.htm

<sup>17</sup> http://www.myri.com/vlsi/LanaiX.Rev1.1.pdf

<sup>18</sup> The main FPGA is an ALTERA EP1S10 device with 10k logic elements (LEs), 60 block memories and 6 DSP blocks.

controls up to 16 FRLs per crate. The nominal bandwidth on the input and output is 200MB/s, which is easily met by the S-Link64 (400MB/s). The Myrinet NIC is a dual-link version and both links together provide 4Gbit/s.

Figure 7: FRL image and block diagram[CMSFRL]

Although the NIC is a commercial device, it is used together with a custom firmware which allows it to communicate with the main FPGA on the base module via a private PCI bus. The FPGA deposits the merged event fragments into the local buffer of the NIC and instructs it to transmit the packets by writing a DMA descriptor. At the system level, a throughput of 300MB/s per FRL for varying size fragments with 2kB average has been measured [CMSSFB], well above the requirement of 200MB/s.

#### **2.1.2** ALICE

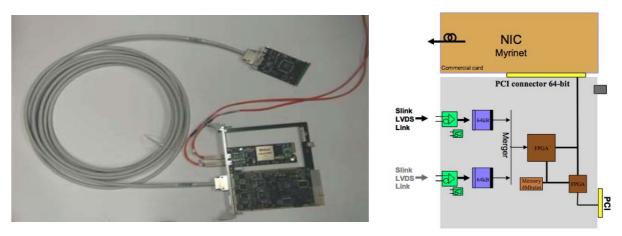

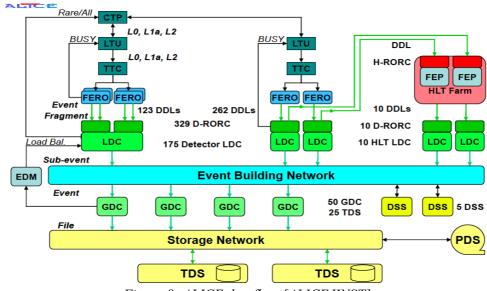

The ALICE dataflow architecture is displayed in Figure 8. Raw data are collected close to the detector in front-end readout cards (FERO) and transmitted via optical links (DDL) to data receiver cards (D-RORC), two of which are hosted each by one local data concentrator (LDC). The LDCs build sub-

Figure 8: ALICE dataflow [ALICEJINST]

events (similar to CMS super-fragments) and output them to a GE network. Full events are assembled by global data concentrators (GDC) and ultimately shipped to mass storage, eventually based upon decisions from the HLT farm. The HLT trigger is fed from a subset of the detector only, via bypass links each established by one of the D-RORC DDL channels.

The ALICE component which is most equivalent to the ROBIN is the D-RORC [DRORC], which receives two optical inputs at 200MB/s each and stores the data into the memory of the host PC. Alternatively, one of the links can be used to send a copy of the input data to the HLT farm. As can be seen from the block diagram [ALICETDR] in Figure 9 the D-RORC does not contain any local memory or processor, but is just an I/O extension to the PC. Measured throughput into host-memory reached 484MB/s, well above the combined bandwidth of two optical links.

Figure 9: ALICE D-RORC [DRORC]

#### 2.2 LHCb

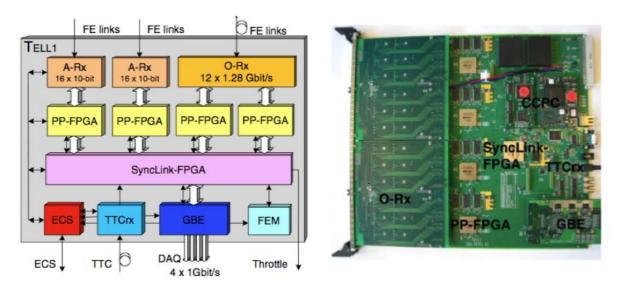

The dataflow architecture [LHCBADD] of LHCb as shown in Figure 10 is relatively simple, as it does not use a separate L1<sup>19</sup> concentration layer. Instead, each of the 310 front-end (FE) units [LHCBTELL]

Figure 10: LHCb dataflow[LHCBADD]

19 In LHCb the first trigger level is called L0. However to avoid confusion the term L1 is used in this document.

located close to the detector collects data from a combination of up to 64 analog or 24 digital<sup>20</sup> channels respectively and transmits L1 accepted events via 4 built-in GE output ports to the readout network, which provides a total connectivity in the order of 2500 ports maximum. LHCb aims to keep the load on the GE network below approximately 70%, as experimental studies have shown that the risk for message loss is close to zero for loads below this value.

The FE card – called TELL1 – is a 9U VME card (Figure 11, right) which features several different I/O interface in addition to the data input and output ports. The ECS ports connects to the slow-control system of the experiment, the TTC port receives the central timing and control information. A throttling mechanisms slows down the L1 accept rate once the local buffers, which need to cover the 4µs L1 latency, become saturated. The PP-FPGAs (Figure 11, left) perform sub-detector specific processing of the raw detector data, while the SyncLink-FPGA is responsible to assemble and transmit event fragments.

Figure 11: LHCb TELL1 [LHCBTELL]

Compared to the other experiments the TELL1 cards looks rather like the combination of front-end readout and DAQ interface, an approach which was also investigated by ATLAS in the course of the ROB-on-ROD project (see chapter 3.3.4).

#### 2.3 Summary

The large LHC experiments CMS and ATLAS generate a few 100 particles every 25ns when operating at design luminosity. Particle tracks are recorded by different detector subsystems via 50 to 100 million sensor channels. A custom first level trigger located close to the detectors is used to select interesting events and provide them to the DAQ/HLT subsystem, which in turn is characterised by a an input rate of 100kHz and an input bandwidth in the order of 100GB/s. The event building processes require to connect roughly 1.000 sources to 1.000 destinations. The latter filter the events according to trigger algorithms, leading to an overall reduction in bandwidth and rate towards mass storage by a

<sup>20</sup> The nominal speed of the digital inputs is 1.25Mb/s.

factor of 1000. All LHC DAQ systems are in general based on commodity technology - GE networks and standard PCs - but need some custom components at the input stage. In particular for CMS and ATLAS a scalable system was required due to financial issues, which allows to operate the system with reduced resources at reduced performance.

The CMS approach as described in this chapter transports the entire data volume – nominally events of 1MB size at a rate of 100kHz – via a layered architecture, following the traditional "PUSH" model. The initial layer employs 458 custom FPGA-based data converters (FRLs) and a Myrinet builder network (FB) made from 72 8x8 switches. The FB provides data from all sources on 8 parallel outputs which feed up to 8 slices of the subsequent stage. Each of the slices consists of 72 readout-units (RU) receiving Myrinet packets at 200MB/s, a GE network and 288 builder units (BU), which assemble the full events and run the event filter algorithms. The performance is scalable at 12.5kHz per slice.

ALICE and LHCb have somewhat different characteristics in terms of rates and event sizes and lower requirements with respect to total bandwidth. However, both share the same "PUSH" model for the dataflow as CMS does and employ similar architectures and technologies for the custom DAQ components.

In contrast, ATLAS introduced the intermediate L2 layer operating on RoIs – typically only a few kB at a rate of 100kHz – and transporting full events – about 1MB each – at a low rate of a few kHz. This architectural decision was taken with the aim for a full commodity dataflow network and under the assumption that processing power at the L2 will be relatively inexpensive at the time of operation.

All four experiments use custom FPGA components at the boundary between the sub-detectors and the dataflow system, which translate from proprietary signals into some networking standard. In case of ALICE and CMS the functionality is basically limited to this translation step. The LHCb component integrates additional functionality related to data processing and first level event selection. The ATLAS dataflow architecture is unique in its demands for buffering at the input and communication capabilities to serve the "PULL" model and requires high-performance FPGA technology combined with high-performance embedded processing – which are realised by the ROBIN component. The ATLAS approach is explained in the following chapter.

# 3 ATLAS DAQ

ATLAS is the other "large" experiment at the LHC, with requirements very similar to CMS (see section 2.1.1). This chapter introduces the ATLAS detector with the focus on the architecture of the ATLAS TDAQ system. The unique ATLAS approach to reduce the throughput requirements by a significant amount using the RoI-principle and sequential-selection in the L2 trigger stage is explained, due to the impact on the architecture of the dataflow. The baseline dataflow system of ATLAS and the ROS are described in detail, which define the requirements on and the environment of the ROBIN.

# 3.1 System View

The ATLAS detector is – like CMS – composed from different sub-detectors to identify charged particles (muons, electrons, …) and to measure other observables (vertex displacement, missing transverse energy, …). The layout of the magnets is different from CMS, which uses a single large solenoid magnet while ATLAS has a an inner solenoid and a group of toroid magnets further away from the centre. A sketch of the 7000t heavy detector is shown in Figure 12.

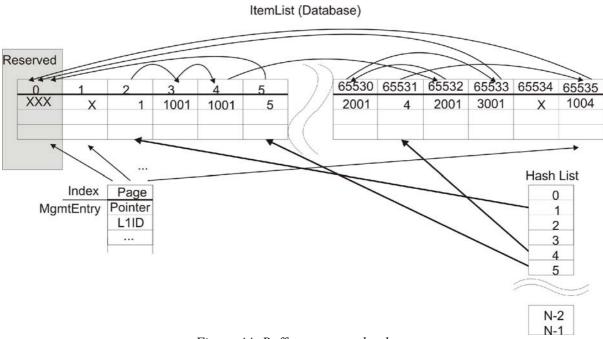

The seven sub-detectors of ATLAS together generate data on roughly 100.000.000 channels, the vast majority of belonging to the pixel detector. These channels are collected by electronics on or close to the detector and combined into 1600 ROD modules. The RODs are also connected to the L1 and the timing system of ATLAS and format data plus event identification into ROD fragments. A simple

Figure 12: ATLAS detector\*

unidirectional link, the S-Link [SLINK], is used to connect the RODs with the TDAQ system. From the TDAQ point of view the ATLAS detector is a data source with 1600 channels, 100GB/s bandwidth<sup>21</sup> and 100kHz event rate. The task of ATLAS TDAQ is to select and store only 0.1% of the generated data volume.

The initial concept to implement the ATLAS TDAQ system as documented in the "ATLAS Technical Proposal" [ATLASTP] is shown in Figure 13. After L1 a digital buffer memory is used to store L1

Figure 13: ATLAS TDAQ TP-version [ATLASTP]

data. An RoI-collection (RoIC) subsystem<sup>22</sup> copies the RoI-portions of some sub-detectors to the L2 system. An RoI is derived from the geographical information<sup>23</sup> attached to the L1 event identifier (L1ID), and defines a subset of a sub-detector, typically around 2%. The L2 is a modular system and operates in two steps. In an initial feature-extraction step all sub-detectors are individually and in

<sup>21</sup> The maximum bandwidth is 1600 channels \* 160MB/s = 256GB/s. However, the nominal fragment size is 1kB and even less for quite some of the sub-detectors.

<sup>22</sup> The digital buffer memories in Figure 13 have two output paths, the main towards "Readout/Event Building" and a second one, which builds the RoIC, towards LVL2.

<sup>23</sup> The particles generated in the collisions produce electrical signals in the detectors while they escape from the the interaction point. Any signal generated on one of the detect channels is called a hit.

parallel analysed for interesting data. The features are subsequently combined by a global decision step into the L2 decision, which is then distributed to the event building stage. At that time different approaches for the L2 implementation were discussed and investigated in a demonstrator programme [ATLDEMPROG] – a global L2 farm, the use of a local sub-farm²4 per sub-detector and the use of custom data-driven L2 processors based on FPGAs either replacing the local sub-farms or in a hybrid fashion together with sub-farms. The different L2 options also affected the design of the readout subsystem, e.g. the latency of the data-driven L2 was much lower than that of the global and local farm approaches. However, it required the fast distribution of the RoI-information to the readout buffers and the RoIC subsystem. The network technologies proposed for the L2 farm interconnects were ATM, SCI and Fibre-Channel, none of which has a significant market share today. Also, three different networks were to be used to transport event data from the buffers to the L2, from the buffers to the L3 and to transport L2 decisions.

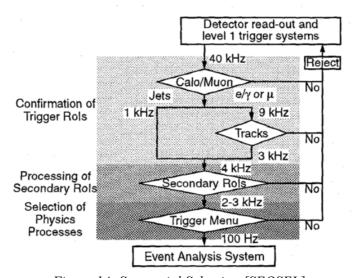

A significant simplification for the TDAQ architecture was achieved by the introduction of the sequential selection strategy [SEQSEL] for L2. Sequential selection takes advantage from the fact that all important physics events require the presence of signals in the Muon detector and the calorimeters. Thus looking for Muons first allows to reject ¾ of the events at the L2, as shown in Figure 14. A subsequent check for electrons, photons and jets enables rejection of another 60% of events. The sequential selection strategy reduced the requirements on the system throughput and allowed to merge the separate, sub-detector specific L2-subfarms of the initial architecture into a single, uniform L2 farm. The required processor farm size for the sequential execution of the L2 was estimated by modelling [PAPMOD] to be in the order of 200 machines. However, sequential selection also has a drawback, which is the increased complexity of the dataflow architecture. The traditional "push"-mode has to be replaced with a "pull"-mode dataflow, which needs relatively advanced interactions between the subsystems (see chapter 3.2).

A test-bed [PILPRO] was setup to verify the performance of the associated dataflow system with different network and readout buffer implementations<sup>25</sup> [ROBCPLX]. The range of technologies investigated is summarised in Table 4.

| Technology    | Options                               |                                      |                                 |                      |

|---------------|---------------------------------------|--------------------------------------|---------------------------------|----------------------|

| FPGA          | High-end, provides core functionality | Medium, I/O plus auxiliary functions | Low-end, I/O only               |                      |

| Processor     | Host only                             | Local DSP                            | Local 32-bit<br>Microcontroller | High-end SMP<br>host |

| Bus           | PCI (PMC mezzanine)                   | PCI (standard format)                | VME                             |                      |

| Network       | ATM                                   | SCI                                  | Gigabit-Ethernet                |                      |

| Optical links | 2.5Gbit/s single fibre                | Multiple fibre<br>15Gbit/s (Paroli)  |                                 |                      |

*Table 1: Pilot Project Technologies*

<sup>24</sup> At the time of the TP approximately 300 processors would have been needed for a local sub-farm.

<sup>25</sup> During the pilot project phase the terminology "ROB Complex" was used which corresponds to the current ROS.

The pilot project defined the ROS to be the aggregation of a number of input units receiving data from the RODs, associated buffers, some intelligent controller(s) to manage the event fragments and handle requests and a number of output units interfacing to the L2 and EB network. The range of configurations investigated covered the most simple one (single input unit, single controller, single output) up to the "Active ROB Complex" [AROBC] where many input units were handled by a powerful SMP host. The latter concept also included data-processing at the level of the readout subsystem.

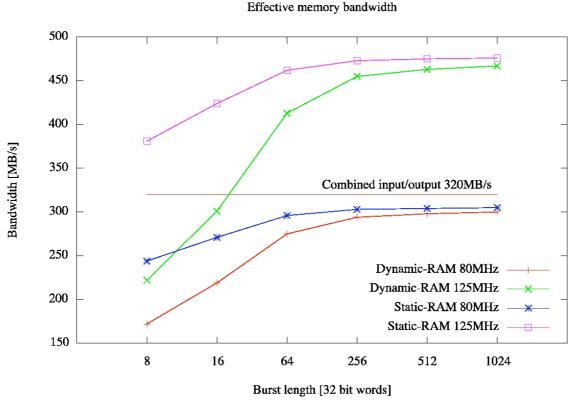

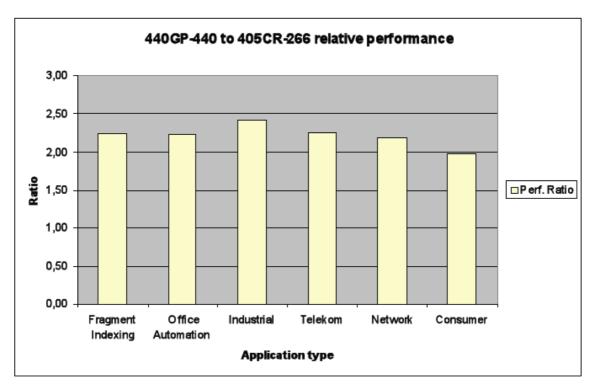

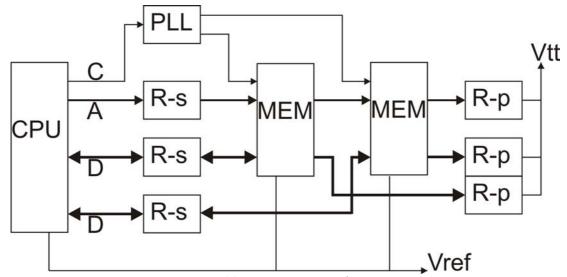

The results<sup>26</sup> obtained during the pilot project phase showed that the requirements of the ATLAS dataflow could be satisfied in principle with the proposed ROS architecture, however a solution was needed in order to achieve the goals for density and cost. From the prototype implementations the ones with a large fraction of functionality implemented in FPGAs provided the best performance, while the processor-oriented suffered from the high rate. Two other areas were identified as potential bottlenecks: the memory subsystem – in particular if shared by processor and buffer – and the parallel bus, specifically the drop in available bandwidth for high message rates. All issues could be addressed by the design of the subsequent ROBIN.

Figure 14: Sequential Selection [SEQSEL]

As a consequence, the ROS consisting of a standard COTS PC equipped with a number of FPGA-based ROBINs became the baseline implementation (see chapter 3.3.3) as documented in the ATLAS Trigger and DAQ Technical Design Report (TDR) [ATLASTDR], which addressed the issues mentioned above in the following way:

- The use of COTS PCs reduces cost

- Concentration of multiple input links per PCI card allows to build a compact system

<sup>26</sup> The pilot project considered two operating conditions – low and high luminosity – of the LHC, with corresponding L1-rates of 40kHz and 75kHz respectively. This is in derivation of the standard 100kHz/high luminosity case assumed elsewhere in this work.

- A central FPGA per ROBIN enables high-rate and high-bandwidth I/O handling

- An auxiliary local processor provides flexibility

- An auxiliary local network interface provides an upgrade path for bandwidth- or rate-intensive request schemes

Figure 15: TDR ROBIN Blockdiagram

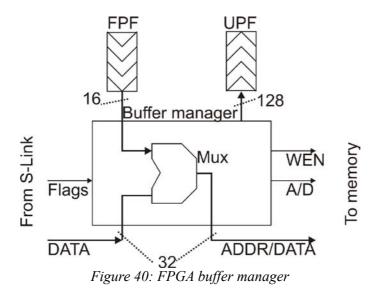

Figure 15 illustrates the TDR ROBIN design, with a central FPGA comprising the main data path from the two input links to the two buffer memories and onwards to the alternative output interfaces PCI and GE. FPGA technology – which is described in chapter 4 – enables to implement I/O interfaces, memory controllers, direct-memory-access (DMA) engines and various other functions on a single device in an optimised and highly efficient way while maintaining flexibility and upgradability. The local processor is attached to the FPGA as well, but separately from the main data path. The final design of the ROBIN is described in chapter 5.3 .

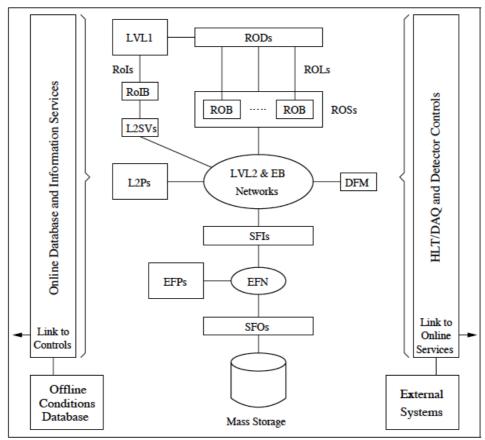

#### 3.2 Dataflow

The ATLAS Dataflow system is responsible to move the detector data from the interface to the detectors – implemented by the ROLs – up to permanent storage, attached via a standard network. A set of subsystems constitute the main data path (Figure 16, center) from the RODs to the mass storage. Additional subsystems provide control and configuration functionality (Figure 16, left and right). Due to the specific properties of ATLAS TDAQ the dataflow uses a mixture of "push" and "pull" mechanisms in order to transport data from one stage to the next one.

Starting at the RODs, event fragments are pushed to the ROBs. Concurrently, RoI information is pushed from L1 to the RoIB and onwards via the L2SVs to the L2PUs. The L2PUs use the L2 network to pull event fragments according to the RoI information via the ROS from the ROBs. The results

from L2 are pushed via the L2SVs to the DFM, which pushes "accept" decision to the SFIs and "reject" decisions to the ROS. The SFI again pull all event fragments from the ROS via the EB network, build the full events and push them to the EFPs. Finally, the events accepted by EF are pushed via the SFOs to mass storage.

Figure 16: Schematic layout of ATLAS TDAQ system [ATLASTDR]

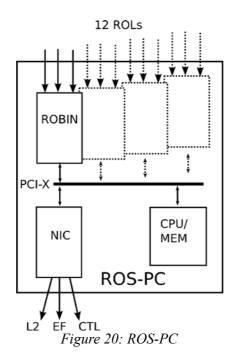

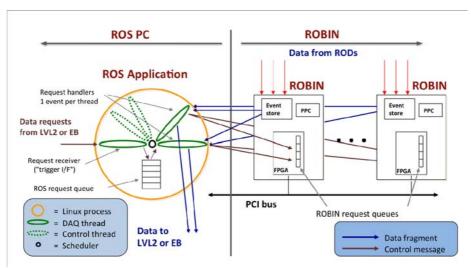

In the baseline dataflow model the ROBs are installed in ROS-PCs, each of which typically houses 4 ROBINs each representing 3 ROBs, so one ROS-PC serves 12 channels. The ROS-PC forwards all relevant requests to the ROBs via the PCI-bus and combines the responses to SFI-requests into larger fragments. In addition, the ROS-PC is responsible for configuration and monitoring of the installed ROBs.

Alternative scenarios bypass the ROS-PC for L2 and/or SFI requests and pull fragments directly from the ROBs, via their private Ethernet ports.

Apart from the bandwidth requirements ATLAS dataflow requires a network with good real-time performance, high reliability and high rate capabilities in particular on the L2 network. The requirements are largely comparable to the requirements of enterprise-size commercial networks where Ethernet is the de-facto networking standard. However, there is one difference: ATLAS DAQ requires low latency and reliability at the same time, while most of the typical Ethernet areas require only one of them. Ethernet networks follow the best-effort principle and are not reliable per-se, like

Myrinet is. Client-server applications for example introduce reliability by using a reliable protocol like TCP/IP over Ethernet, which can add significant delays to the transmissions. On the other hand, multimedia applications like IPTV or video conferencing are sensitive to latency but quite tolerant to packet loss and the unreliable UDP protocol is used frequently here.

The L2 system has an intrinsic latency of a few ms, caused by the execution time of the L2 algorithms, which defines the buffering requirements at the ROS. Any additional latencies introduced by the network increase the required amount of buffering capacity and make the system less stable. The use of a reliable protocol like TCP is not a general solution, due to the relatively long retransmission delays<sup>27</sup> in case of packet loss and its unavailability<sup>28</sup> on the ROBINs. An additional requirement on the reliability of the network at the low level is the use of multicast messages to distribute the DFM results to the ROS. Although Ethernet does not appear to be the ideal candidate for the ATLAS dataflow network from a technical point of view it was selected for reasons of cost, general availability, ease of use and expected longevity, which is important for an operation time of 10 years or more.

The total size of the ATLAS TDAQ system from the dataflow perspective is defined by the number of external data sources and by the number of networking nodes. The number of ROBINs and ROSes corresponds to the number of detector links and is fixed. The number of L2PUs and EFPs define the trigger capabilities and thus influence<sup>29</sup> the maximum L1-rate the system can handle. The expected numbers for the individual components is given in Table 2.

| Component        | Instances in final system | Comment                                 |

|------------------|---------------------------|-----------------------------------------|

| ROL              | 1600                      |                                         |

| RoIB             | 1                         | RoI: 2% of full event                   |

| ROBIN            | 600                       | 100kHz L1-rate                          |

| ROS              | 150                       | Separate network ports for L2 and EB    |

| L2SV             | 10                        |                                         |

| L2PU             | 500                       | Dual-CPU systems, ~100 events/s per CPU |

| DFM              | 35                        |                                         |

| SFI              | 100                       | Full event size ~1.5MB                  |

| EFP              | 1600                      | ~1 event/s per CPU                      |

| SFO              | 30                        |                                         |

| L2 network nodes | 700                       | 100 kHz, RoIs                           |

| EB network nodes | 300                       | 3 kHz, full events                      |

*Table 2: Data-flow components (TDR)*

The large number of network nodes cannot be attached to a monolithic magic box which provides the full connectivity for more than 1000 ports. Instead, the Ethernet approach for interconnecting nodes is

<sup>27</sup> The TCP retransmission timeout is typically set to 3s, which results in delays in the order of seconds.

<sup>28</sup> TCP requires to monitor every logical connection, which is too resource consuming on the ROBIN, where several hundred simultaneous connections may exist.

<sup>29</sup> Good linear scaling of L2, EB and EF documented in [ATLASTDR]

to cascade a number of units called switches, each serving up to a few hundred ports in a cross-bar fashion. Significant effort has been put by ATLAS into the analysis of Ethernet behaviour and equipment, well documented in [STANCU]. As mentioned above, the main issues with Ethernet apart from the connectivity - are latency and message loss. Both factors strongly depend on the technology of the switches. In principle, a switch has a unit handling the input (ingress), a unit handling the output (egress) and the cross-bar<sup>30</sup> connecting input and output. The routing path over the cross-bar is determined by the ingress unit from the header of every individual Ethernet packet, which starts with a source and destination address identification. The switch constantly monitors all source addresses and builds a map of addresses and ports. If a destination address is already in the table, the packet is routed to the corresponding port, otherwise it is replicated and sent to all ports. The latency introduced by this routing process is relatively small, as the evaluation of the routing path starts while the packet is still being received from the source. An obvious problem is the case where multiple source are sending to the same destination (so called funnel traffic) and such exceeding the egress bandwidth limit. While Ethernet allows the switch to simply drop packets in this case the most common solution is to queue packets at the input. If an input queue become full an Ethernet flowcontrol message is sent to the source, asking to pause the transmission. A common complication in Ethernet switches is head-of-line blocking, which occurs when an congested egress is blocking an ingress queue which contains also packets for another egress port. That egress can be idle in the worst case despite the fact that packets are available for it in an ingress queue. Some switches improve the situation by providing separate ingress queues<sup>31</sup> for some or all egress ports but at high load both loss and latency of Ethernet switch are inherently indeterministic.

Various test-beds have been set up to study the behaviour of the individual components and the performance using different networking protocols. To achieve reasonable sizes for the test-beds typically several components had to be emulated. For example, every ROBIN has built-in datagenerators able to provide event fragments of arbitrary size at full speed. FPGA-based data-generators [GETB] [ETHERT] providing up to 128 ports and programmable NICs providing up to 16 ports were used to create network traffic with relatively simple patterns at high rate. More complex traffic pattern were created using PCs with special test programs. Using such systems, throughput in the order of 10% of the final system has been demonstrated for the baseline bus-based [BASEDF] readout architecture. Large-scale tests [LARSC] were performed on computing clusters with several hundred of machines, emulating different portions of the dataflow system up to the full size in most areas. The analysis of the congestion management of various switches indicates that at loads up to 60% of the nominal switch capacity the rate of lost message is virtually zero<sup>32</sup> for random traffic patterns, if the components are properly selected [ETHER]. Hence the capacity of the ATLAS dataflow network is tailored such that the load on the switches stays below this margin. However, care must be taken that the actual traffic patterns do not derive too much from a random distribution, such overloading certain switch ports. A potential problem is the event building step where an SFI needs to get data from a large number of sources. If the SFI would issue all data requests simultaneously the response packets would

<sup>30</sup> There are also switches which use a shared-memory instead of the cross-bar, however the required memory bandwidth poses a limit on the throughput and number of ports of such implementations.

<sup>31</sup> This is also called virtual output queuing.

<sup>32</sup> This is in line with the results obtained by LHCb (section 2.2).

certainly introduce head-of-line blocking in the switch with the associated effects, increased latency and packet loss and ultimately reduced system performance. For example, a message loss rate of 0.01% results in a performance reduction of 20% of the SFI [STANCU]. The implemented strategy at the SFI therefore uses a random delay after every data request.

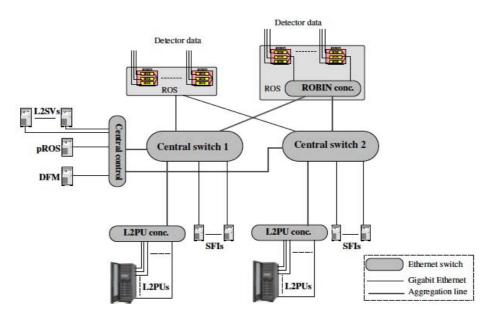

Another consideration for the design of the ATLAS dataflow network was the communication pattern – certain nodes communicate with each other and others do not. For example, the ROS nodes need to communicate will all L2PUs and SFIs but the SFIs never communicate with the L2PUs. Also, nodes of the same kind do not communicate with each other. The analysis of the corresponding bandwidth requirements shows that concentrating switches can be used in to aggregate ROSes or L2PUs. The small concentrating switches are then connected to the central switches, which also connect to the SFIs. The uplinks from the concentrators to the central switches use either several GE or a single 10GbE link. Figure 17 Shows the layout of the dataflow network using concentrator switches for the L2PUs, for the control nodes (DFM, L2SV and pROS) and for some of the ROSes. Two large central switches with a nominal capacity in the order of 250Gbit/s each build the core of the network. L2 and EB traffic is mixed in this scenario which provides also a certain degree of fault tolerance, as the system can continue to run even after the failure of a central switch, although at a lower rate. The alternative scenario where one central switch is used for EB and the other one for L2 was preferred earlier as it keeps the subsystems separate, however at the expense of missing flexibility and fault tolerance.

Figure 17: Dataflow network [STANCU]

The networks have been characterised using UDP and TCP and both protocols can be used concurrently in the system. In general, network latencies and message loss can be kept at an acceptable low level using standard – sometimes selected – network components [DFNET][DFROS]. Message loss on UDP based L2 data-requests is handled at the L2 application level, by re-requesting the data or

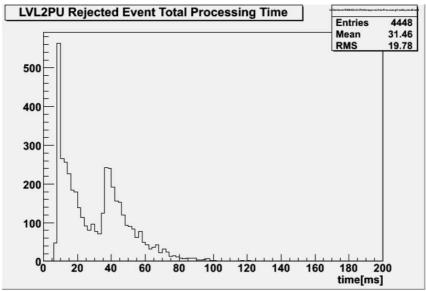

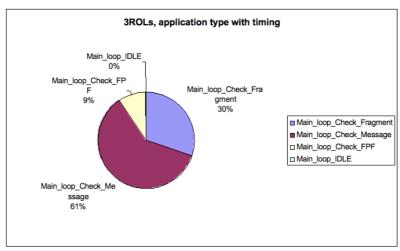

by generating a "forced-accept" decision. Message loss on multicast delete messages is handled at the ROS by a garbage-collection mechanism (see chapter 3.3.2). The buffering requirements introduced by the L2 trigger latency depends on the actual event (due to the sequential selection) and was estimated most recently to below 100ms in a relatively large test setup consisting of 134 ROS, 32 SFI and 130 HLT nodes, using 4.000 simulated events [L2PROC]. The distribution of the processing time is shown in Figure 18.

Figure 18: L2 processing times [L2PROC]

#### 3.3 **ROS**

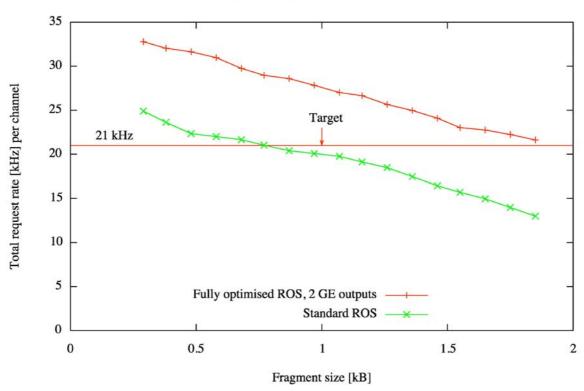

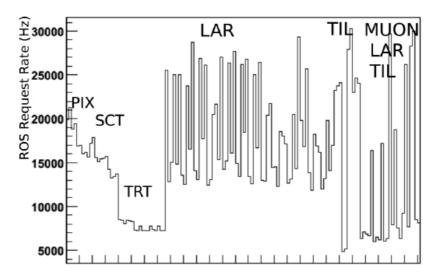

The ROS implements the buffering capabilities of the DAQ and the interfaces to the detector/L1 system on one side and to the HLT system on the other side. Event fragments are arriving from the detector/L1 system through the ROLs at the L1-rate of up to 100kHz and with a nominal bandwidth of 160MB/s per link. The actual fragment sizes depend on the type of sub-detector and vary typically between 400 and 1200 byte ([ATLASTDR], see chapter 8.4 ). Fragments generated for detector calibration purposes may be much larger (approx. 10 - 100kB), however occur at a very low rate. A full event is composed from all fragments corresponding to the same L1ID and has a typical size between 1MB and 1.5MB.

A baseline ROS architecture [Ibid.] has been developed, which concentrates a significant number of ROL channels into a single PC via the PCI-bus, satisfying the typical requirements. For a 12-channel ROS-PC the total L2 request rate varies between 300Hz for the TRT sub-detector and 18.6kHz for the electromagnetic calorimeter [Ibid.]. While under typical conditions the L2 and EF requests average to 6kHz per channel at a L1-rate of 100kHz the theoretical worst-case rate<sup>33</sup> on an individual channel is around 21kHz [MADROS]. The bandwidths related to the typical and worst-case request rates are in the order of 10MB/s and 33MB/s per ROL respectively. Enhanced ROS performance is achieved either by reducing the number of channels per PC or by employing additional networking connectivity

<sup>33</sup> The 21kHz are composed of 18kHz L2-rate plus 3kHz EB-rate. Under normal conditions it is very unlikely that the full L2-rate goes to a single channel.

bypassing the PCI-bus. The ROBIN – the only custom component of the ATLS dataflow apart from the RoIB – was designed to handle and buffer the input data with the flexibility to interact with the ROS-PC as well as directly with the dataflow system via a private network interface. In addition to the tasks above, which are related to the transport of detector data, the ROS interfaces to the configuration database and run control, the monitoring system and the detector control system (DCS) [ATLDCS]. The requirements on the ROS are summarised in a ROS user requirements document [ROSURD].

## 3.3.1 Event handling

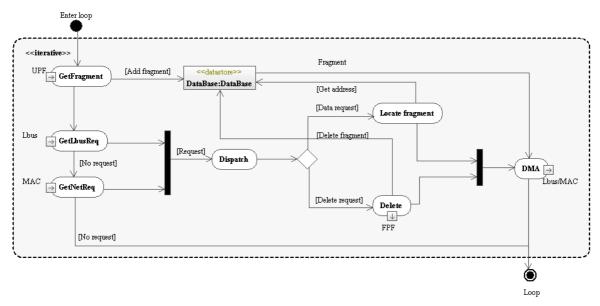

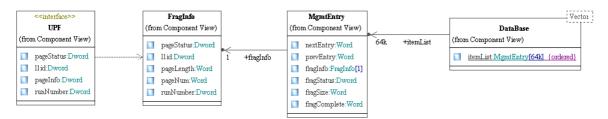

In ATLAS, events are identified by a 32 bit event number composed from a 24 bit identifier generated by the L1 trigger – the primary L1ID – plus an 8 bit event-counter-reset (ECR) value, incremented by the RODs upon the wrapping of the event identifier to 0. For simplicity the event number is normally and in this thesis referred to as L1ID. A design constraint limits the frequency of the ECR to the range from 0.1Hz to 1.0Hz. As a result, the maximum time between two zero-crossings of the event number is 256s, equivalent to 25.6 million events at a L1-rate of 100kHz. The minimum time is 25.6s. As a typical ATLAS run (a period of continuous operation) can extend to several hours the L1ID is not necessarily unique for all events and an additional mechanism needs to be put in place for event identification. As the minimum time covers the range of L2 and EF latencies the additional information is inserted at the event building stage by adding appropriate time-stamp information. At the ROS level the limited amount of buffering space requires to delete events as soon as possible. This is done by explicit delete messages distributed by the DFM, after the event has been rejected by the L2 or processed by the EF. To reduce the rate for delete messages they are sent out via a multicast mechanism typically in groups of 100.

As stated in chapter 3.2 the dataflow system is designed to minimise packet loss on the network switches, however losses are not fully prevented. While data requests are point-to-point interactions and can be protected by a reliable protocol this is not the case for delete messages. Lost delete message lead to orphaned fragments in the ROS and reduce the amount of buffer space available. While the event numbers at the ROS level restart at 0 after a maximum of 256s it cannot be guaranteed that all orphaned events will be replaced, as the L1ID does not have to be strictly sequential. Therefore, a "garbage collection" mechanism is required to clean up the buffer. The implementation of this mechanism requires to distribute the "oldest" valid L1ID in the dataflow system, which is piggy-backed to the delete messages. The loss of a message is detected by a jump in the message sequence numbers. Once a lost delete message is detected, the ROS compares the oldest valid L1ID to the most recent L1ID received from the ROLs, creates a range of valid L1IDs and deletes all fragments with event numbers outside of this range. The actual garbage collection procedure is executed on the ROBINs, which need to do a time-consuming scan of their entire buffer in order to build the list of stored fragments. To avoid excessive load the garbage collection is executed only when the buffers on the ROBIN have reached a certain filling level.

#### 3.3.2 Configuration and monitoring

Every ATLAS run is associated with a set of configuration parameters, stored in the global ATLAS configuration database. The range of parameters is very broad and includes calibration values for

detector front-end electronics, RoI-mappings and IP-addresses. A number of these parameters controls the behaviour of the ROBINs, distinguished into regular parameters and expert parameters. The regular parameters include buffer memory page sizes<sup>34</sup>, truncation limit, IP-address, channel identifier etc. The expert parameters include values which need to be modified in order to enable or disable particular functionality required to perform specific tests. During a regular run all expert parameters are set to their default values. The configuration of the ROBIN is controlled by the ROS-PC via a the normal requests/response mechanism.

The ATLAS TDAQ system requires a detailed online view of all activities in the system, in order to properly react to any malfunction. Thus, every subsystem has to provide functions related to operational monitoring. At the ROS level, operational monitoring gathers statistics information of received and lost messages, of buffer pages, processed fragments and of errors and histograms of buffer occupancies and fragment sizes. Most of this information is prepared by the ROBIN and transported to the ROS-PC via the regular requests/response mechanism.

#### 3.3.3 Baseline bus-based ROS

According to the baseline bus-based<sup>35</sup> architecture, the ROS is built from 150 PCs installed into racks with up to 12 PCs each (see Figure 19, front and rear view of rack). Each ROS-PC<sup>36</sup> attaches to 12 ROLs with a total input bandwidth of almost 2GB/s at a fragment rate of 1.2MHz. On the DAQ/HLT side the ROS has to handle the requests from L2 and EF for event data<sup>37</sup> and event rejection<sup>38</sup>. Connectivity to the L2 and EB networks is implemented with a 4-port NIC, which uses 1 port for each of the networks in the default configuration.

An additional NIC port is used for the operating system's network interconnection and for control and configuration. The bandwidths corresponding to the typical conditions are 60MB/s per network. The performance requirements as documented in the ATLAS TDR relate to fractions of the L1 input rate and translate for the standard ROS to 4kHz EB plus 12kHz L2 (RoI size of 1) at 100kHz L1 rate and 1kB fragments. A "hot-spot" condition was defined with 17% of L2 (RoI size of 2) and a fragment size of 1.4kB. Early measurements for a typical 12 channel ROS, equipped with data emulators, showed that the standard requirements were within reach (94kHz L1 rate achieved). For the "hot-spot" ROS either the EB rate had to be lowered to 2% or the L1 rate to 75kHz. As the "hot-spot" condition applies only to a few ROS-PCs attached to the electromagnetic calorimeter, the proposed solution at the time of the TDR was to reduce the number of ROBINs to 3 or even 2 in the few ROS-PCs affected.

<sup>34</sup> The buffer memory page size on the ROBIN has a default values of 2kB. Calibration runs for example can use larger pages.

<sup>35</sup> The baseline bus-based architecture uses the ROS-PC to interact with the DAQ/HLT system via the network and to select and collect event fragments from the individual channels of the ROBINs. An alternative switch-based architecture allows the ROBINs to directly communicate with some of DAQ/HLT components via a private network interface. This scenario is intended for special cases with more demanding performance requirements.

<sup>36</sup> The terminology of ATLAS TDAO sometimes uses ROS synonymous for ROS-PC.

<sup>37</sup> An L2 request addresses a single or a few channels, while an EB request addresses all channels.

<sup>38</sup> Event rejection (delete) messages are issued by a separate DAQ component, the dataflow-manager (DFM).

Figure 19: Racks with ROS-PCs\*

A further, even more demanding use case was defined after the TDR with a L2 request rate of 18 kHz on all channels plus 3kHz of EB, at 100kHz L1 rate. Going even beyond that, a ROS could theoretically be configured for 100% readout ratio, which would make it look somewhat like the CMS FRL unit (see chapter 2.1.1.4).

## 3.3.3.1 ROS-PC

The typical ROS-PC comprises a single CPU, 1GB of main memory, a 4-port PCIe NIC and 4 ROBINs, as shown in Figure 20. The mainboard<sup>39</sup> provides multiple PCI-X buses such that a

<sup>39</sup> Supermicro X6DHE-XB, http://supermicro.com/products/motherboard/Xeon800/E7520/X6DHE-XB.cfm

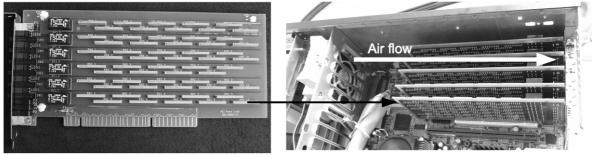

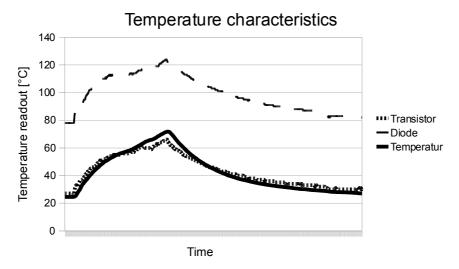

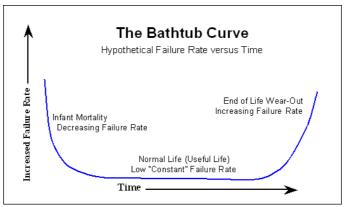

maximum of 2 ROBINs are connected to the same bus. This way, the maximum output bandwidth<sup>40</sup> of a ROBIN can be fully utilised. The NIC is placed on a separate PCIe bus. Both the motherboard and the chassis were selected after testing a number of different machines for performance and stable operation. Special attention has been paid to the quality of the power supply for PCI cards and to the cooling facilities. Concerning the power supply it was observed that several motherboards did not provide proper 3.3V if 4 ROBIN cards were installed. In some cases the voltage dropped below 3.0V, which triggered the under-voltage reset circuitry of the ROBIN and prevented the boards from starting. The thermal behaviour of the PC was tested by installing up to 5 custom "load-cards" (Figure 21) with configurable dissipation between 1W and 28W. The air-flow generated by the front fan of the case passes across all installed cards and exits through special openings at the rear of the case. The card temperature has been measured for different cooling conditions (case open/fan on, case closed/fan on, case closed/fan off) at a room temperature of 35°C. The temperature difference between the edges and the centre of the cards on one hand and between cards at different positions is in the order of 10°C for the situations where the fan is active, and the maximum temperature is around 65°C, which is acceptable considering the high room temperature. If the fan is turned off, the maximum temperature comes close to 80°C which is beyond the spec for many components. A regular monitoring of the temperature of the ROBINs can be done with the on-board temperature sensor. Also, there are sensors on the motherboard which can be used to detect failure of the cooling system in the PC.

Figure 21: PCI load board

## 3.3.3.2 Message passing

The ROS-PC runs a standard 32-bit Linux kernel, however with a patch<sup>41</sup> that enables applications to acquire a large amount of physically contiguous memory. The ROS application uses this memory to build a pool of fixed-sized memory pages as destination buffers for ROBIN responses. The communication between the main CPU and the ROBINs works in a messaging passing fashion: the application sends a request to the ROBIN and the ROBIN returns a response. The requests follow a standard format, which comprises the request code, a channel identifier, a sequence number, a destination address, a length field and eventually any data related to the request. Requests are written into a dual-ported memory area on the ROBIN, which is mapped into PCI memory space. A request descriptor identifying the length and the location of the request is written to a separate memory area, which is implemented by a FIFO on the ROBIN. The memory sizes of FIFO and dual-ported memory

<sup>40</sup> The output bandwidth of a ROBIN is 256MB/s, the PCI-X bus supports 512MB/s at 66MHz.

<sup>41</sup> The patch is called "bigphysarea", see e.g. http://lkml.indiana.edu/hypermail/linux/kernel/0411.1/2076.html

form a 32 entry deep hardware queue for requests from the ROS application. The number of available entries is maintained by the ROS application. To provide the destination addresses, the ROS application selects a buffer from the memory pool. A ROBIN configuration parameter assures that the actual fragment size cannot go beyond the size of the buffer area. This is done by setting an upper limit to the maximum number of fixed-size memory pages the ROBIN may use for any event fragment. Any fragment exceeding that size is truncated by the ROBIN during reception from the link.

#### 3.3.3.3 ROS Software

The ATLAS TDAQ online software is made up from a very large number of individual packets, which control trigger, DAQ, database access, monitoring etc. Alone the dataflow section, which is the main framework for the ROS and the ROBIN consists of 200 software packages. Among these, 27 deal with the ROS, 2 contain the application and boot code of the ROBIN and 1 covers the ROBIN FPGA code. Three of the ROS packages are relevant for the ROBIN and contain device drivers, a library and a number of applications. These packages are currently maintained by the CERN ROS software team and the group at RHUL. The Mannheim team has been and will be active in this area as well, however there is no manpower available at this time.

The main device driver performs the initialisation of the kernel structures related to PCI devices and makes the resources available to user applications. The driver also accepts interrupts from the ROBIN and provides the hooks for a corresponding user level interrupt handler. Additionally, it provides some debugging information which is available through the Linux "/proc" filesystem and which reports for every ROBIN card the serial number, the version number of FPGA and application code, the real-time status of the S-Link inputs, occupancies of the request queues and the values of the mailbox communication registers. Apart from the debugging interface the device driver is very generic and leaves most of the device specific functionality to a user level library and the associated applications. This approach makes the device driver less sensitive to modifications of the ROBIN functionality, which is advantageous as installing a new device driver has to be done by the system administrators while the applications can be updated by regular users.

A second device driver is available which provides a standard serial port to the host. This serial port is implemented at the hardware level by the the ROBIN FPGA, which in turn attaches to a serial port of the ROBIN processor. The purpose of this driver is to gain access to a ROBIN terminal port without attaching a cable. The latter is not practical, as the ROS-PC has only one internal serial port. Changing cables or adding an external USB-to-serial expander are not viable options under normal operating conditions. The serial interface is then used for testing and debugging purposes, for example the test suite (see below) uses this feature to set configuration values and to retrieve status and debug messages. There are two reasons to keep this driver separate from the main driver. Firstly, the functionalities are completely different and the serial port is only used for debugging and maintenance. Secondly, the serial driver interferes with the firmware upgrade procedure and must be unloaded beforehand. To minimise the chance for a system crash due to this interference, the serial driver is by default not loaded.

In addition to the two ROBIN device drivers there are other drivers used by the ROS software, for

example to allocate physically contiguous memory for the communication with the ROBIN.

The library used by the drivers and the applications contains functions related to the following areas:

- Allocation of boards and resources, memory mapping

- Access to the PLX PCI-bridge device

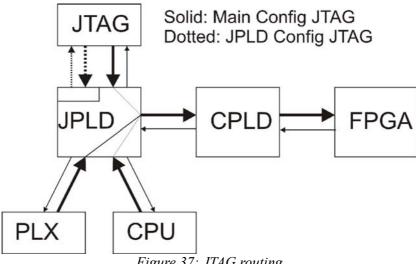

- JTAG access to FPGA and CPLD

- Exception and interrupt handling

- Handling of FPGA bitstreams, incl. FPGA configuration