# Steering electronics, module design and construction of an all silicon DEPFET module

Inauguraldissertation zur Erlangung des akademischen Grades eines Doktors der Naturwissenschaften der Universität Mannheim

vorgelegt von

Dipl.-Inf. Christian Kreidl

aus Worms

Dekan: Professor Dr. Heinz Jürgen Müller, Universität Mannheim

Referent: Professor Dr. Peter Fischer, Universität Heidelberg Korreferent: Professor Dr. Reinhard Männer, Universität Heidelberg

Tag der mündlichen Prüfung: 15. Dezember 2011

### **Abstract**

High energy physics experiments require detectors with an excellent imaging performance. The innermost part is often a pixel vertex detector with 2D position readout. The DEPFET pixel detector is an option for the International Linear Collider and will be used in the Belle II experiment at the SuperKEKB accelerator in Japan. Two barrel layers will be installed in a very confined space and hence, a dense packaging of sensors, readout and steering chips is mandatory. A hard radiation environment is influencing the electronics at the location close to the interaction point.

The steering chips are controlling the DEPFET imaging devices. They need to provide fast signals to read-out the large sensitive areas in a high speed. Two generations of steering chips are characterized and tested for their radiation hardness in this work. A converter chip was designed to operate the read-out chip stand-alone, until the data compression chip is ready.

The DEPFET detector modules will be build in the novel all-silicon approach, where the read-out and steering chips are mounted upside down directly onto the detector silicon. The silicon area is also used to interconnect the chips with the imaging devices and the cables. A thinned sensor area reduces the negative influences of the material on the particle tracks, but results in fragile devices.

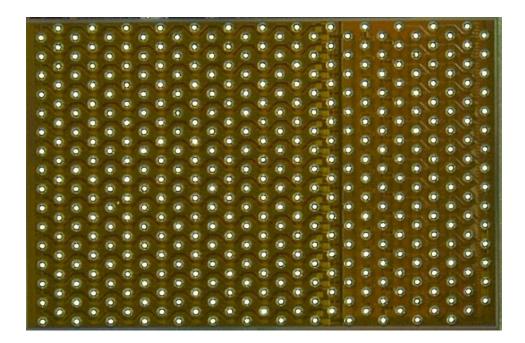

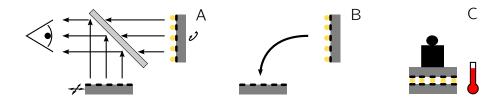

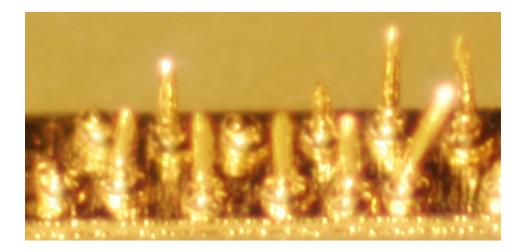

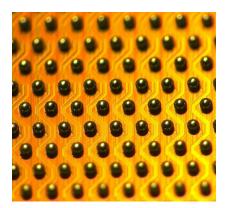

A flip-chip interconnection technology connects the chips to the detector and builds the all-silicon module. The technology has to be compatible with the thin and fragile DEPFET devices. Different flip-chip methods are evaluated in this dissertation. Many processes are only feasible for mass production and can't adopt to the flexibility requirements in research and development. Two processes, the gold-stud and solder ball bumping, meet the requirements and were deployed in the scope of this work. Several test prototypes have been successfully built with these processes.

Interconnecting the flip-chip mounted chips with the DEPFET array and the off-module cable connection on the detector modules is a further task addressed in this work. The special DEPFET technology limits the design complexity of the chip interconnection. A high power consumption of the read-out chips and the dense packaging of chips on the module are increasing the complexity furthermore.

In summary, this work has provided an important contribution to the development of the novel high resolution DEPFET vertex detector concept and has advanced the construction of the Belle II pixel vertex detector.

# Zusammenfassung

Experimente in der Hochenergiephysik benötigen Detektoren mit exzellenten bildgebenden Eigenschaften. Ein zentraler Teil ist oft ein Pixel Vertex Detektor zur 2D Positionsbestimmung. Der DEPFET Pixel Detektor ist eine Option für den International Linear Collider und wird beim Belle II Experiment am SuperKEKB Beschleuniger in Japan eingesetzt werden. Zwei zylindrische Lagen werden auf kleinstem Raum montiert und ein kompakter Aufbau des Sensors mit den Auslese- und Steuerchips ist dadurch nötig. Nahe am Wechselwirkungspunkt herrscht eine starke Strahlung, die die Elektronik negativ beeinflusst.

Die Steuerchips müssen schnelle Signale erzeugen, um den großen aktiven Bereich des DEPFET Detektors schnell auslesen zu können. Zwei Generationen der Steuerchips wurden in dieser Arbeit charakterisiert und auf ihre Strahlenhärte getestet. Ein Konverterchip wurde entwickelt, um den Auslesechip bis zur Fertigstellung des Datenkompressionschips betreiben zu können.

Die DEPFET Detektor Module werden ausschließlich aus Silizium-Komponenten aufgebaut. Die Auslese- und Steuerchips werden direkt auf das Detektor-Substrat montiert, welches auch zu deren Verdrahtung verwendet wird. Die sensitive Fläche wird gedünnt, um den negativen Einfluss des Materials auf die Teilchenspuren zu minimieren.

Die Flip-Chip Verbindungstechnologie wird verwendet, um die Chips und das Anschlusskabel mit dem Sensor-Substrat zu verbinden. Die Technologie darf die zerbrechlichen und dünnen Detektoren nicht zerstören oder negativ beeinflussen. Verschiedene Methoden wurden analysiert. Die meisten Prozesse sind auf die Verarbeitung von Wafern optimiert und für den Einsatz in der Forschung und Entwicklung ungeeignet. Zwei Verfahren, das gold-stud und das solder ball bumping, erfüllen die Flexibilitätsvoraussetzungen und wurden im Rahmen dieser Arbeit eingesetzt. Mehrere Test-Prototypen wurden mit diesen Verfahren erfolgreich hergestellt.

Die Verdrahtung der Flip-Chip montierten Chips mit den DEPFET Zellen und dem Kabel auf dem Detektor-Substrat ist ein weiterer Teil dieser Arbeit. Die DEPFET Technologie erlaubt nur eine begrenze Anzahl Metalllagen. Der hohe Strombedarf und die Dichte der Elektronik erschwert die Verdrahtung zusätzlich.

Diese Arbeit liefert einen wichtigen Beitrag zur Weiterentwicklung des neuen, hochauflösenden DEPFET Vertex Detektor Konzepts und hat den Bau des Belle II Pixel Vertex Detektors vorangebracht.

# **Contents**

| C | onten | ts      |                                          | i  |

|---|-------|---------|------------------------------------------|----|

| 1 | Intr  | oductio | on                                       | 1  |

| 2 | DEF   | PFET A  | Active Pixel Sensor Basics               | 3  |

|   | 2.1   | Radiat  | tion Detection                           | 3  |

|   |       | 2.1.1   | Charged Particles                        | 3  |

|   |       | 2.1.2   | Photons                                  | 6  |

|   | 2.2   | Semic   | onductor Sensors                         | 7  |

|   |       | 2.2.1   | The PN-Junction as a Detector            | 7  |

|   |       | 2.2.2   | Principle of Sidewards Depletion         | 9  |

|   |       | 2.2.3   | Radiation-Induced Effects                | 10 |

|   |       | 2.2.4   | Multiple Scattering                      | 13 |

|   | 2.3   | The D   | EPFET Detector                           | 14 |

|   |       | 2.3.1   | The DEPFET Principle                     | 14 |

|   |       | 2.3.2   | Charge removal                           | 16 |

|   |       | 2.3.3   | Building a Pixel Matrix                  | 18 |

|   |       | 2.3.4   | System Noise                             | 19 |

|   |       | 2.3.5   | Radiation Damage Effects                 | 19 |

| 3 | The   | DEPF    | ET as a Vertex Detector                  | 21 |

|   | 3.1   | The D   | EPFET Module Concept                     | 21 |

|   | 3.2   | Wafer   | Thinning                                 | 23 |

|   | 3.3   | The Ir  | nternational Linear Collider             | 26 |

|   |       | 3.3.1   | Vertex Detector Geometry for ILC         | 27 |

|   |       | 3.3.2   | Read-out and Timing                      | 28 |

|   |       | 3.3.3   | Module Power Consumption                 | 30 |

|   |       | 3.3.4   | Irradiation Damages and Radiation Length | 30 |

|   |       | 3.3.5   | Alternative Detector Concepts            | 31 |

|   | 3.4   | The B   | Belle II Experiment at SuperKEKB         | 35 |

|   |       | 3.4.1   | Accelerator Upgrade                      | 35 |

|   |       | 3.4.2   | Vertex Detector Geometry                 | 37 |

<u>ii</u> Contents

|   |      | 3.4.3   | Read-out and Timing                      | . 40 |

|---|------|---------|------------------------------------------|------|

|   |      | 3.4.4   | Module Power Consumption and Cooling     | . 42 |

|   |      | 3.4.5   | Irradiation Damages and Radiation Length | . 43 |

|   | 3.5  | Read-   | out Chips for DEPFET modules             |      |

|   |      | 3.5.1   | Curo                                     | . 44 |

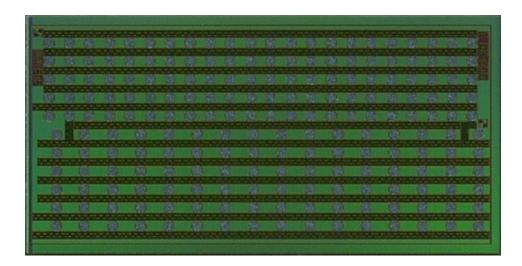

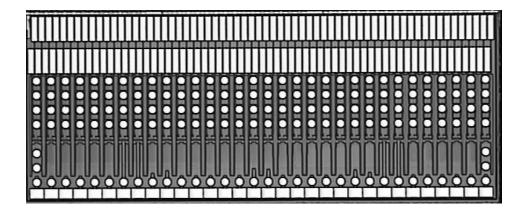

|   |      | 3.5.2   | DCDB                                     | . 44 |

|   |      | 3.5.3   | DHP                                      | . 46 |

| 4 | Rea  | d-out ( | Chip Design & Characterization           | 49   |

|   | 4.1  | DCD 1   | for ILC                                  | . 49 |

|   |      | 4.1.1   | Measurements                             | . 50 |

|   |      | 4.1.2   | Irradiation of DCD2                      | . 51 |

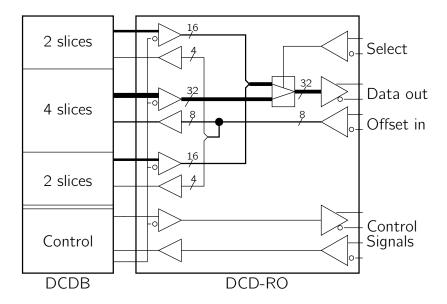

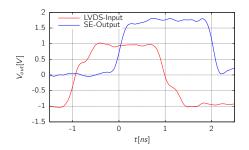

|   | 4.2  | DCD-I   | RO                                       | . 54 |

| 5 | The  | Switch  | her Steering Chips                       | 59   |

|   | 5.1  | Switch  | her3 for ILC                             | . 60 |

|   |      | 5.1.1   | Architecture and Design                  | . 60 |

|   |      | 5.1.2   | Sequencer                                | . 62 |

|   |      | 5.1.3   | Output Stage                             | . 63 |

|   | 5.2  | Switch  | her-B for Belle II                       | . 66 |

|   |      | 5.2.1   | Architecture and Design                  | . 67 |

|   |      | 5.2.2   | JTAG                                     | . 69 |

|   |      | 5.2.3   | Output Stage                             | . 69 |

|   | 5.3  | Test S  | Setups                                   | . 73 |

|   | 5.4  | Switch  | her3 Irradiation                         | . 74 |

|   | 5.5  | Switch  | her-B Irradiation                        | . 76 |

| 6 | Inte | rcon. 7 | Technology Developments                  | 79   |

|   | 6.1  | Wire b  | bonding                                  | . 79 |

|   | 6.2  | Flip-C  | hip Bonding                              | . 81 |

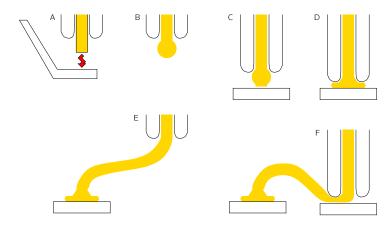

|   | 6.3  | Gold-S  | Stud Flip-Chip Bonding                   | . 83 |

|   | 6.4  | Solder  | Bump Flip-Chip Bonding                   | . 85 |

|   |      | 6.4.1   | Wafer Level Bumping                      | . 85 |

|   |      | 6.4.2   | Single Chip Solder Bumping               | . 87 |

|   |      | 6.4.3   | Reworking of Damaged Assemblies          | . 88 |

|   | 6.5  | Test S  | Structures                               | . 89 |

|   |      | 6.5.1   | Glass Substrates                         | . 90 |

|   |      | 6.5.2   | ILC Silicon Substrates                   | . 91 |

|   |      | 6.5.3   | ILC Full Size Demonstrator Module        | . 91 |

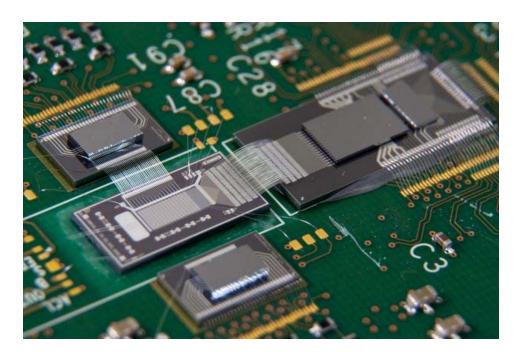

|   |      | 6.5.4   | Triple Chip Dummy Substrates             | . 92 |

Contents

|     | 6.6<br>6.7        |         | Two Metal Layer Test Chip  Test Structures in a 180nm Technology  Bonding Adapters  Dutions to other R&D Projects  HyperImage ToF-PET Readout Chip Wire Bonding  Capacitive-Coupled Pixel Detector  ISOSENSOR & ISOPIX | 94<br>96<br>98<br>99<br>100 |  |

|-----|-------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--|

|     |                   | 6.7.4   | XNAP Ceramic Interposer                                                                                                                                                                                                |                             |  |

|     |                   | 6.7.5   | Advanced Optical Cable                                                                                                                                                                                                 | 104                         |  |

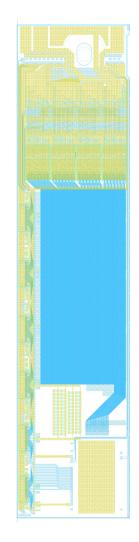

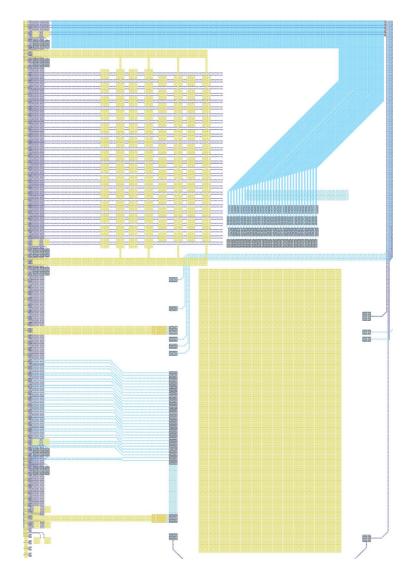

| 7   | DEF               | FET M   | Module Balcony Design                                                                                                                                                                                                  | 107                         |  |

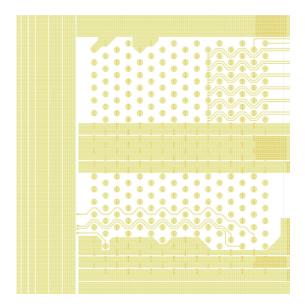

|     | 7.1               | PXD6    | Matrix Designs                                                                                                                                                                                                         | 108                         |  |

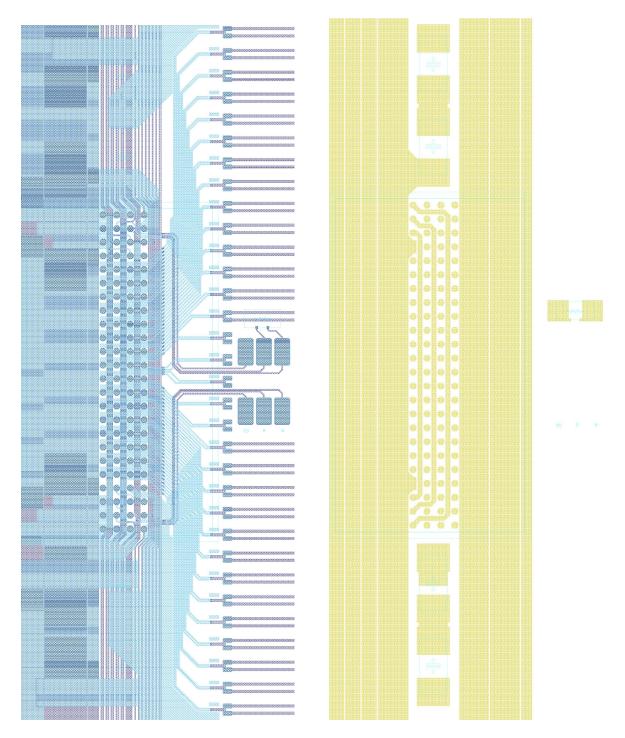

|     |                   | 7.1.1   | Technology Properties                                                                                                                                                                                                  | 109                         |  |

|     |                   | 7.1.2   | Wire Bond Matrixes                                                                                                                                                                                                     | 110                         |  |

|     |                   | 7.1.3   | Bump Bond Matrixes                                                                                                                                                                                                     | 111                         |  |

|     |                   | 7.1.4   | PXD6 Production                                                                                                                                                                                                        | 116                         |  |

|     |                   | 7.1.5   | First Measurement Results                                                                                                                                                                                              | 117                         |  |

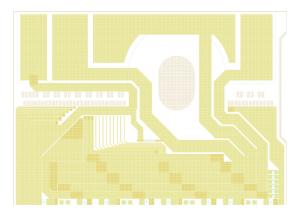

|     | 7.2               | Multi ( | Chip Module                                                                                                                                                                                                            |                             |  |

|     |                   | 7.2.1   | Switcher Balcony                                                                                                                                                                                                       |                             |  |

|     |                   | 7.2.2   | End of Stave                                                                                                                                                                                                           |                             |  |

|     |                   | 7.2.3   | Active Area Test Structures                                                                                                                                                                                            | 128                         |  |

| 8   | Sum               | mary a  | nd Outlook                                                                                                                                                                                                             | 131                         |  |

| Lis | st of             | Figures |                                                                                                                                                                                                                        | 133                         |  |

| Lis | List of Tables 13 |         |                                                                                                                                                                                                                        |                             |  |

| Bi  | bliogı            | aphy    |                                                                                                                                                                                                                        | 141                         |  |

# 1 Introduction

The search for the origin of the universe and the interactions that build our world has driven scientists for many centuries. The philosophical thought of all matter being build of a few indivisible particles has been formulated by the ancient Greeks, who called these particles atoms (Greek:  $\acute{\alpha}\tau o\mu o$ ). The first discovery of a particle in the beginning of the 19th century started the successful search in the field of particle physics. Many discovered particles could be explained as a combination of elementary particles. The theoretical Standard Model of particle physics has been formulated and predicted many elementary, subatomic particles. While most of them have been confirmed experimentally, the Higgs boson, as the key ingredient of the Standard Model, has not been discovered yet. It is required to give particles their mass. New particle accelerators reaching very high center of mass energies are needed to produce the rare events to confirm the existence of the Higgs. The Large Hadron Collider (LHC) is an energy frontier machine build at the European Organization for Nuclear Research (CERN¹). New particle discoveries are expected in proton-proton collisions with a center of mass energy of 14TeV.

Energy frontier machines can discover new particles, but lower energy accelerators are needed to study the properties of particles in detail. The International Linear Collider (ILC) is currently developed to provide such a high precision at the Terascale. Particles discovered at the LHC can be analyzed in more detail in the electron-positron collider at energies of up to 1TeV.

The questions of how the universe evolved and why it is dominated by matter are addressed by flavor physics at B-factories like the Belle experiment at the KEKB accelerator in Japan. The charge-parity (CP) symmetry needs to be violated in order to explain the dominance of matter over antimatter in the universe. B-mesons created in the asymmetric electron positron colliders are precisely measured and can give an insight on CP violation. KEKB has rather moderate center of mass energies of 10GeV, but provides a 50 times higher interaction rate compared to the ILC, which allows the observation of phenomena with high statistics to either further support the assumptions of the Standard Model or to unveil new particles and processes beyond it. The rare/precision frontier will be enlarged by the SuperKEKB, an upgrade of the KEKB accelerator. An upgrade of the Belle detector is also necessary in order to cope with the high luminosity of the SuperKEKB.

Semiconductor sensors can provide the required precision to the ILC and Belle II detec-

<sup>&</sup>lt;sup>1</sup>Conseil Européen pour la Recherche Nucléaire

tors. The main advantages of the semiconductor sensors, compared to other detector types like gaseous detectors, are a faster response time, a lower energy threshold and a smaller feature size. They allow the integration of many sensor devices on one piece of silicon and to obtain a high resolution image. Especially the DEPFET detector, with its integrated first amplification stage, achieves a spacial resolution of a few micrometers. The higher resolution demands a high density interconnection technique to connect the steering chips to the sensor and to transfer the sensor information to the readout chips. The detectors need to be placed as close as possible to the accelerator's interaction point to reconstruct the particle tracks as precise as possible.

A harsh radiation environment is influencing the detectors at the position close to the interaction point. They need to be read out more often in order to reduce the amount of false hits in a data set and to allow a precise track reconstruction. The steering chips need to provide fast control signals to the matrix and both, the readout and steering chips, have to be radiation hard. The results of the chip characterization and irradiation tests are presented in chapters 4 and 5.

A dense packaging of sensor, steering and read-out devices, together with cabling, cooling and mounting infrastructure is mandatory for an inner layer pixel detector. Particles passing through matter are interacting with nuclei and changing their trajectories. The amount of material has to be reduced in order to limit the number of interactions, resulting in small, thin and fragile devices. Read-out and steering chips have to be mounted on those fragile devices. The density requirements of such a novel all-silicon detector module can be accommodated by flip-chip mounting of the chips directly onto the detector silicon. This interconnection technology utilizes different conductive materials, such as gold or solder, to form the conductive paths between chips and substrate. Gold and solder ball placement processes have been evaluated and set-up during this thesis and the results are presented in chapter 6.

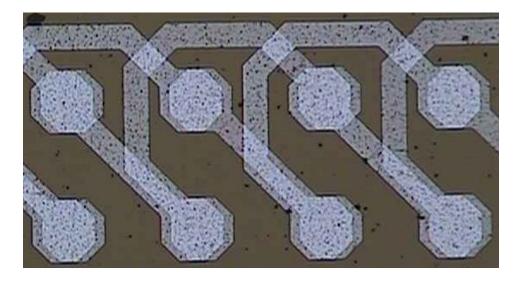

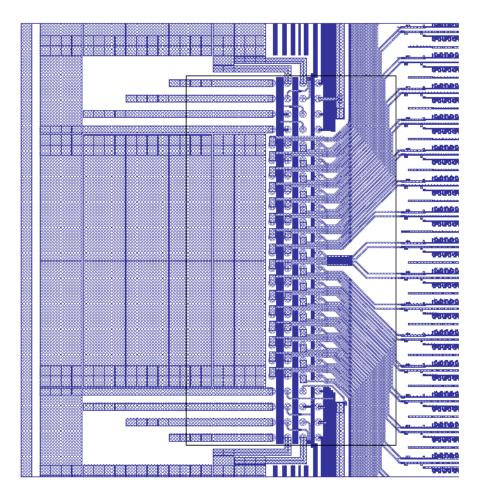

The detectors are arranged in concentric layers around the particle interaction point, limiting the size of the detector silicon. As most of its area is devoted to the imaging pixels, only a small fraction is available for mounting and interconnecting the read-out and steering chips to the off-module cable connection. Additionally, the DEPFET detectors are manufactured in an engineering process with a confined design complexity. Providing the high power and signal routing demands in such an environment is challenging. The results of the design efforts for the all-silicon module are presented in chapter 7.

# 2 DEPFET Active Pixel Sensor Basics

The DEPFET<sup>1</sup> is a monolithic active pixel semiconductor sensor with a very good signal-to-noise ratio. This makes the DEPFET an attractive device for spectroscopy applications or particle physics, where a high spacial resolution and low power consumption are needed. The principle of the DEPFET was shown by Kemmer and Lutz in 1987 [1].

Detectors built with semiconductor material have the advantage of a large signal-tonoise ratio, which allows the detection of low energy radiation. They also allow the integration of electronics within the detector. The short, low capacitance path from signal source to electronics enables the device to amplify the signals with low noise contribution. Hit detection or timestamp counter circuits are integrated in monolithic active pixel detectors.

DEPFET detectors are developed for X-ray imaging in the IXO<sup>2</sup>[2] astronomy project or for the European XFEL<sup>3</sup>[3] for atomic and molecular spectroscopy. They are also an option for the ILC<sup>4</sup> and for Belle II particle physics experiments as the inner layer vertex detectors. ILC is a  $e^+e^-$  linear accelerator, with energies up to 500GeV. Belle II is an asymmetric electron-positron collider to study B-physics.

### 2.1 Radiation Detection

Radiation is detected because of its interaction with matter. It looses its energy partly or completely through interaction processes while traversing through matter. The interactions create free electrons, either by direct or indirect processes, which can be detected as electrical signals. Depending on the type of radiation, different processes are involved. It is distinguishable between charged particles and photons.

# 2.1.1 Charged Particles

Charged particles interact with matter by different processes, like inelastic collisions with atomic electrons, elastic scattering from nuclei, emission of Cherenkov radiation and

<sup>&</sup>lt;sup>1</sup>Depleted Field Effect Transistor

<sup>&</sup>lt;sup>2</sup>International **X**-ray **O**bservatory

<sup>&</sup>lt;sup>3</sup>X-ray Free Electron Laser

<sup>&</sup>lt;sup>4</sup>International Linear Collider

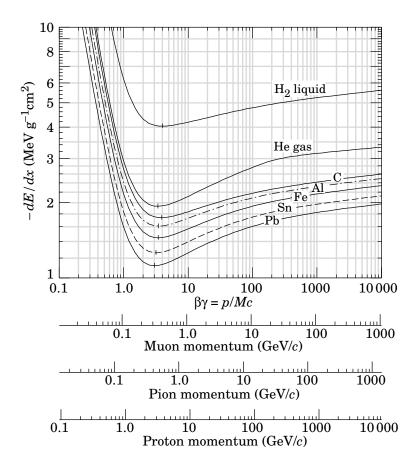

Figure 2.1: Mean energy loss in different materials as a function of particle momentum by the Bethe-Bloch formula. [4]

bremsstrahlung. The type of interaction of charged particles depends on their mass. Energy loss of charged particles heavier than electrons is mainly caused by inelastic collisions with atomic electrons causing ionization or excitation. In a single collision, only a small amount of kinetic energy is transferred. Due to the density of matter, the amount of collisions are high enough to loose a significant amount of energy. Electrons and positrons transfer most of their energy by bremsstrahlung. They emit a photon when they are decelerated by the electric field of an atomic nuclei.

The mean energy loss in matter of heavy, charged particles with an intermediate energy caused by ionization or excitation processes is described by the Bethe-Bloch formula[4][5]:

$$-\left\langle \frac{dE}{dx}\right\rangle = Kz^{2}\frac{Z}{A}\frac{1}{\beta^{2}}\left[\frac{1}{2}In\frac{2m_{e}c^{2}\beta^{2}\gamma^{2}T_{max}}{I^{2}} - \beta^{2} - \frac{\delta(\beta\gamma)}{2}\right]$$

where

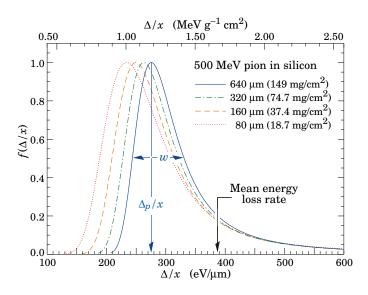

Figure 2.2: Landau distribution for different silicon thicknesses. [4]

$\frac{dE}{d}$  energy loss of the particle, usually given in  $\frac{eV}{g/cm^2}$

$K 4\pi N_{Av} r_e^2 m_e c^2 = 0.307075 MeV cm^2$

z charge of the traversing particle in units of the electron charge

Z atomic number of the absorption medium (14 for silicon)

A atomic mass of the absorption medium (28 for silicon)

$m_e c^2$  rest energy of the electron (0.511MeV)

$\beta$  velocity of the traversing particle in units of speed of light

$\gamma$  Lorentz factor  $1/\sqrt{1-\beta^2}$

I mean excitation energy (137eV for silicon)

$T_{max}$  maximum kinetic energy transferred to a free electron by collision

$\delta(\beta\gamma)$  density effect correction to ionizing energy loss for high particle energies

Figure 2.1 shows the mean energy loss for different absorber materials as a function of particle energy, calculated by the Bethe-Bloch formula. For low energies, the  $1/\beta^2$  term is dominant and the stopping power decreases to a minimum. This minimum is reached with particle velocities about 0.96 the speed of light. With further increasing energy, dE/dx rises again due to the logarithmic term. A particle with an energy in the minimum of the Bethe-Bloch formula is called minimum ionizing particle (MIP).

For thick absorbers, the energy loss probability distribution is of Gaussian shape centered around the mean value given by the Bethe-Bloch formula. However thin layers of matter, which are commonly used in particle physics, have a energy loss probability distribution

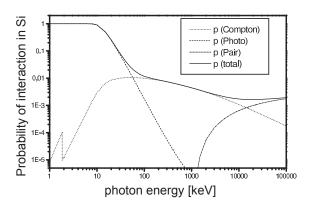

Figure 2.3: Probability of energy loss of a photon in silicon. [6]

with a long tail to higher energies. Fluctuations of energy loss for thin absorbers are described by the Landau distribution. Fast particles pass through the sensor, don't deposit all their energy, but generate  $\delta$ -electrons.  $\delta$ -electrons (also named knock-on electrons) are high energy free electrons which are ionizing themselves and thus create more charge by secondary ionization.

Figure 2.2 shows the Landau distribution for different silicon thicknesses. The most probable stopping energy in a  $75\mu m$  detector is  $\approx 18 keV$ , corresponding to  $\approx 4800e^-$ .

### 2.1.2 Photons

Photons are neutral and interact with matter differently than charged particles. The main interaction processes are:

- **Photoelectric effect:** The photon is absorbed by an atomic electron which gains the photon's energy. If its energy is higher than the electron's binding energy, the electron is ejected from the atomic shells. The free electron's kinetic energy is  $E = hf \varphi$ , where h is the Planck constant, f the frequency of the photon and  $\varphi$  the work function. The kinetic energy of this electron will be transferred by ionizing collisions to the absorber material.

- Compton scattering: A photon is scattered elastically on an electron and causes an energy transfer to the electron. The electron is then ejected from the atomic shell. The amount of energy transfer depends on the photon's energy and the scattering angle. The transfer is maximum for backscattering, when the photon is reflected.

- Pair production: The high-energy photon is converted into a electron-positronpair by interacting with a nucleus. A photon energy of at least twice the rest energy of an electron is needed:  $2m_ec^2 = 1.022MeV$ .

At energies below 60keV, the photoelectric effect dominates in silicon material. Higher energy photons predominantly interact through Compton scattering. Above 10MeV, pair production is dominant [7]. Figure 2.3 shows the probability of energy loss in silicon as a function of the photon's energy for the above mentioned interaction processes.

Photons are either absorbed or scattered by a large angle and thus removed from the photon beam. A photon that has passed through the material and didn't interact with it, hasn't lost energy. The beam doesn't loose energy, but intensity. The intensity loss of a photon beam passing through matter shows exponential behavior as a function of material thickness:

$$I(z) = I_0 e^{-\mu z}$$

where  $\mu$  is the absorption coefficient and depends on the density of the material and the beam energy. z is the thickness of the absorber.

### 2.2 Semiconductor Sensors

Semiconductor sensors have many advantages for detecting radiation or ionizing particles. The small band gap allows an electron to be lifted from the valence to the conduction band and thus creates an electron-hole pair with only a few eV. This is much lower than in gaseous detectors: A mean value of 3.63eV in silicon, compared to approximately 30eV in gas, is needed for ionization. Hence, a much better energy resolution and lower signal-to-noise ratio is achieved.

Semiconductor material has a high density, which results in a higher stopping power. The sensor thickness can be lower than in other detector types without decreasing the sensor performance. A fast charge collection time enables the device to be read out with faster frame times. The bulk of the detector can be fully depleted by using a high resistivity and weakly doped substrate. The generated charge cannot recombine and thus can be completely measured.

### 2.2.1 The PN-Junction as a Detector

The basic element of a silicon sensor is a pn-junction with a fully depleted bulk. In a fully depleted bulk, no free charge carriers are available and an electron-hole-pair, that has been generated by ionization, cannot recombine. It will be separated by the electric field and moves towards the electrodes, where a signal is measured.

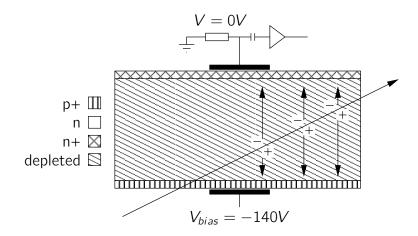

The device is created by using a weakly n-doped silicon material and implanting a highly doped p-type area on one side (see figure 2.4). The difference in majority charge carrier concentrations causes a diffusion of electrons into the p-doped region and holes into the

Figure 2.4: PN-junction as detector. [7]

bulk. A depletion zone starts to grow in which the bulk is positively charged, due to the missing electrons. The p-implantation is negatively charged, due to missing holes. This charge creates an electric field counteracting to the diffusion until it reaches an equilibrium. The corresponding potential is called *built-in voltage*  $V_{bi}$ .

The size of the depletion zone in equilibrium can be enlarged by applying a voltage with the same direction as the electric field. It is called reverse bias voltage, as it has the opposite polarity to the conducting direction of a pn-diode. The reverse voltage increases the electric field and removes more majority charge carriers. Due to the difference in doping concentrations, the depletion zone reaches much more into the weakly doped n-type bulk than into the p-doped region. By increasing the voltage, the depletion zone grows until the bulk is fully depleted.

The total width W of the depletion zone can be calculated as followed [5]:

$$W = \sqrt{\frac{2\varepsilon_0\varepsilon_{Si}}{e}\left(\frac{1}{N_A} + \frac{1}{N_D}\right)(V_{bias} + V_{bi})}$$

A typical donor concentration of the DEPFET detector is  $N_D \approx 10^{12} cm^{-3}$  for the bulk material and  $N_A > 10^{19} cm^{-3}$  for the acceptor concentration of the p-implantation. As  $N_D << N_A$  and  $V_{bias} >> V_{bi} \approx 0.6 V$ , the terms  $1/N_A$  and  $V_{bi}$  can be neglected. The required bias voltage to fully deplete a bulk of width W is:

$$V_{bias} pprox rac{eN_D}{2arepsilon_0 arepsilon_{Si}} W^2$$

For the above given donor concentration, a  $450\mu m$  thick silicon needs a depletion voltage of  $\approx 130V$ . However, voltage can be reduced to  $\approx 3.75V$  by using a  $75\mu m$  thin device.

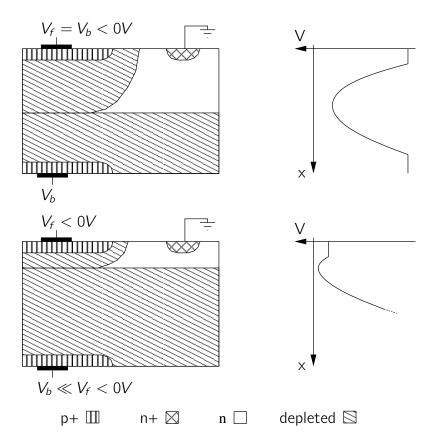

Figure 2.5: Principle of sidewards depletion. [7]

### 2.2.2 Principle of Sidewards Depletion

The principal of sidewards depletion has the advantage of creating a potential minimum for electrons within the bulk material by influencing the electric field.

This is achieved by creating highly p-doped implantations on both sides of the weakly n-doped material and adding a bulk contact at one side (see figure 2.5). The bulk contact is kept at ground potential, whereas both p-contacts are connected to a negative voltage. Depletion zones are reaching into the bulk from both pn-junctions. By applying the same voltage to both p-contacts, the potential minimum is in the middle of the material. In order to completely deplete the bulk from two sides, only a fourth of the bias voltage of a single pn-junction is required. Lowering the voltage on one side and increasing it on the other shifts the minimum towards surface with the lower voltage.

The Poisson-equation describes the potential perpendicular to the substrate surface[7]:

$$\frac{\delta^2 \Phi(z)}{\delta z^2} = -\frac{\rho}{\varepsilon_0 \varepsilon_r}$$

It is solved by:

$$\Phi(z) = \frac{\rho}{2\varepsilon_0\varepsilon_r}z(d-z) + \frac{z}{d}(V_b - V_f) + V_f$$

with the back side potential  $V_b$ , the front-side potential  $V_f$  and the substrate thickness d. The potential minimum is located at:

$$z_{min} = \frac{d}{2} + \frac{\varepsilon_0 \varepsilon_r}{\rho d} (V_b - V_f)$$

The position of the minimum within the bulk is defined by the front side and back side potentials.

### 2.2.3 Radiation-Induced Effects

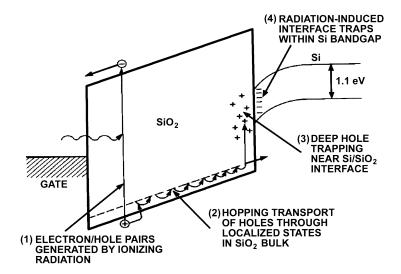

In MOS transistors and semiconductor sensors, radiation deteriorates the performance of the device. Sensors are affected by type inversion, an increase of leakage current and charge trapping. MOS transistors show a shift in threshold voltage, a reduced mobility of charge carriers and also an increased leakage current.

The bulk of semiconductor sensors is damaged by particles, which do not interact only with electrons and thereby create signals, but also interact with the silicon's nuclei. Silicon is a crystal and interacting particles will remove atoms from their lattice position. This creates crystal defects, that can be electrically active and change the detector's behavior.

In order to remove an atom from its lattice position, a recoil energy of 25eV is required. To provide this energy, an electron needs at least 260keV, protons and neutrons need only 190eV, because of their higher mass [5]. If the removed lattice atom gets enough energy transferred by the collision, it will also cause defects by secondary interactions. When the transferred energy exceeds about 2keV, the atom creates defects in a small area. These cluster defects are mostly created by neutrons, because they interact with the nuclei and are not scattered electromagnetically. Charged particles are screened by the lattice atom's electrons and thus create mostly point defects.

Non-ionizing energy loss (NIEL) is used as a measure in order to compare the damages caused by different particles at different energies. It describes the energy deposited in the material, that is not used for signal generation by ionization. Neutrons with 1 MeV are used as a reference. A hardness factor converts the physical fluence of a particle to the equivalent of 1 MeV neutron fluence.

Defects are able to move within the silicon material and create secondary point defects by combining with other defects. They can be stable and change the electrical properties of the material. It is also possible, that the defects anneal during their movement. Point defects and trapped holes near the  $Si/SiO_2$  interface create energy levels in the band

Figure 2.6: Energy band diagram showing the main processes of radiation-induced charge generation. [8]

gap, that allows electrons to switch more easily to the conduction band and thus create an increased leakage current.

Electrically active point defects influence the effective doping, which is the difference between n- and p-like doping effects. The defects act like p-doping and reduce the initial effective n-doping of the bulk. This allows the full depletion of the material with a lower reverse bias voltage. It decreases up to a flux of  $\Phi = (2-5)10^{12}cm^{-2}$  where the n- and p-doping effects cancel each other and the material behaves like intrinsic silicon. With a more increasing flux, the n-material starts to behave like p-doped material. This is called *type inversion*. The pn-junction is now at the  $n^+$ -side of the detector and depletion zone starts to grow from there.

Similar to all MOS transistors, the DEPFET is also susceptible to threshold voltage shifts caused by charge build up in the gate oxide. Ionizing radiation creates electron-hole pairs in the oxides. If a positive voltage is applied at the gate electrode, the charge is separated, the electrons drift towards the gate and the holes towards the  $Si/SiO_2$  interface. Due to the higher mobility of electrons  $(\mu_{n,oxide} \approx 20 cm^2/(Vs))$ , they are removed from the oxide within picoseconds. Holes are less mobile  $(\mu_{p,oxide} \approx 2 \times 10^{-5} cm^2/(Vs))$  and mostly remain near their generation point. They form a positive oxide-trap charge [8]. Other holes move through the oxide by hopping through shallow traps. Near the  $Si/SiO_2$  interface, some holes fall into long-lived trap states and contribute to the voltage shift. Others are exited into the silicon substrate. While hopping through the oxide lattice structure, they release hydrogen ions (protons), that also move to the  $Si/SiO_2$  interface and form interface-traps [9]. The effect is dependent on the bias voltage. If no bias is applied, the recombination of generated electron-hole pairs is most probable and thus less charge builds up in the oxide.

Figure 2.7: Multiple scattering of particle passing through matter. [4]

This additional charge necessitates compensation by an increased gate voltage, which results in the threshold voltage shift. Thinner gate oxides are less susceptible to threshold shifts, because the volume, where charge can be generated, is smaller. The thin gate oxides of deep sub-micron MOS technologies have very low threshold shifts:  $\Delta V_T = Q_{OX}/C_{OX}$  leads to a voltage shift, that is proportional to  $t_{OX}^2$ . These technologies are 'intrinsically' radiation hard, because tunneling removes trapped oxide charges.

Not only the gate oxide of a transistor is sensitive to radiation damage, but also the much thicker field oxide around the transistor. The charge trapped in this oxide causes a parasitic leakage path from the source- to the drain-region by creating a conductive path. Current flows outside the active, gate controlled transistor area, even if the transistor is switched off. They increase the static power consumption of an integrated circuit.

Interface states between Si and  $SiO_2$  result in an increased sub-threshold slope and a higher 1/f noise of the transistor.

Large concentration of trapped charge at the interface reduces the mobility of charge carriers in the transistor channel, which reduces the transconductance  $g_m$ . As a consequence, this decreases the drive capability of the transistor, degrades timing parameters and leads to a failure of the integrated circuit.

Oxide trapped holes are relatively stable, but may be removed through an annealing process, which can take hours or even years. Annealing is caused by tunneling and thermal excitation processes and is dependent on temperature, time and the applied electrical field. In tunneling, the hole is not removed, but neutralized by an electron tunneled from the silicon into the  $SiO_2$ .

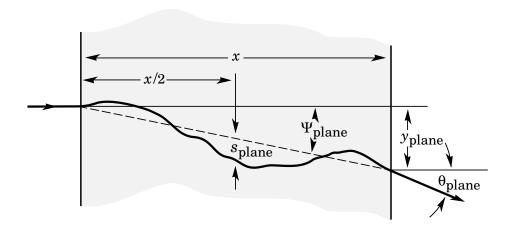

### 2.2.4 Multiple Scattering

Multiple scattering is deteriorating the particle track reconstruction precision, as it influences the particle trajectory. Many elastic scatterings in the electric field of nuclei with small angled deflections cause large deviations from the original trajectory. Particles exit the material at different positions and with different angles (figure 2.7). Scattering is a stochastical process, where the width of the projected deflection angle can be approximated by a Gaussian distribution. It is dependent on the thickness x of the material, given in radiation length  $x/X_0$ , the momentum p, velocity  $\beta c$  and the charge number of the particle z:

$$\Theta_{plane} = \frac{13.6}{\beta cp} z \sqrt{x/X_0} [1 + 0.038 \ln(x/X_0)]$$

Radiation length is the length of matter traversed by an electron or photon, which interacts with the material. It is the mean distance where an electron looses all but 1/e of its energy by bremsstrahlung and 7/9 of a photon's mean free path<sup>5</sup> between pair productions. It is often given in  $g \, cm^{-2}$ . The radiation length in cm can be calculated by dividing this value through the material's density:  $9.37 \, cm$  for silicon,  $0.33 \, cm$  for gold and  $1.21 \, cm$  for tin. [4]

The thickness of a material is often expressed in the percentage of its radiation length. A  $450\mu m$  thick silicon detector uses  $0.48\%~X_0$ . A reduction in terms of radiation length is desired in order to minimize the particle track deflection. In particle detectors, a maximum radiation length of  $0.1\%~X_0$  per layer is mandantory.

<sup>&</sup>lt;sup>5</sup>average length between collisions

Figure 2.8: Sketch of a DEPFET with drain readout. [10]

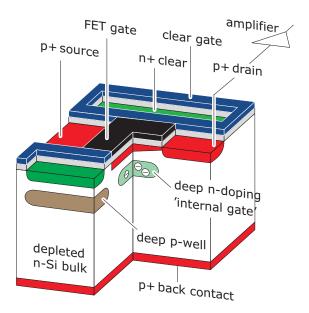

### 2.3 The DEPFET Detector

The DEPFET detector is a monolithic active pixel sensor. In hybrid pixel detectors, the first amplification stage is located in an additional chip. However, a DEPFET has an amplification transistor integrated in every pixel. The extremely small input capacitance of this transistor allows a low noise amplification at room temperature. A fast and complete charge collection is made possible by the drift in a fully depleted bulk.

# 2.3.1 The DEPFET Principle

The DEPFET uses a pn-junction with a fully depleted bulk for signal generation and sidewards depletion to modulate the electrical field. A p-MOS signal amplification transistor is integrated in the front-side of the high resistivity n-type detector material. The highly p-doped back side implantation and the p-implantation of the transistor are used for sidewards depletion. The  $n^+$ -contact needed for depletion is not shown in figure 2.8 and is located outside the sensitive area. The potential minimum for electrons is shifted towards the front side, to  $\approx 1 \mu m$  below the surface. A structured  $n^+$ -implant is located beneath the transistor channel and creates the potential minimum, which collects the signal electrons.

Charged particles create electron-hole pairs in the fully depleted bulk. The holes drift towards the back side contact, while the electrons move to the front side and accumulate in the potential minimum below the transistor channel. The signal charge, stored in this deep n-implant, modulates the transistor channel and can be considered as an *internal*

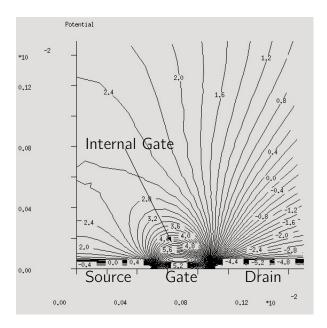

Figure 2.9: Equipotential lines of the electric field in the DEPFET detector bulk, showing the source-gate-drain region with the internal gate. [11]

gate. Figure 2.9 shows the equipotential lines of the electric field in the transistor region and the potential minimum of the internal gate. The change in transistor current dI is proportional to the change of signal charge dQ in the internal gate and defines the internal amplification  $g_q$ :

$$g_q = \frac{dI}{dQ}$$

The devices with a standard channel geometry show a  $g_q$  of approximately  $400pA/e^-$ . The electric field in the depleted region collects the charge in the internal gate within less than 60ns [10].

To read out the signal modulated by the internal gate, the DEPFET is switched on by the external gate of the transistor. As a readout is non-destructive, a DEPFET can be considered as an integrating device and can be read out multiple times without loosing signal information. The DEPFET transistor doesn't need to be switched on during signal collection, because the drift of signal charge into the internal gate is not influenced by the external gate. This allows a low power dissipating operation and makes an active cooling of a DEPFET detector obsolete.

Figure 2.10: Charge removal from the internal gate by a clear pulse on the clear contact.

### 2.3.2 Charge removal

As the readout of the DEPFET is non-destructive, means of removing charge from the internal gate are necessary. The internal gate will fill up by either signal or thermally generated electrons (leakage). The sensor gets insensitive to new signal charge, if the internal gate is not cleared.

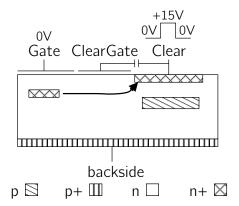

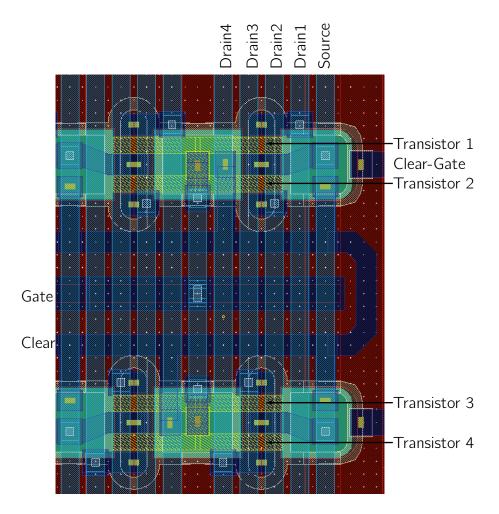

Figure 2.10 shows a cross section of the DEPFET transistor with a clear and a clear-gate structure. A highly doped n-type implantation is used as a potential minimum for electrons and as a electrical contact for the clear voltage. It is located near the internal gate. The charge stored in the internal gate is removed through applying a high positive voltage on the clear contact. The electrons in the internal gate are attracted by the high voltage, drift towards the clear contact and are then removed.

A complete charge removal is crucial, because remaining charge will contribute to the noise value of the detector. To lower the potential barrier between clear contact and internal gate, a *clear-gate* structure is introduced. It can be held at constant potential or can be pulsed. The pulsing may be realized by capacitively coupling the clear signal to the clear-gate structure using the parasitic capacitances of the layout.

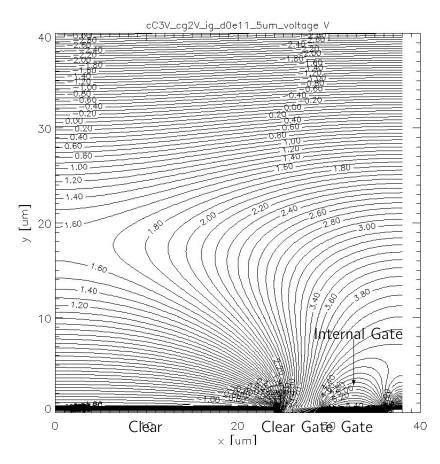

Electrons generated by ionization drift in the depleted bulk along the electric field. They aren't exclusively attracted by the potential minimum of the internal gate, but also by the  $n^+$  implantation of the clear contact. Charge drifting into the clear does not influence the transistor current and is lost. To avoid this incomplete charge collection, a p-type implantation is created underneath the clear contact. It provides a potential barrier for electrons and shields the clear contact. This assures a complete charge collection. Figure 2.11 shows the equipotential lines in a Clear-ClearGate-Gate region. The potential barrier shielding the clear contact is located at a depth of  $18\mu m$ .

The DEPFET is insensitive during a clear cycle, because signal charge drifting into the internal gate is immediately removed.

Figure 2.11: Equipotential lines of electric field in the DEPFET detector bulk showing a Clear-ClearGate-Gate region. [11]

Figure 2.12: DEPFET matrix with current read out and steering of gate and clear signals. [10]

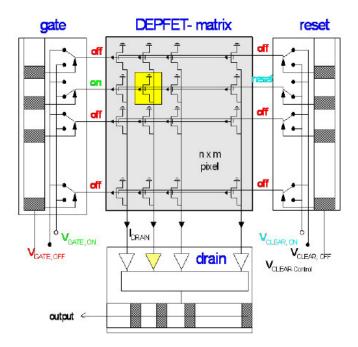

### 2.3.3 Building a Pixel Matrix

Single DEPFET cells are arranged regularly to build a pixel matrix. The clear and gate signals of the DEPFETs are connected row-wise and the drain signals are connected column-wise (see figure 2.12). The source voltage is distributed to all cells of the matrix (not shown in figure).

This connection scheme is possible, because the DEPFET is an integrating device and doesn't need to be read out continuously. For a continuous read out, every pixel would need it's own readout electronics, that lead to a high power dissipation. An active cooling would be required, but often is not possible in the space restricted area of the particle accelerators.

The matrix is read out row-wise. All transistors of a row are enabled by the common external gate signal. Signals, that are modulated by charge in the internal gate, can be read out by the electronics connected to the end of the drain lines. Clearing is also a row-wise operation. Two different readout modes exist:

**double sampling** After the signals of a row have been read out, internal gates are cleared and the row is re-read. The first read out value contains the signal and the baseline of the DEPFET cell. The second value contains only the baseline, if the clear has completely removed all charge. A baseline-free signal can be determined by subtracting the second from the first value.

single sampling The baseline of the matrix needs to be read out before any signal data is taken. It is stored for each pixel, to allow the subtraction of the baseline later on. They need to be updated regularly, as the baseline values of the matrix may change with time. Baseline compensation can be done in the readout chip, demanding on-chip memory to store the baseline values, or off-line in the analysis software.

Reducing the number of control signals, by grouping adjacent pixel rows, speeds up the frame readout. The number of drain lines has to be increased by the same factor, to read out the grouped rows in parallel. The data rate and the complexity of the readout electronics increases, but this also shortens the frame readout time.

### 2.3.4 System Noise

The noise of a system is a critical factor, as it influences its physics performance. A higher noise decreases the capability to detect low energy signals and lowers the spacial resolution of the detector. The noise value is often converted into *equivalent noise charge* (ENC), which describes the signal charge at the detector input needed to create the corresponding noise value. In case of the DEPFET, the ENC corresponds to the number of electrons in the internal gate.

$$ENC^2 = \frac{I^2}{g_a^2}$$

converts a current noise into ENC. Different processes are involved in the generation of noise in the DEPFET system:

**Thermal noise** is created by the thermally induced motion of charge carriers in a conductor.

**Shot noise** is a leakage current created by a random generation of electron-hole pairs in the sensor.

**Flicker noise** Charge trapped in the gate region influences the transistor current. The noise spectrum has a frequency dependence of 1/f. Flicker noise is also called 1/f noise.

To limit the influence of 1/f noise, the bandwidth of the read-out circuit has to be limited at low frequencies. The  $450\mu m$  thick devices shows a S/N > 110 [12].

# 2.3.5 Radiation Damage Effects

Radiation damage effects on the DEPFET transistor are mainly a shift of the threshold voltage, a build up of states at the interface between Si and  $SiO_2$  and a reduction of the transconductance  $g_m$ .

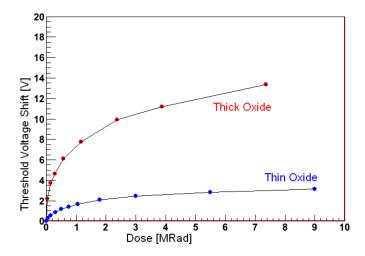

Figure 2.13: Threshold shift of a DEPFET transistor for 2 different gate oxide thicknesses after irradiation up to 9Mrad. [13]

The DEPFET test-structures show a shift in threshold voltage of  $\approx 13V$  after an irradiation of 7.5Mrad ionizing dose. The effects of ionizing radiation on the DEPFET can be reduced by a thinner gate oxide. However, the oxide thickness also affect other parameters like the internal amplification. Figure 2.13 shows the threshold voltage shift as a function of radiation dose for thick and thin oxides on DEPFET test-structures. The threshold shift has a great influence on building the system and can be reduced to  $\approx 3V$  by using thinner oxides. All components need to be able to cope with this shift. The specially build power-supplies need to provide a wider voltage range and the steering chips have to be designed in a technology which is able to handle these voltages.

Radiation effects on the steering chip will be discussed in chapter 5. Irradiation results on the read-out chip DCDB are not available at the time of writing.

# 3 The DEPFET as a Vertex Detector

In high-energy physics, detector systems consist of many sub-detectors which are used to detect the interaction products. Typically, a calorimeter is used for energy measurements, a tracking device measures the particle momentum in a magnetic field and the vertex detector determines the primary interaction point and secondary decays.

A vertex detector is the innermost detector, located closest to the interaction point of the accelerated beams. It consists of several cylindrical layers of sensors surrounding the interaction point and should be a pixel detector (2-dimensional device) with a high spacial resolution. Their distance to the interaction point should be minimal in order to reconstruct a vertex with a high resolution, by extrapolating the hit points in the layers of the detectors.

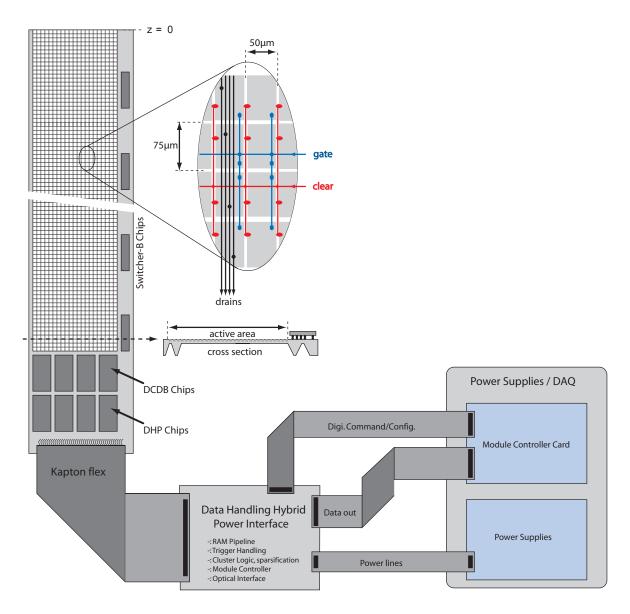

# 3.1 The DEPFET Module Concept

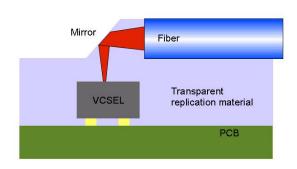

The steering of the gate and clear signals and the digitalization of the charge information is done by specially designed silicon chips. To meet size, material budget, speed and noise goals, the chips have to be located close to the matrix. The chips can be directly connected to the matrix by wire- or bump-bond techniques or by an intermediate layer of PCB<sup>1</sup>, silicon or a kapton based flex board. The control, data and power lines of all components of the detector system need to be interconnected and routed to a connection point. From there, a cable connects the system to the data acquisition (DAQ) and power supplies. This assembly of detector, steering and read out chips, routing and outside connection is called a module.

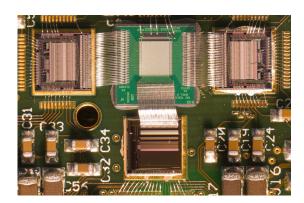

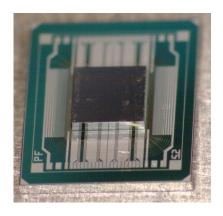

Figure 3.1 shows a photograph of the hybrid PCB 'S3A' with the 2 *Switcher-2B* steering chips at the left and the right of the DEPFET matrix. The readout chip *Curo* is located below the matrix. The hybrid PCBs are used for testing and characterization of the DEPFET matrix and the chips. A FPGA board is connected to this PCB, which communicates with the PC, configures and controls the chips and transfers the digitized DEPFET signal data to the software.

Using PCBs to build a detector system is the first step, but often a PCB cannot be integrated into a particle accelerator. The space available for a vertex detector module,

<sup>&</sup>lt;sup>1</sup>Printed Circuit Board

Figure 3.1: Switcher-2B steering chips, matrix and Curo readout chip on 'S3A' hybrid PCB. [14]

Figure 3.2: Futuristic sketch of a DEPFET module. [15]

located close to the interaction point of the particle accelerator, is minimal. The thickness of the PCB material and its components is enlarging the radius, increasing multiple scattering and deteriorating the physics performance of the detectors. A thin and small solution is needed.

### The All-Silicon Model

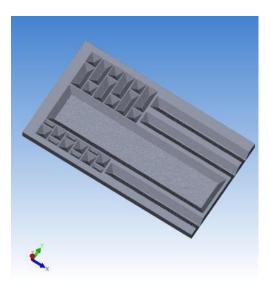

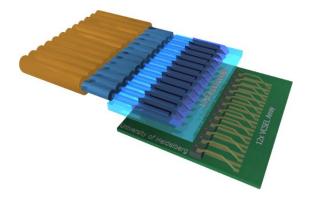

By enlarging the silicon size of a DEPFET sensor, while keeping the size of the active area constant, space can be created for directly mounting the steering and readout chips onto the detector silicon and for routing the interconnection and power traces. On a highly integrated and densely populated area of such all-silicon modules, the routing of a huge amount of signal and power connections is a difficult task. The components, located on the detector silicon, must not influence the detector or the electronics operation.

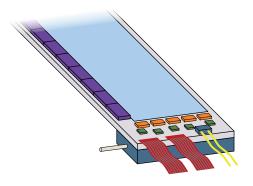

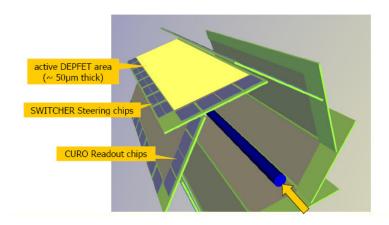

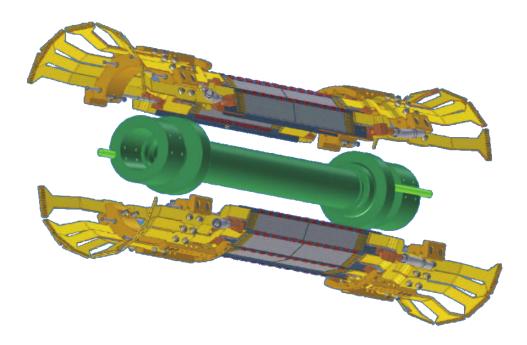

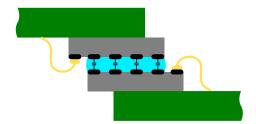

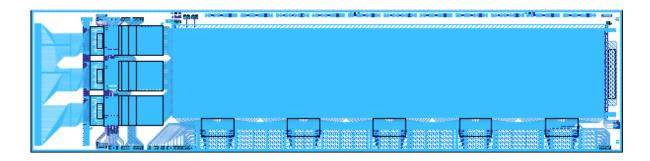

Figure 3.2 shows a sketch of the module concept. The steering chips are located on the long side of the detector, while the readout chips are mounted on the short end. This setup results in short and low capacitance matrix steering signals, which can be charged

quickly. A high capacitive load on the drain lines is not as limiting as on the control lines, because the DEPFET is operated in drain read-out mode, yielding to a current signal.

Control, data and power lines have to be connected directly to the silicon, the module is mounted on a support structure, which is also used for actively cooling the readout chips. By thinning the silicon of the detector and the chips, the material budget of the module can be reduced furthermore. For interconnecting the chips with the detector module, the flip chip technology has been chosen. Details on interconnection will be presented in chapter 6.

### **Cooling**

The integrated circuits, the leakage current of the detector and the currents flowing in signal and power traces are heat sources, that often need to be actively cooled. With increasing temperature, the module expands and the pixel positions of the detector change relative to the accelerator's interaction point. This influences particle track reconstruction negatively. Another effect is thermal runaway, where an increasing temperature increases the leakage current, which itself generates more heat. But cooling of an inner layer detector, surrounded by many more detectors, is not easy, as the area for installing the module's cooling is confined. The pipes for the cooling medium and the means of heat transfer must not significantly increase the material budget of the active volume. In the closed volume of the pixel detector the heat cannot escape and the temperature will rise. The heat has to be actively removed, because air cooling in detectors with a high power density is not sufficient. Therefore, cold liquid or gas has to be used to remove the heat close to the source.

The modules have to be supported by a stable mechanical mounting solution, which also has to be minimized in terms of material budget. The mounting structure can also be used as a cooling element, because the modules can transfer heat directly to it.

# 3.2 Wafer Thinning

The multiple scattering effect, that influences a particle's track while passing through matter, should be minimized. It lowers the impact parameter resolution for low energetic tracks. However, thinning the sensor material is not only improving the material budget, but also is decreasing the detector's signal-to-noise ratio.

Thinning silicon devices on wafer level is a commercially established process, where the unused back side of the device is removed by mechanically lapping and chemically etching. The DEPFET technology needs a back side implantation for a complete depletion of the sensor's volume. Processing the back side implantation after thinning the device to less than  $100\mu m$  is difficult, because the thin silicon foil might be damaged. A different

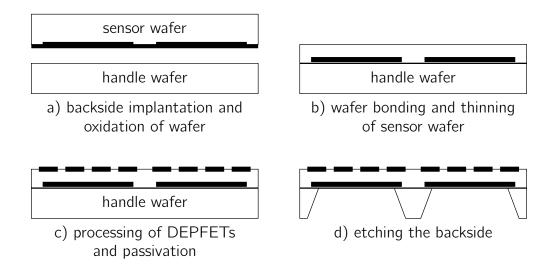

Figure 3.3: Thinning steps of back side processed DEPFET sensor wafers.

thinning technology has been developed at the MPI Semiconductor Laboratory in Munich, where the DEPFET structures are completely processed before the thinning is applied.

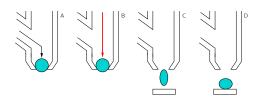

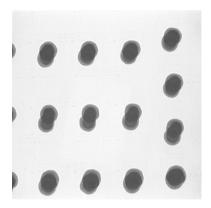

Figure 3.3 illustrates the thinning process. First, the back side is processed on a high grade sensor wafer and then oxidized (a). The back side of this wafer is then bonded by direct wafer bonding to a handling wafer and the sensor wafer is thinned to the desired thickness by CMP<sup>2</sup> (b). The DEPFET structures are processed on the thinned sensor wafer (c). Afterwards, the thinning mask is applied to the handling wafer and the silicon is removed by anisotropic etching, which stops at the oxidized layer (d).

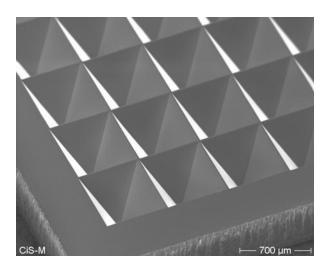

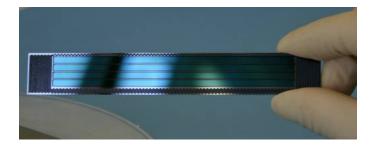

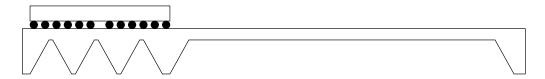

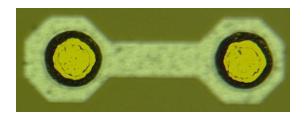

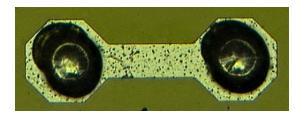

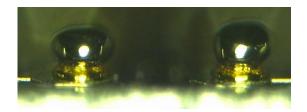

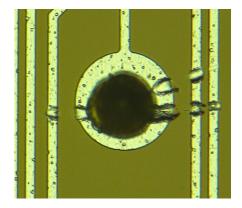

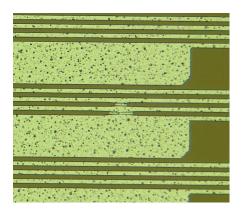

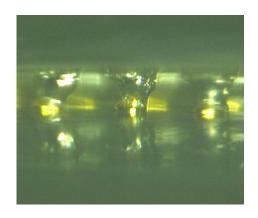

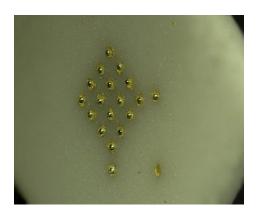

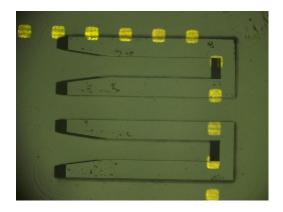

The support frame of the module is needed to mechanically support the thin active area and carry the steering chips. It allows to build a thin all-silicon module without glueing the thin silicon onto a support structure. Different temperature coefficients of silicon and support material could cause problems, which can be avoided in an all-silicon approach. The silicon support frame is partially thinned to further reduce the material budget of the detector. Figure 3.4 displays a hole pattern etched into the frame, which reduces the material by 33%. The thinned material is less stiff and a gravitational sag of  $20\mu$  along the long side of the module has been observed [16]. The support frame makes the module stiff enough to be handled by hand. Figure 3.5 shows a module with a size of  $10cm \times 1.3cm$ , where the active area is thinned down to  $50\mu m$ . The support frame is  $450\mu$  thick and thinned with the presented hole pattern. In figure 3.6 is a side view of a thin module with an attached steering chip shown.

<sup>&</sup>lt;sup>2</sup>Chemical Mechanical Polishing

Figure 3.4: Photograph of the hole pattern of the thinned balcony. [12]

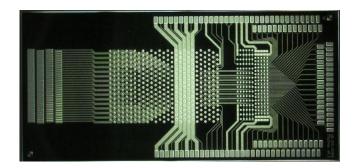

Figure 3.5: Photograph of a  $10cm \times 1.3cm$  mechanical sample with a thin active area and a hole pattern in the support frame. [17]

Figure 3.6: Schematic side view of a thin module with a hole pattern in the support frame and a steering chip attached by bump bonding.

### 3.3 The International Linear Collider

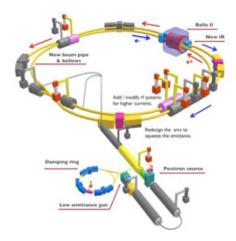

Figure 3.7: Schematic layout of the ILC linear accelerator. [18]

The currently running Large Hadron Collider (LHC) at CERN is a proton-proton collider with center-of-mass energies of up to 14TeV and a luminosity (a measure of collision rate) of up to  $10^{34} cm^{-2} s^{-1}$ . It is currently running with energies of 7TeV and a luminosity of  $10^{32}cm^{-2}s^{-1}$ . Physicists were able to validate aspects of the Standard Model of particles and forces [19]. New Physics beyond the Standard Model might be discovered with this collider. The discoveries made should be enhanced with more precise measurements. A hadron collider can't provide this precision, as it is limited by the uncertainty of the interaction's initial energy. A lepton collider is needed, as lepton collisions have a well defined initial state and all of their center-of-mass energy is available at the primary collision. The ILC is planned to provide this high precision by electrons colliding with positrons at energies between 90GeV and 1TeV.

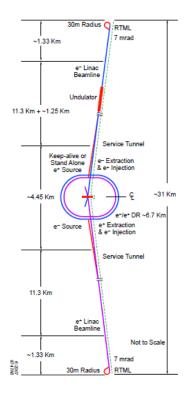

Two major concepts of building the accelerating part of a collider exist: the circular and the linear approach. In a circular collider, particles are accelerated in a ring and are gaining energy in every turn. They are brought to collision after reaching their target energy. The particles are loosing energy by synchrotron radiation, which is emitted when they are forced on a circular path. This energy loss is proportional to  $1/m^4$

and is significant at high energies for light particles like electrons. Therefore, the concept of **lin**ear **ac**celeration (linac) is introduced. The particles start at two different places, are accelerated on a straight line and are brought to collision. In circular accelerators, the particles are accelerated at one segment of the circle and reach the target energy after multiple circulations. A linear accelerator has to reach the target energy by a single passage. The particle is accelerated among the full length of the beam line. Figure 3.7 shows the low energy damping rings with 6.7km circumference in the middle, from which the particles are fed to the ends of the two main linacs. From there, they are linearly accelerated on a length on  $\approx 11km$  per side. Prior to the collision in the interaction point in the middle, the beams are focused to a size of  $639nm \times 5.7nm$ .

The ILC uses the superconducting technology to accelerate the particles. 16000 RF cavities are installed and operated at 1.3GHz with an accelerating gradient of 31.5MV/m per cavity. They are build of niobium instead of copper, which has a factor of  $10^6$  lower surface resistance. This leads to a much lower power consumption, even if the energy needed for cooling to superconducting temperature is taken into account. An electrical power of 230MW is required to reach the luminosity of  $2\times10^{34}cm^{-2}s^{-1}$ . The accelerator

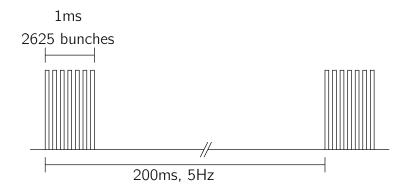

Figure 3.8: ILC beam timing with 2625 bunches within 1ms and 199 ms pause.

has a repetition rate of 5Hz with a beam pulse length of 1ms and a 199ms pause (see figure 3.8). The 1ms beam pulse contains 2625 bunches with  $2 \times 10^{10}$  particles per bunch, resulting in an average beam current per pulse of 9mA. An accelerator length of 31km is mandatory to reach a center of mass energy of 500GeV. The length has to be extended to reach 1TeV. [18]

However, neither the decision to build the ILC has been made, nor where to build it. Governments in the US and the UK are forced to cut the budget for research and development. The US reduced its funds to a fourth[20], the UK research budgets were cut severely[21]. Thus, the development of the ILC has been slowed down.

The large delay of the ILC made the search for an intermediate application for the DEPFET detector necessary. The development of a vertex detector based on the DEPFET technology was continued for the Belle detector at the SuperKEKB accelerator facility in Japan.

# 3.3.1 Vertex Detector Geometry for ILC

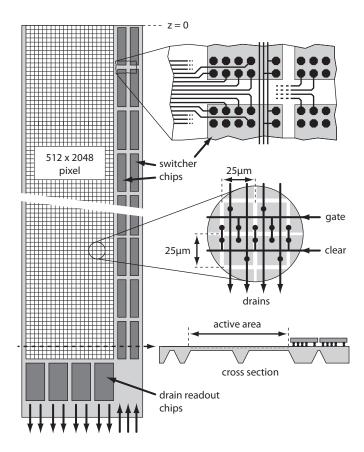

Reconstruction of all tracks and the assignment of the vertices to the primary, secondary and tertiary events requires a high resolution detector with a spacial resolution of  $4\mu m$ . Multiple layers of detectors are placed around the beam pipe with a small overlap for a precise track reconstruction.

The DEPFET uses pixel sizes of  $25\mu m \times 25\mu m$ , which allows a binary resolution of  $25\mu m/\sqrt{12}\approx 7\mu m$ . The pixel signal is compared with a threshold value to detect a hit at the binary read-out scheme. Only this hit information is stored. A resolution of  $3.5\mu m$  is achieved with the  $50\mu m$  thin detector by interpolation using the center-of-gravity method and a signal-to-noise ratio of 40 [12].

Figure 3.9 shows the innermost layer. The modules are placed as close as possible to the beam pipe, at a radius of 1.5cm. The steering chips are at the long side of the matrix and the readout chips are at the short end. The modules are overlapping, to

Figure 3.9: ILC inner layer modules placed around the beam pipe with steering and readout chips. [12]

| Layer | Radius<br>(mm) | Number of ladders | Ladder length (mm) | Ladder width (mm) | Frame<br>Rate |

|-------|----------------|-------------------|--------------------|-------------------|---------------|

| 1     | 15.5           | 8                 | 100                | 13                | 50μs          |

| 2     | 26             | 8                 | 2x125              | 22                | $250 \mu s$   |

| 3     | 38             | 12                | 2x125              | 22                | $250 \mu s$   |

| 4     | 49             | 16                | 2x125              | 22                | $250 \mu s$   |

| 5     | 60             | 20                | 2x125              | 22                | 250 <i>μs</i> |

Table 3.1: Proposed ILC DEPFET vertex detector layer configuration. [12]

cover the inactive balcony of one module by the active area of the next module. The detector's active area has a size of  $4096 \times 512$  pixels, with a length of  $\approx 10$  cm, given by the beam pipe, and the pixel size of  $25\mu m \times 25\mu m$ . Table 3.1 shows the proposed geometric properties of the 5 layers of the vertex detector.

# 3.3.2 Read-out and Timing

As the detectors are in a high multiplicity environment, where many events occur simultaneously, many pixels are hit by incident particles. With the given accelerator timing parameters and physics simulations, the hit multiplicity is  $\approx 0.05$  hits per  $mm^2$  and bunch for the inner layer. Assuming that, due to charge sharing, 30% of the particles create hits not only in one but two pixels, the integrated occupancy in one bunch train would be 15%. This amount of hit pixels per read out frame complicates track reconstruction and is unacceptable. The occupancy has to be reduced to 1% by reading out the detector several times during a bunch train. The readout speed is the driving force in the detector development for the ILC. [12]

Reading a 4096 row matrix requires high speed steering and readout chips with low noise

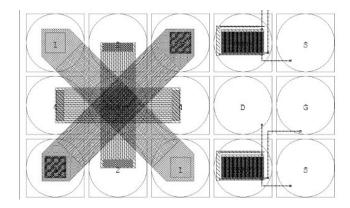

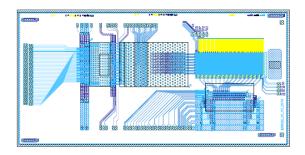

Figure 3.10: ILC half module drawing with cross section of the thinning, double row organization and chip location. [22]

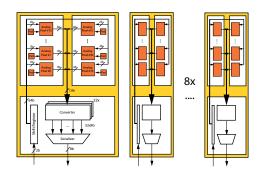

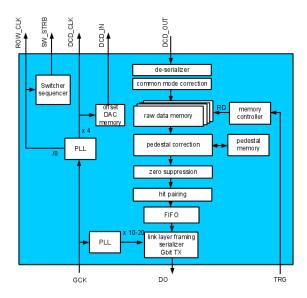

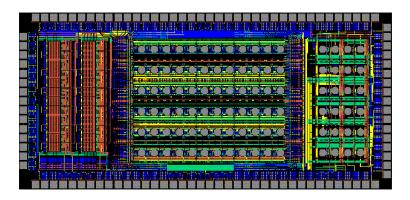

and low power consumption. A trade-off between speed, noise and power consumption needs to be found. The effective readout rate can be doubled by splitting the matrix in 2 halves and reading out from both ends. The electronics are running at moderate speed with low noise and without excessive power consumption. To reduce the speed even more, two consecutive rows are grouped and controlled by the same gate and clear signals (see figure 3.10). This requires twice the amount of drain lines and readout electronics. The matrix of the inner layer with  $4096 \times 512$  pixels would then connect to 1024 channels with gate and clear signals and 1024 readout channels per half module.

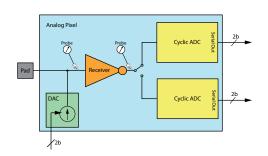

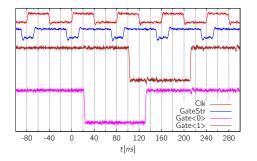

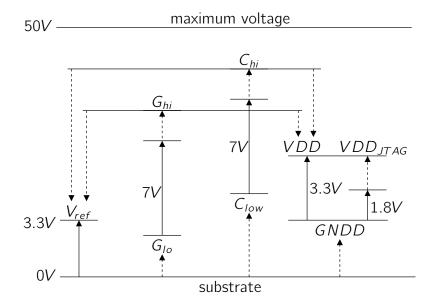

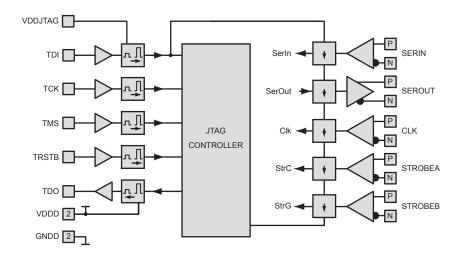

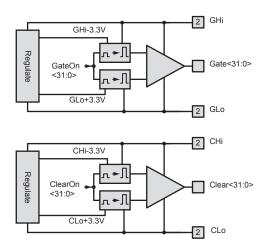

The occupancy can be reduced when reading out with an effective row rate of 40MHz, with both halves of the matrix running at 20MHz. Because a sample-clear-sample (double-sampling) readout was chosen for the ILC, the sampling and digitalization of two values had to be within 50ns = 1/20MHz per double row. Therefore, the ADCs digitizing the analog DEPFET values have to run with 40MHz. One frame is read out in  $\approx 50\mu s$ . 20 frames can be read out in a bunch train of 1ms.

The occupancy of layers 2-5 is much lower, because the distance to the interaction point is greater. This allows larger detectors and a slower readout speed of  $250\mu s$  per frame.

| Layer | Number of | Active | Power per | Power per | Average |

|-------|-----------|--------|-----------|-----------|---------|

|       | ladders   | pixels | ladder    | layer     |         |

| 1     | 8         | 2048   | 12W       | 96W       |         |

| 2     | 8         | 3072   | 21W       | 168W      |         |

| 3     | 12        | 3072   | 21W       | 252W      |         |

| 4     | 16        | 3072   | 21W       | 336W      |         |

| 5     | 20        | 3072   | 21W       | 420W      |         |

| total |           |        |           | 1272W     | 6.4W    |

Table 3.2: ILC DEPFET power consumption during burst and averaged to the 200ms beam timing. [12]

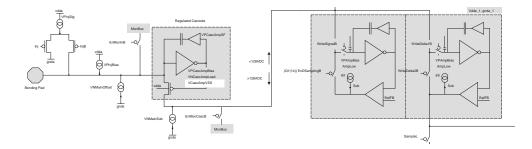

The steering signals are controlled by the Switcher-3 chip (see chapter 5.1). One chip is needed for the clear and another for the gate signals, as each chip supports only one steering voltage. Two columns of chips are located on the balcony.

A drain current digitization with the Curo chip was foreseen (chapter 3.5.1). The high capacitance of the long ILC matrixes caused an unacceptable noise contribution by the Curo. A successor chip called DCD (see chapter 4.1) had to be developed.

#### 3.3.3 Module Power Consumption

A benefit of the DEPFET is its low power consumption. A pixel consumes  $I_D \times V_{DS} = \sim 100 \mu A \times \sim 5V \approx 500 \mu W$  during read out. The power consumption of a switched off pixel is almost zero, although it is still sensitive and collects signal electrons. A half module has 2 rows of 512 DEPFET pixels activated during read out with the readout scheme described above. Therefore, an inner layer module consumes 1W. Adding the Switcher steering chips' 0.85W and the DCD readout chips' 2048 channels, with 5mW per channel, this sums up to  $\approx 12W$ .

Table 3.2 shows the approximative power consumption of all layers. The total power consumption of 1272W during reading breaks down to 6.4W, because the DEPFETs and the electronics are only active and read out during the bunch train of 1ms. The system is idle in the 199ms pause. Since most of the power is dissipated by the readout chips located outside the acceptance region, an active cooling is feasible without adding material to the critical active area. The power dissipated in the active volume by the DEPFETs and the steering chips is low and can be removed by air cooling. [12]

# 3.3.4 Irradiation Damages and Radiation Length

An expected dose of 200krad of ionizing radiation and  $10^{11} n/cm^2$  1MeV neutron equivalents will be deposited in the silicon devices close to the interaction point during 5 years

of ILC operation. The influence on the DEPFETs from PXD4 production was tested by irradiation up to a dose of 900krad with gamma rays and  $3x10^{12}n/cm^2$  1MeV neutron equivalent protons, which simulates 30 years of operation. Bulk damages, with change of the effective doping concentration, are not observed for non-ionizing radiation, as expected. A by  $2e^-$  ENC slightly increased noise at higher temperature indicates an additional shot noise. [12]

The radiation length of the module should be about 0.1% in order to reduce multiple scattering effects. The material budget would be already used up by a  $100\mu m$  thick sensor, without taking the additional radiation length of steering chips and interconnection technology into account. The readout chips are not added, because they are outside of the detector's acceptance area. To meet the requirements, the  $450\mu m$  thick silicon substrate of the DEPFET detector has to be thinned to  $\approx 50\mu m$ . It is only partly thinned for stability reasons and mainly in the active region. A signal to noise ratio of >40 can be achieved due to the good properties of the DEPFET, even with the  $50\mu m$  thin active area. The thin active area and the support frame add  $0.1\%~X_0$ , where the also thinned steering chips will add another 0.01%. As the chips are connected with a flip chip technology using gold bumps, the material added by the gold has to be included in the material budget. It adds another 0.01%. The radiation length sums up to an acceptable value of  $0.12\%~X_0$ . [12]

# 3.3.5 Alternative Detector Concepts

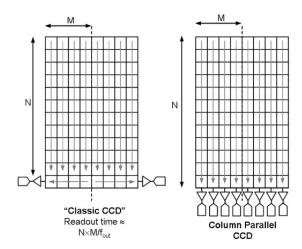

Several other detector concepts have been proposed for the ILC pixel vertex detector. The use of Charge Coupled Devices with a column parallel read-out to improve speed or with an in-pixel storage are options, together with monolithic active pixel sensors based on CMOS technologies.

#### **Charge Coupled Devices**

Charge Coupled Devices (CCD) for the ILC can have pixel sizes down to  $2 \times 2\mu m^2$ , but a pixel size of  $20 \times 20\mu m^2$  is sufficient to achieve the required resolution. The pixel detector consist of five layers mounted in a low-mass foam cryostat. The inner layer modules are  $100 \times 13mm^2$  large and are read out from both ends, while the four outer layers consist of  $125 \times 22mm^2$  large devices. Two of each are glued together to form the ladder. The sensitive epitaxial layer is  $20\mu m$  thin, which allows the detector to be thinned close to this value for a low material budget. A low read-out noise of  $10~e^-ENC$  gives a good S/N, even with thin devices. Fully depleted devices are mandatory to collect the charge within a clock cycle. A point resolution of  $5.8\mu m$  can be achieved. Charge sharing between pixels is not available and the resolution cannot be increased by interpolation.

Charge trapping due to irradiation damages could cause signal electrons to be trapped

Figure 3.11: Comparison of standard and column-parallel CCD read-out. [23]

while they are traveling from their generation point to the output. The high capacitive load of clock signals, connected to every pixel and used for charge shifting, cause high power dissipation. Low swing signals of 2V are used in contrast to the 10-15V of standard designs. The capacitance of a detector area of  $10cm^2$  sums up to 50nF and even with the reduced swing is a current of  $\approx 10A$  needed when operated at 50MHz. The output drivers designed in the CCD-technology need a high supply voltage in the range of 15-20V and cause a high power dissipation. CMOS circuits can't be integrated due to incompatible technologies.

A column-parallel readout is used to increase the read-out speed. Figure 3.11 illustrates the differences between standard and parallel read-out. A separate processing chain is used for every column. The read-out chip is flip-chip bonded to the detector with 125 solder bumps. It allows a constant 20kHz frame rate and is operated at 50MHz on the inner layer to reduce the occupancy to acceptable limits. It features double sampling, a 5-bit ADC and a read-out FIFO with 132 entries. [24][23]

#### Charge Coupled Devices - In Pixel Storage (ISIS)

As sensors are sensitive to Radio Frequency pickup caused by the accelerator during charge to voltage conversion, a new concept of CCD has been proposed. Figure 3.12 shows the in-situ storage (ISIS) of 20 charge signals in a CCD pixel. During the 1ms bunch train, the charge is shifted from the photo-gate to the storage pixels with a moderate frequency of 20kHz. The stored signals are read out during the inter-bunch pause of 199ms with a frequency of 1MHz. This is by a factor of 50 slower than the continuous column-parallel CCD read-out. [24]

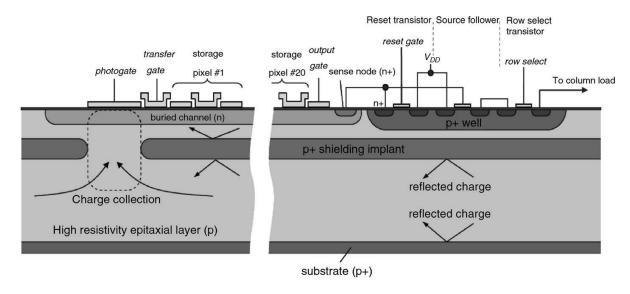

Figure 3.12: Cross section of CCD with in-situ storage. [24]

Figure 3.13: Detection principle of a CMOS sensor. Generated signal charge is traveling by thermal diffusion to the collection electrode.

#### Monolithic Active Pixel Sensors

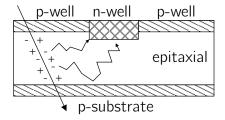

In monolithic active pixel sensors, signal processing electronics are integrated on the sensor substrate. A double-well CMOS process with a  $5-15\mu m$  thin epitaxial layer is used. The signal charge is generated by the incident particle in the epitaxial layer and is collected in a diode formed by a n-well implantation in the p-epi layer (figure 3.13). Since no electrical field is available, like in a fully depleted bulk, the signal electrons travel by thermal diffusion into the collection electrode. The thermal diffusion leads to a larger signal collection time of  $\approx 100 ns$ . A thinner epitaxial layer leads to shorter collection times and smaller charge spreading, but also to a smaller signal. A S/N of 20-30 and a point resolution of  $1.5-2.5\mu m$  was achieved with  $20\mu m$  epi layer thickness.

A read-out time of  $\leq 25\mu s$  is required to keep the occupancy below 1%. The pixel columns are organized perpendicular to the beam axis and are read out in parallel in order to achieve a shorter column read-out time. The charge is digitized with a 4-5bit ADC integrated in each column. Depending on the layer, a pixel pitch ranging from 20 to  $40\mu m$  is used. The CMOS process allows integration of circuits for amplification, pedestal correction, digitization, etc in every pixel. Detector thinning to a few tens of microns is permitted by the thin active volume of the epi layer. Thinning to  $20\mu m$  is currently evaluated. [25]

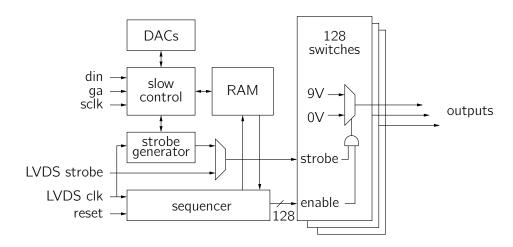

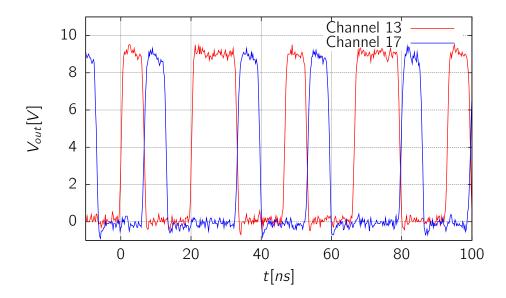

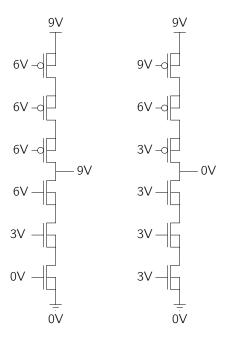

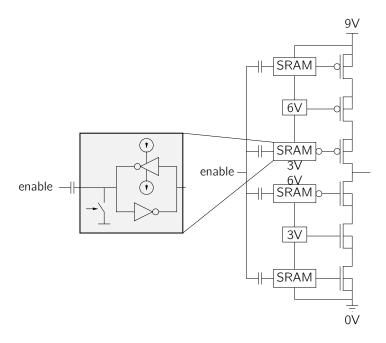

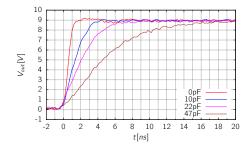

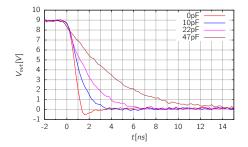

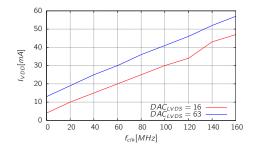

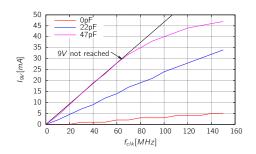

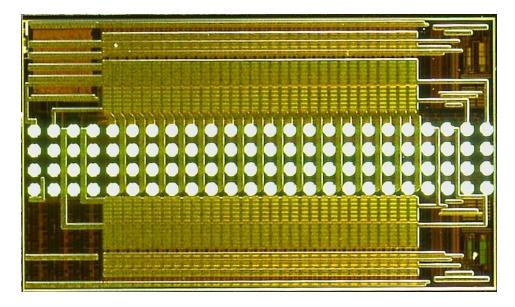

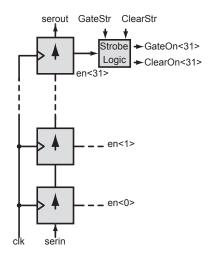

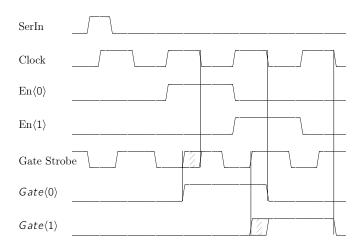

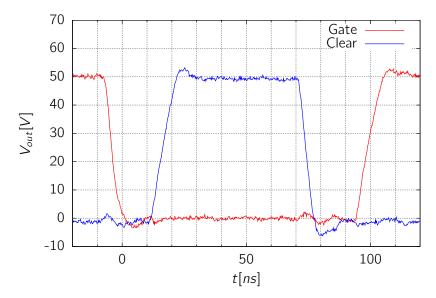

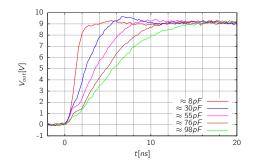

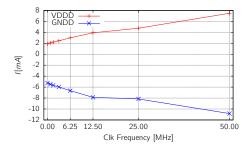

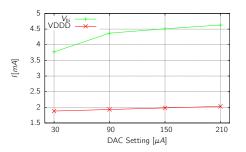

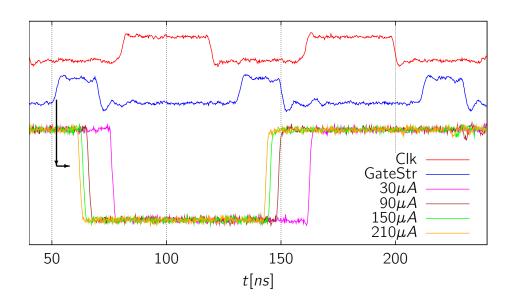

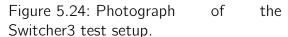

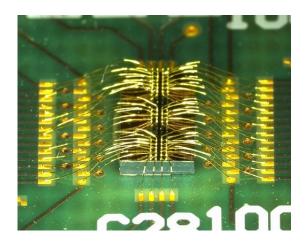

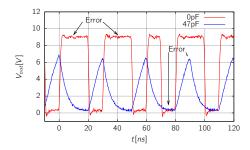

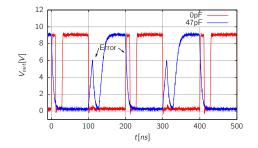

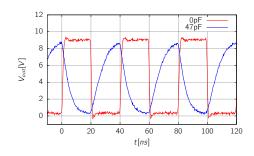

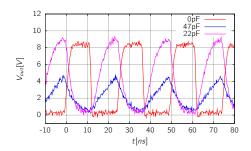

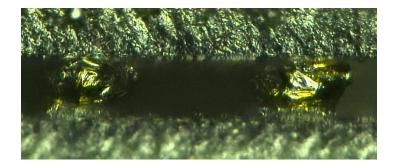

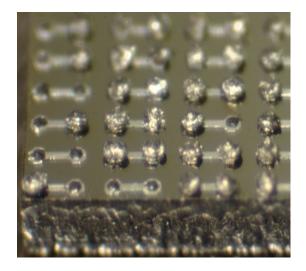

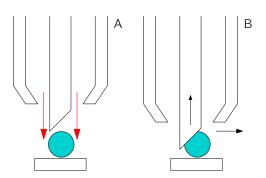

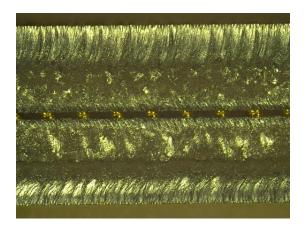

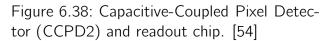

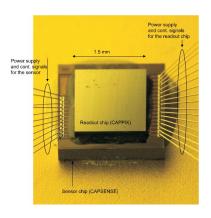

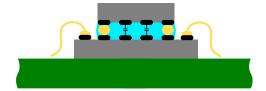

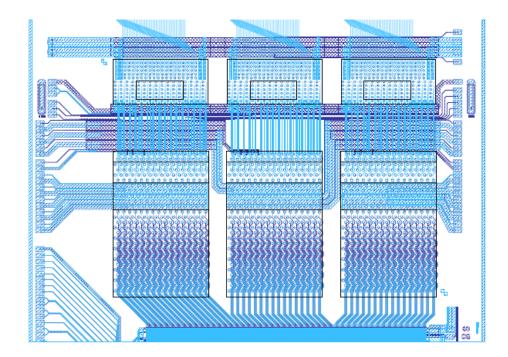

# 3.4 The Belle II Experiment at SuperKEKB