# Hardware Support for Efficient Packet Processing

Inauguraldissertation zur Erlangung des akademischen Grades eines Doktors der Naturwissenschaften der Universität Mannheim

vorgelegt von

Dipl.-Inf. Benjamin Ulrich Geib aus Heidelberg

Mannheim, 2012

Dekan:Prof. Dr. Heinz Jürgen Müller, Universität MannheimReferent:Prof. Dr. Ulrich Brüning, Universität HeidelbergKorreferent:Prof. Dr. Reinhard Männer, Universität Heidelberg

Tag der mündlichen Prüfung: 21.03.2012

Für Sonja

# Abstract

Scalability is the key ingredient to further increase the performance of today's supercomputers. As other approaches like frequency scaling reach their limits, parallelization is the only feasible way to further improve the performance. The time required for communication needs to be kept as small as possible to increase the scalability, in order to be able to further parallelize such systems.

In the first part of this thesis ways to reduce the inflicted latency in packet based interconnection networks are analyzed and several new architectural solutions are proposed to solve these issues. These solutions have been tested and proven in a field programmable gate array (FPGA) environment. In addition, a hardware (HW) structure is presented that enables low latency packet processing for financial markets.

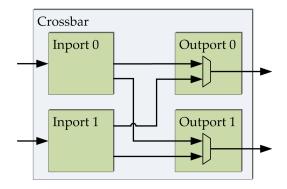

The second part and the main contribution of this thesis is the newly designed crossbar architecture. It introduces a novel way to integrate the ability to multicast in a crossbar design. Furthermore, an efficient implementation of adaptive routing to reduce the congestion vulnerability in packet based interconnection networks is shown. The low latency of the design is demonstrated through simulation and its scalability is proven with synthesis results.

The third part concentrates on the improvements and modifications made to EXTOLL, a high performance interconnection network specifically designed for low latency and high throughput applications. Contributions are modules enabling an efficient integration of multiple host interfaces as well as the integration of the on-chip interconnect. Additionally, some of the already existing functionality has been revised and improved to reach better performance and a lower latency. Micro-benchmark results are presented to underline the contribution of the made modifications.

# Zusammenfassung

Der wichtigste Faktor, um die Leistung heutiger Supercomputer weiter steigern zu können, ist Skalierbarkeit. Da andere Ansätze, wie zum Beispiel Frequenzskalierung, ihre Grenzen erreicht haben, ist Parallelisierung der einzig mögliche Weg um die Leistung solcher Systeme weiter steigern zu können. Damit ein System skalierbar ist, muss die Zeit, welche für die Kommunikation zwischen einzelnen Knoten benötigt wird, so klein wie möglich gehalten werden.

Der erste Teil dieser Dissertation analysiert Möglichkeiten und zeigt neue architektonische Lösungen, welche die Latenz reduzieren und somit die Skalierbarkeit verbessern. Die Wirksamkeit dieser Lösungen wurden in einer FPGA (Field Programmable Gate Array) Umgebung getestet und bewiesen. Zudem wird eine Hardware-Struktur vorgestellt, welche das Dekodieren von Datenpaketen, wie sie beim Wertpapierhandel an Finanzmärkten verwendet werden, mit besonders niedriger Latenz und hohem Durchsatz ermöglicht.

Den zweiten und Hauptbestandteil dieser Dissertation stellt die neu entworfene Crossbar Architektur dar. Darin wird eine Lösung vorgestellt, wie die Fähigkeit Multicasts in einem Netzwerk zu senden, effizient in einen Crossbar integriert werden kann. Des Weiteren wird eine effiziente Implementierung von adaptivem Routing dargelegt, welche die Empfindlichkeit gegenüber Blockierungen in paketbasierten Netzwerken reduziert. Die niedrige Latenz des Designs wird durch Simulation und seine Skalierbarkeit durch Syntheseergebnisse gezeigt.

Der dritte Teil konzentriert sich auf die Verbesserungen und Erweiterungen, die an Extended ATOLL (EXTOLL) gemacht wurden. EXTOLL ist ein Hochgeschwindigkeitsnetzwerk, das speziell für Anwendungen mit den Anforderungen niedrige Latenz und hoher Durchsatz entwickelt wurde. Im Rahmen dieser Arbeit wurden Module zur effizienten Integration mehrerer Host Interfaces sowie des On-Chip Netzwerks entworfen und implementiert. Zudem wurde bereits existierende Funktionalität nochmals durchleuchtet und verbessert, um höhere Performanzwerte und eine niedrigere Latenz zu erreichen. Um den Beitrag der gemachten Veränderungen zu unterstreichen, werden Micro-Benchmark Ergebnisse präsentiert.

# Contents

| Intro | oductio                                                                                                                                | n                                                                                                                                                                                                                                                                                    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------|----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1   | Motiv                                                                                                                                  | ation                                                                                                                                                                                                                                                                                | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1.2   | Graph                                                                                                                                  | ical Representations                                                                                                                                                                                                                                                                 | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1.3   | Outlin                                                                                                                                 | ne                                                                                                                                                                                                                                                                                   | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Effic | cient Pa                                                                                                                               | acket Processing                                                                                                                                                                                                                                                                     | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.1   | Arbite                                                                                                                                 | er Generator                                                                                                                                                                                                                                                                         | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | 2.1.1                                                                                                                                  | State of the Art                                                                                                                                                                                                                                                                     | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | 2.1.2                                                                                                                                  | Implementation                                                                                                                                                                                                                                                                       | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2.2   | FIFO I                                                                                                                                 | Implementations                                                                                                                                                                                                                                                                      | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | 2.2.1                                                                                                                                  | Multi-Queue FIFO                                                                                                                                                                                                                                                                     | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | 2.2.2                                                                                                                                  | Speculative FIFO                                                                                                                                                                                                                                                                     | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | 2.2.3                                                                                                                                  | Double Shift-Out FIFO                                                                                                                                                                                                                                                                | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2.3   | Write                                                                                                                                  | Combining Buffer                                                                                                                                                                                                                                                                     | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2.4   | Virtua                                                                                                                                 | l Ring Buffer Handler                                                                                                                                                                                                                                                                | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

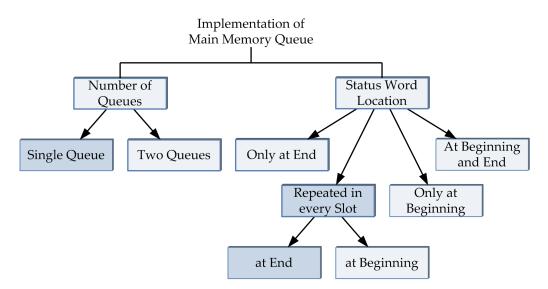

|       | 2.4.1                                                                                                                                  | State of the Art                                                                                                                                                                                                                                                                     | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | 2.4.2                                                                                                                                  | Design Space Analysis                                                                                                                                                                                                                                                                | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | 2.4.3                                                                                                                                  | Implementation                                                                                                                                                                                                                                                                       | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | 2.4.4                                                                                                                                  | Performance                                                                                                                                                                                                                                                                          | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2.5   | Tag M                                                                                                                                  | atching Unit                                                                                                                                                                                                                                                                         | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | 2.5.1                                                                                                                                  | State of the Art                                                                                                                                                                                                                                                                     | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | 2.5.2                                                                                                                                  | Implementation                                                                                                                                                                                                                                                                       | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | 2.5.3                                                                                                                                  | General Operation Description                                                                                                                                                                                                                                                        | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2.6   | FAST                                                                                                                                   | Decoder                                                                                                                                                                                                                                                                              | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

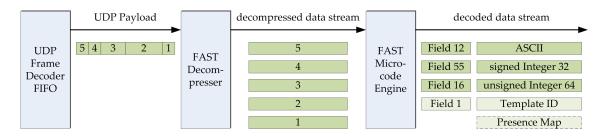

|       | 2.6.1                                                                                                                                  | FAST Protocol                                                                                                                                                                                                                                                                        | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

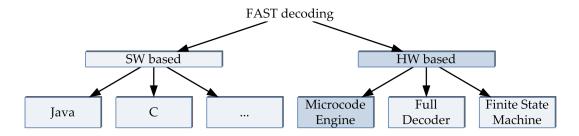

|       | 2.6.2                                                                                                                                  | Related Work                                                                                                                                                                                                                                                                         | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | 2.6.3                                                                                                                                  | Design Space Analysis                                                                                                                                                                                                                                                                | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

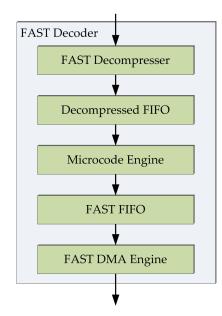

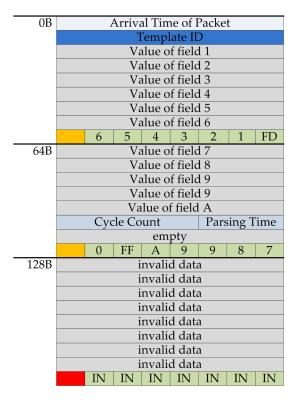

|       | 2.6.4                                                                                                                                  | Baseline Implementation                                                                                                                                                                                                                                                              | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

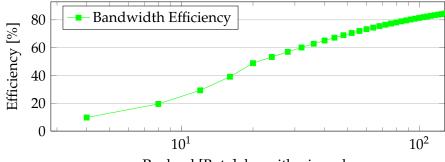

|       | 2.6.5                                                                                                                                  | Baseline Performance                                                                                                                                                                                                                                                                 | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | 2.6.6                                                                                                                                  | FAST Decoder Improvements                                                                                                                                                                                                                                                            | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | <ol> <li>1.1</li> <li>1.2</li> <li>1.3</li> <li>Efficiency</li> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>2.5</li> </ol> | 1.1 Motiv<br>1.2 Graph<br>1.3 Outlin<br>Efficent Par<br>2.1 Arbite<br>2.1 2<br>2.2 FIFO 1<br>2.2.1<br>2.2 2<br>2.2.3<br>2.3 Write<br>2.4 Virtua<br>2.4.1<br>2.4.2<br>2.4.3<br>2.4.4<br>2.5 Tag M<br>2.5.1<br>2.5.2<br>2.5.3<br>2.6 FAST<br>2.6.1<br>2.6.2<br>2.6.3<br>2.6.4<br>2.6.5 | 1.2       Graphical Representations         1.3       Outline         1.3       Outline         Efficient Packet Processing         2.1       Arbiter Generator         2.1.1       State of the Art         2.1.2       Implementation         2.2       FIFO Implementations         2.1.1       Multi-Queue FIFO         2.2.2       Speculative FIFO         2.2.3       Double Shift-Out FIFO         2.2.4       Virtual Ring Buffer Handler         2.4       Virtual Ring Buffer Handler         2.4.1       State of the Art         2.4.2       Design Space Analysis         2.4.3       Implementation         2.4.4       Performance         2.5.1       State of the Art         2.5.2       Implementation         2.5.3       General Operation Description         2.5.3       General Operation Description         2.6       FAST Decoder         2.6.1       FAST Protocol         2.6.2       Related Work         2.6.3       Design Space Analysis         2.6.4       Baseline Implementation         2.6.5       Baseline Performance |

| 3 | High Performance Switching 63 |         |                                         |     |  |  |

|---|-------------------------------|---------|-----------------------------------------|-----|--|--|

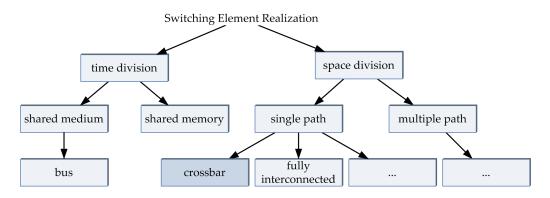

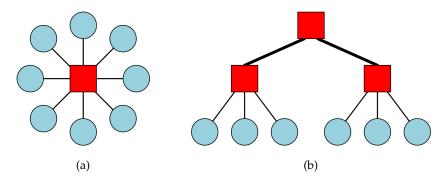

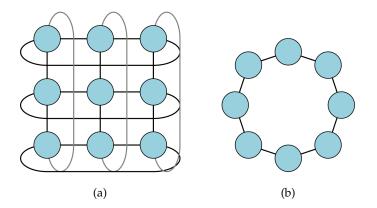

|   | 3.1                           | Switch  | ing Elements                            | 63  |  |  |

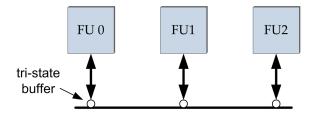

|   |                               | 3.1.1   | Time Division Switching Elements        | 63  |  |  |

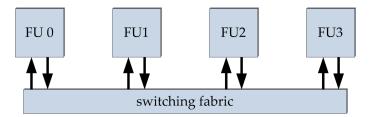

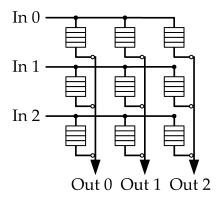

|   |                               | 3.1.2   | Space Division Switching Elements       | 65  |  |  |

|   | 3.2                           | Crossb  | pars as Interconnect Switches           | 66  |  |  |

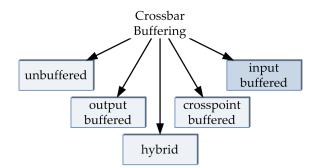

|   |                               | 3.2.1   | Crossbar Buffering                      | 66  |  |  |

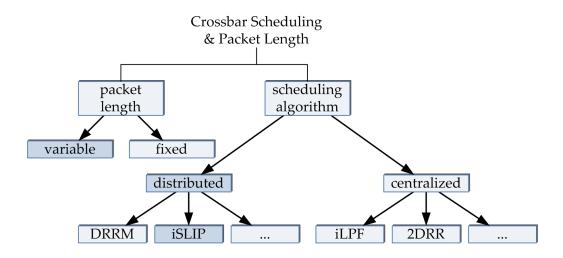

|   |                               | 3.2.2   | Crossbar Scheduling                     | 68  |  |  |

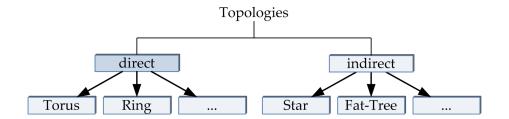

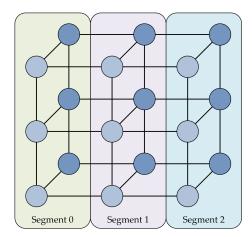

|   | 3.3                           | Topolo  | ogies                                   | 69  |  |  |

|   | 3.4                           | Termin  | nology                                  | 70  |  |  |

|   |                               | 3.4.1   | Deadlocks                               | 70  |  |  |

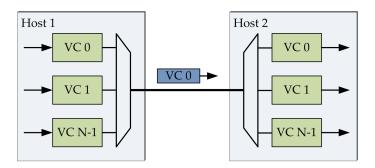

|   |                               | 3.4.2   | Virtual Channels                        | 71  |  |  |

|   |                               | 3.4.3   | Head-of-Line Blocking                   | 72  |  |  |

|   |                               | 3.4.4   | Virtual Output Queuing                  | 72  |  |  |

|   |                               | 3.4.5   | Credit Based Flow Control               | 73  |  |  |

|   |                               | 3.4.6   | Wormhole Switching                      | 74  |  |  |

|   |                               | 3.4.7   | Virtual-Cut-Through Switching           | 74  |  |  |

|   |                               | 3.4.8   | Adaptive Routing                        | 74  |  |  |

|   | 3.5                           | Requi   | rements for an Interconnection Network  | 75  |  |  |

|   | 3.6                           | State o | f the Art                               | 76  |  |  |

|   |                               | 3.6.1   | Cray Gemini                             | 76  |  |  |

|   |                               | 3.6.2   | Tofu                                    | 78  |  |  |

|   |                               | 3.6.3   | TianHE-1A Interconnect                  | 80  |  |  |

|   |                               | 3.6.4   | Blue Gene/Q                             | 80  |  |  |

|   | 3.7                           | State c | f EXTOLL R1 Crossbar                    | 82  |  |  |

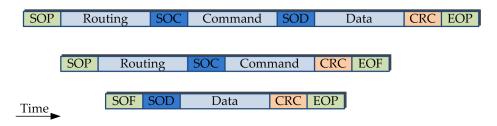

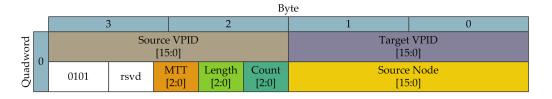

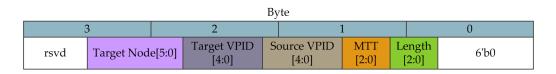

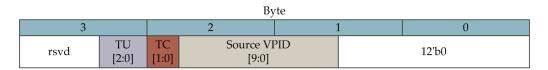

|   |                               | 3.7.1   | Packet Format                           | 85  |  |  |

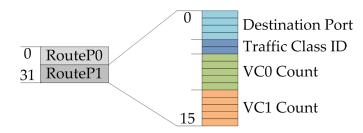

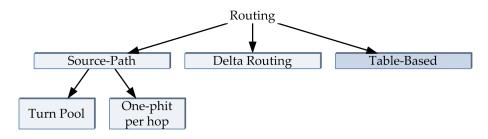

|   |                               | 3.7.2   | Routing                                 | 86  |  |  |

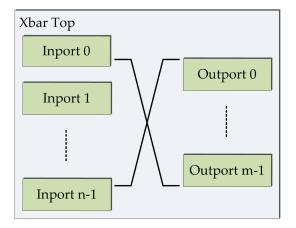

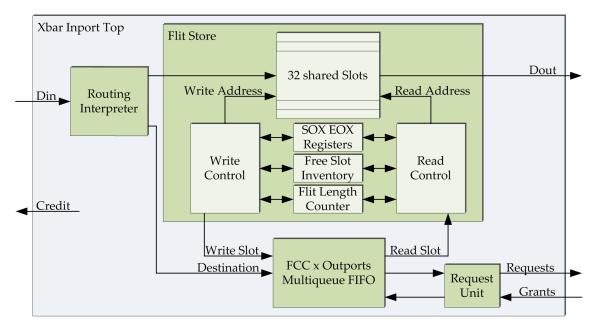

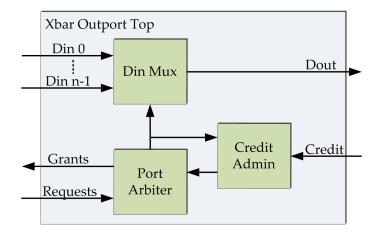

|   |                               | 3.7.3   | Architecture                            | 87  |  |  |

|   |                               | 3.7.4   | Performance                             | 90  |  |  |

|   | 3.8                           | Implei  | mentation of R2 Crossbar                | 93  |  |  |

|   |                               | 3.8.1   | Routing                                 | 93  |  |  |

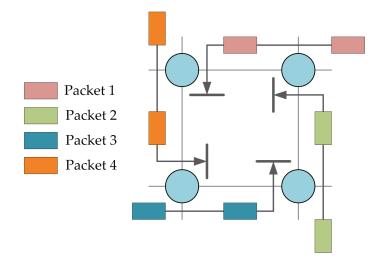

|   |                               | 3.8.2   | Ordering of Packets                     | 99  |  |  |

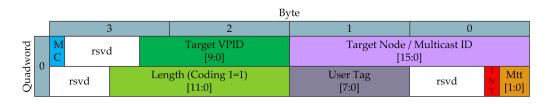

|   |                               | 3.8.3   | Packet Format                           | 101 |  |  |

|   |                               | 3.8.4   | Multicast                               | 102 |  |  |

|   |                               | 3.8.5   | Request Allocation and Grant Generation | 107 |  |  |

|   |                               | 3.8.6   | Fine Grain Credits                      | 108 |  |  |

|   |                               | 3.8.7   | Debug-Ability and Maintainability       | 111 |  |  |

|   |                               | 3.8.8   | Early Arbitration                       | 112 |  |  |

|   |                               | 3.8.9   | Further Optimizations                   | 113 |  |  |

|   |                               | 3.8.10  | Multi-Queue-FIFO Optimizations          | 116 |  |  |

### Contents

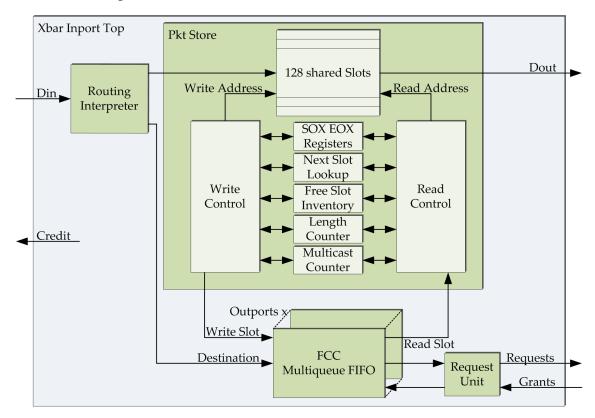

|    |        | 3.8.11  | Overall Architecture            | 120 |

|----|--------|---------|---------------------------------|-----|

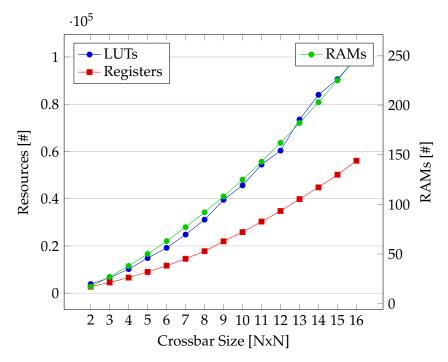

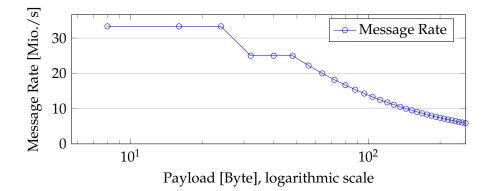

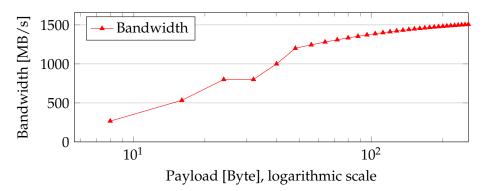

|    |        | 3.8.12  | Evaluation                      | 121 |

|    | 3.9    | Outloo  | ok and Future Improvements      | 125 |

|    |        | 3.9.1   | Multicast Optimization          | 125 |

|    |        | 3.9.2   | Read Slot Lookahead             | 126 |

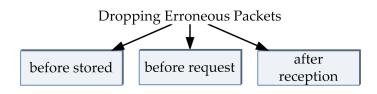

|    |        | 3.9.3   | Removal of Erroneous Packets    | 127 |

|    |        | 3.9.4   | Balance Packet Travel Time      | 129 |

|    |        | 3.9.5   | Split Inport Into Smaller Units | 130 |

|    | 3.10   | Crossł  | par Summary                     | 130 |

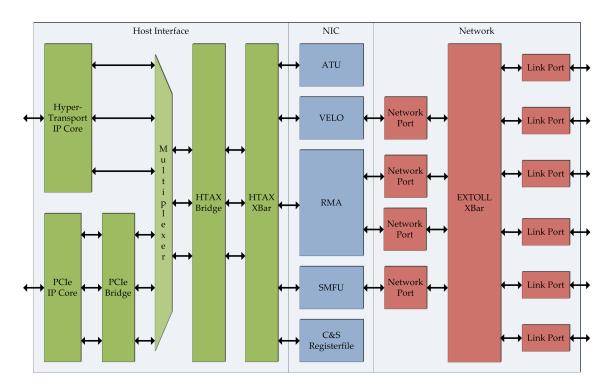

| 4  | FXT    | OLL     |                                 | 133 |

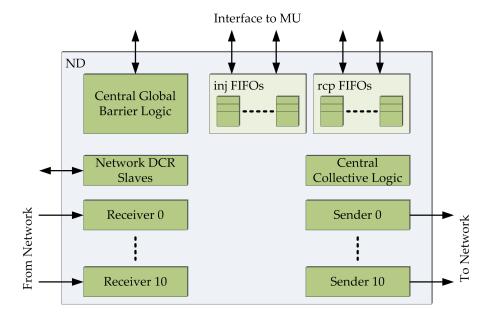

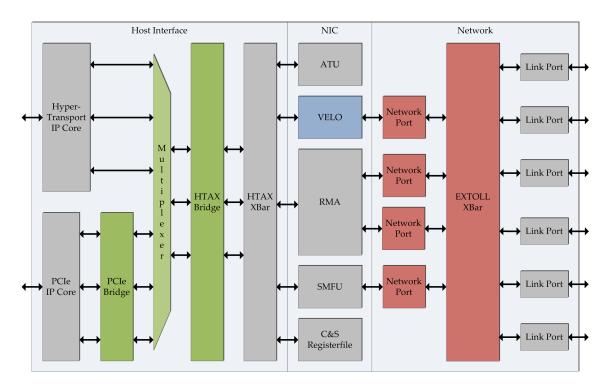

| т  | 4.1    |         | Overview                        | 134 |

|    | 1.1    | 4.1.1   | Host Interface                  | 135 |

|    |        | 4.1.2   | HTAX                            | 137 |

|    |        | 4.1.3   | Register File                   | 137 |

|    |        | 4.1.4   | ATU                             | 139 |

|    |        | 4.1.5   | RMA                             | 139 |

|    |        | 4.1.6   | SMFU                            | 139 |

|    |        | 4.1.7   | LP                              | 140 |

|    | 4.2    |         | Dar                             | 140 |

|    | 4.3    |         | Bridge                          | 141 |

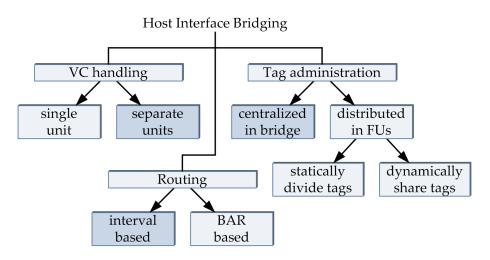

|    | 1.0    | 4.3.1   | Design Space Analysis           | 142 |

|    |        | 4.3.2   |                                 | 144 |

|    | 4.4    |         | xpress Bridge                   | 147 |

|    | 1.1    | 4.4.1   | Requirements                    | 148 |

|    |        | 4.4.2   |                                 | 140 |

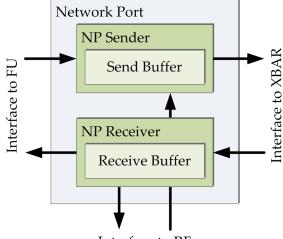

|    | 4.5    |         | prk Port                        | 151 |

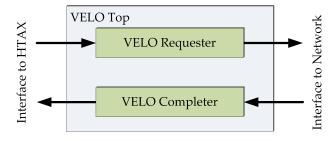

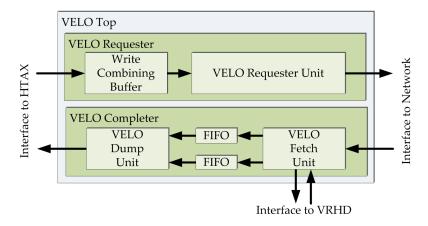

|    | 4.6    | VELO    |                                 | 151 |

|    | 1.0    | 4.6.1   | Introduction                    | 155 |

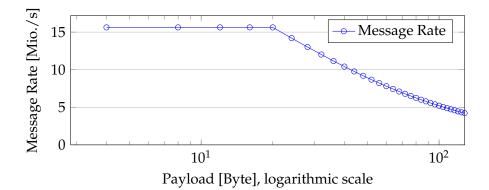

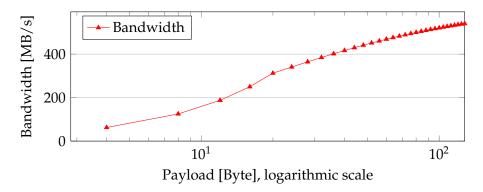

|    |        | 4.6.2   | VELO Evaluation                 | 154 |

|    |        | 4.6.3   | VELO Requester R2               | 150 |

|    |        | 4.6.4   | VELO Completer R2               | 161 |

|    |        | 4.6.5   | VELO Performance                | 166 |

|    |        |         |                                 |     |

| 5  | Con    | clusion |                                 | 169 |

| Δ. |        |         |                                 | 175 |

| AC | ronyr  | IIS     |                                 | 175 |

| Bi | bliogr | aphy    |                                 | 179 |

|    | - 8-   | • •     |                                 |     |

#### Contents

| List of Figures | 191 |

|-----------------|-----|

| List of Tables  | 195 |

# 1 Introduction

Researches always have the need for more computing power. To satisfy this thirst, a great amount of work is done trying to increase the performance of supercomputers. This performance is measured in floating point operations per second (FLOPS) using a standard benchmark called *Linpack* [1]. Today's fastest supercomputer, Japan's *K-Computer* [2], is capable of performing around 10 Peta-FLOPS, a ten with 16 zeros. The next big step for such machines is to reach the *exascale era*.

### 1.1 Motivation

Supercomputers need to be a hundred times faster as the *K-Computer* in order to achieve an Exa-FLOP. It is unfeasible to further increase the frequency with which the individual processors run as they hit the power wall, because the power consumption increases quadratically with increasing frequencies. Thus, the only solution to increase the overall performance is seen in parallelization.

While increasing the number of processors is a valid approach, the performance does not scale with the same rate due to limiting factors. These limiting factors are again power-, area consumption and most importantly communication overhead. It is common sense that with an increasing amount of processors, both power and area consumption increase linear. Increasing the performance of a supercomputer, equipped with currently available technology, by a factor of hundred thus increases the power and area consumption by at least the same factor. While the two problems power and area can be solved with pure force, the limiting factor communication overhead remains. When parallelizing a given problem to solve it on a large cluster of processing nodes, the problem size that each individual node has to process decreases in the same degree. Consequently the time required to calculate the result also decreases. In an ideal environment with a problem that can be partitioned into an endless number of sub-problems and without any communication overhead, the performance increases linear with the parallelization degree.

#### 1 Introduction

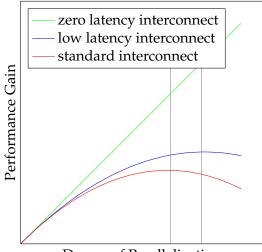

However, communication overhead between the nodes increases as the problem has to be transferred to all nodes. Furthermore each node needs to synchronize their results more often with other nodes. The time required for this communication overhead unfortunately does not decrease for smaller sub-problem sizes and due to the increased amount of messages the overall time for communication increases significantly. At a certain degree of parallelization the time spent for communication is larger than the time spent for actual computation. This leads to an overall performance drop as it is illustrated in figure 1.1. This effect is known as *Amdahls Law* [3].

Degree of Parallelization

Figure 1.1: Performance Gain when Parallelizing a Computational Task [3]

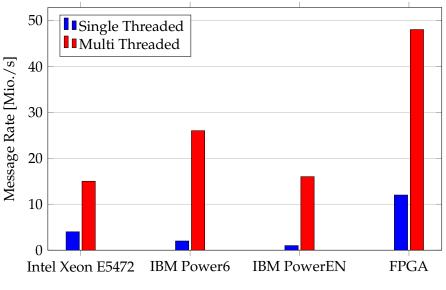

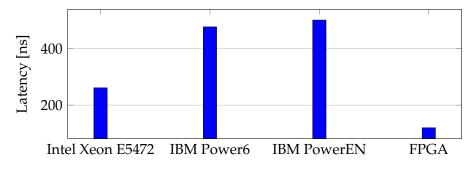

To reduce the amount of time spent for communication is therefore an important research topic. There are three criteria to characterize the performance of an interconnection network. *Bandwidth* or *throughput* is the most common term to describe the performance of networks in high performance computing (HPC) and describes the amount of data that can pass through the network in a period of time. *Latency* is the time required to send a minimum sized packet from one node to another including all software (SW) and hardware (HW) overhead. The *message rate* describes the amount of messages that can be injected into or received from the network by a single node in a period of time, effectively describing how good the processing of independent messages can be overlapped. The higher the overlapping, the more messages can be processed in a certain period of time.

Latency is an important factor due to the above mentioned percental increase in time spent for communication compared to computation when parallelizing tasks. The lower the latency, the less time is spent in communication. Furthermore the scalability of the network increases as illustrated in figure 1.1. Compared to a *standard interconnect* the performance decrease due to communication of a *low latency interconnect* is at a higher

parallelization rate. The gap between the two gray lines represents the increased scalability of the network due to the lower latency. Here the performance gain decreases at a higher rate of parallelization improving the overall efficiency of the cluster.

The three fastest supercomputers according to the *Top500* list of June 2011 [4] all use a custom built interconnection network to leverage the increased processor count without decreasing the overall performance. Such extreme scale computing will always have a need for custom interconnects, like the *TOFU Interconnect* from Japan's *K Computer* [2] which ranked first in the June and November 2011 *Top500* lists or Cray's *Gemini Interconnect* [5], which is used in Cray's *XE6* and *XK6* series systems. Custom interconnects have the advantage of being able to be designed to exactly meet the customers needs and therefore remove bottlenecks that occur with commodity interconnect technology.

But not only the HPC sector strives for low latency, also financial companies require it to be able to participate in high frequency trading (HFT) or low latency trading. In low latency trading information from the exchanges are received through a common network, need to be processed and then a decision has to be made whether to buy or sell a stock based on the received information. Subsequently an order has to be sent back to the exchange. Consequently low latency is the key for making money, as only the fastest company is able to buy or sell the most profitable opportunities. For HFT however not only latency, but also *throughput* is of essence to be able to process all incoming information provided by the exchanges. If the system is not capable of processing all arriving data, packets need to be dropped. The result is an inconsistent view of the current market situation, which can then result in wrongful trades.

The latency of a HW structure is determined by two factors, first the amount of pipeline stages and second the frequency at which the module is able to operate. While a deeper pipeline, i.e. a high amount of pipeline stages, enables the designer to increase the operation frequency, it also increases the latency as each pipeline stage requires a clock cycle. A trade off between number of pipeline stages and clock frequency has to be made in order to get the best latency result for a certain module.

Therefore the aim of this thesis is to find ways to reduce latency required for communication and at the same time increase the throughput. This thesis presents HW structures that enable the reduction of latency for different communication types in particular and also shows structures that enable lower latencies and a high throughput for packet processing in general.

## 1.2 Graphical Representations

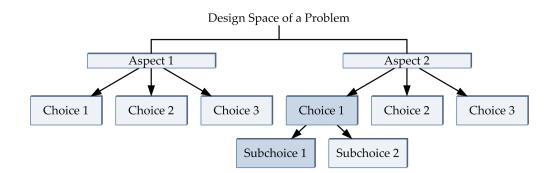

Figure 1.2: An Example Design Space Analysis

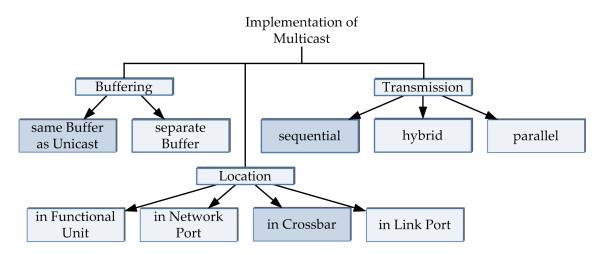

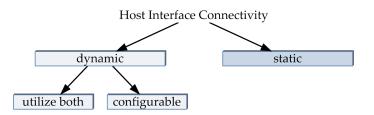

An important part of this work is to analyze options and aspects to solve a given problem. *Design space diagrams* have been introduced by [6] and are a common way to illustrate all different aspects that need to be taken into account and their design choices. Figure 1.2 shows an example diagram where a given problem is divided into multiple orthogonal aspects which are connected using also orthogonal lines. For each aspect all possible options are connected using direct arrows. A third level is used, if an option can be further divided. The option chosen for an implementation is highlighted using a darker blue tone.

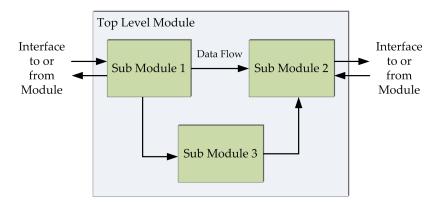

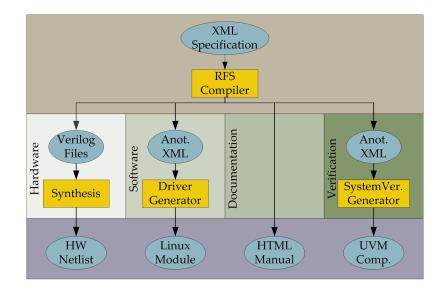

Figure 1.3: An Example Block Diagram

HW is always described in modules, which include the desired functionality. If a problem is very complex, these modules are often divided into multiple sub-modules, which are connected to each other. A *block diagram* is then used as an abstraction layer to illustrate the connectivity of these sub-modules within such a top level module. In figure 1.3 an example for such a block diagram is given. Interfaces to other modules are illustrated using arrows at the edges of modules, the direction of the internal data flow

is also illustrated using arrows. The actual wiring required between modules and sub modules is often not fully displayed, as the diagram is otherwise unclear.

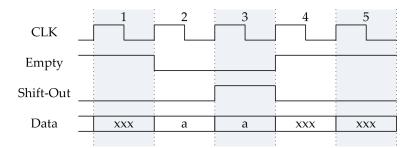

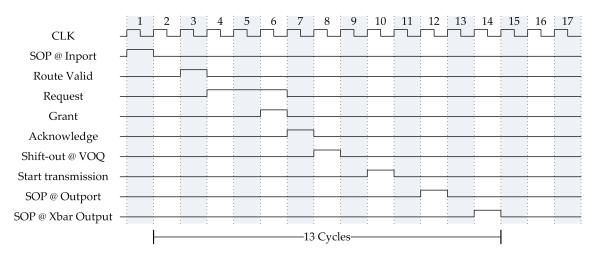

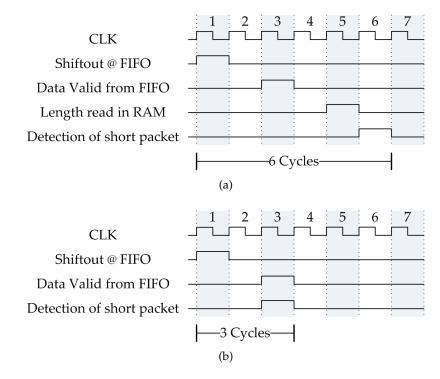

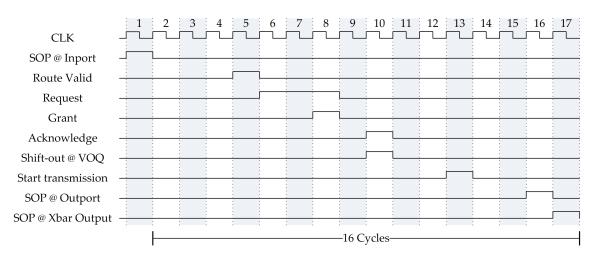

Figure 1.4: An Example Timing Diagram

The third used diagram in this thesis is a *timing diagram*. It illustrates a cycle accurate behavior of a module, unit or interface. The timing of each signal is given in dependency to a common clock. Using such diagrams enables to illustrate the latency of a module or the correct interaction between modules.

In figure 1.4 an example for such a timing diagram is given. In this example the interface between a module and a first-in-first-out (FIFO) buffer is illustrated. It shows a fall-through FIFO implementation, meaning the first data word stored inside is already visible at the output before data has actually been shifted out.

## 1.3 Outline

This thesis is divided into four main chapters. The first chapter introduces mechanisms and building blocks that reduce latency, enable an increase of the throughput, offload processing intensive tasks to specialized HW or ease the HW-designers work. They can be used in various environments that require high throughput and low latency processing. Additionally a low latency, high-throughput decode unit for the financial market is introduced.

The second chapter concentrates on crossbars in general and on Extended ATOLL (EXTOLL)'s crossbar design in particular. It discusses all made design decisions and explains their implementation. Performance is compared to a previous design and an outlook for future extensions is given.

The third chapter explains the functionality of EXTOLL with all its functional units (FUs) that facilitate EXTOLL achieve its outstanding performance values. All involved

#### 1 Introduction

units are explained and those which are part of this thesis are introduced in detail. Microbenchmark results of the complete design are given to underline the made contributions of the crossbar as well as the EXTOLL Network Interface Controller (NIC).

The final chapter closes this thesis with a reflection on the achievements and the impact of this work.

# 2 Efficient Packet Processing

All communication intensive computing tasks like Internet services, cloud computing, HFT or HPC require a lot of computing resources just handling incoming and outgoing packets due to the fact that the network gets faster with every new generation. However, the protocols themselves or the SW handling those networks often do not improve with the same rate. Ethernet for example is a network standard that has been introduced in 1980. More than 30 years later it is still the most often used protocol without any improvements. It requires a lot of processing power just to encode and decode the various framing layers.

The Internet is driven by Transmission Control Protocol (TCP) or User Datagram Protocol (UDP), both protocols work on top of Ethernet and are also widely used in HFT or HPC. The standard use case is kernel level communication, which always involves the operating system (OS). Kernel-level communication means that a SW thread hands over a packet to the OS and the system then issues the packet at the network adapter. This makes it necessary to copy packets to be sent at least one time inside main memory of the host system and involves at least one thread change from the user application to the OS. The same of course also applies for the reception of packets. All this makes kernel level communication very inefficient because resources are used for protocol handling which can otherwise be used to solve the actual workload.

Latency is often an issue, especially in timing critical applications like HFT, where every spared microsecond can be turned into possibly more profit. Reducing latency also increases the scalability of a network as the time required to traverse the network decreases making it possible to build larger networks. Efficient mechanisms are therefore necessary to reduce the workload of a single machine and reduce the latency.

The latency of a packet can be reduced using two mechanisms. Either it can be avoided by minimizing the required processing steps a packet as to pass, or it can be hidden by overlapping the processing of multiple packets. Both mechanisms can of course also be combined to get the best results.

Sometimes a change to a new type of interconnection network like switching from

Ethernet based systems to InfiniBand [7] or other high performance networks already increases the scalability by an order of magnitude. However, in some cases this might not be possible. The infrastructure at exchanges for example are a given and cannot be changed by companies actively trading there. But improving the performance in this environment is very critical for the longterm survival of companies involved in HFT on such exchanges.

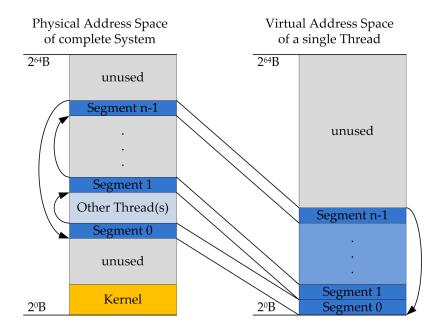

One commonly employed mechanism when improving performance of a network is to bypass the kernel of the OS and therefore do everything, including communication at the user-level. I/O devices must be virtualized in order to be able to handle them on the user-level. The virtualization is required so that devices can safely be mapped into the user-level address space, otherwise multiple applications can intervene each other when accessing devices or act as another process and therefore hijack a connection. Sophisticated Ethernet adapters like the ones offered by *Solarflare* [8] or the *QLogic* [9] InfiniBand adapters can be configured to bypass the kernel. This reduces the latency significantly, the computation and handling of packets on the other hand remains in the host Central Processing Unit (CPU).

To further improve the performance of a network two approaches are used, either *onloading* and *offloading*. *Onloading* tries to keep the HW as simple, and therefore fast, as possible and do most of the computation on the host CPU. The above mentioned QLogic InfiniBand adapter for example is very lean and QLogic promotes onloading [10] as the way to improve performance in the multi-core era.

*Offloading* is the exact opposite. It tries to put as much logic and packet processing tasks as possible into specialized HW as it often can process those tasks faster than a general purpose CPU, even if the CPU runs a lot faster than the HW.

Both approaches have their positive and negative sides and care has to be taken which approach is more beneficial for which task. There is no general rule that *onloading* or *offloading* is always better, it depends a lot on the task and the actual implementation whether or not it really is beneficial at the end. A trade-off has therefore to be made for every problem that has to be solved in order to get the best performing HW-SW co-design.

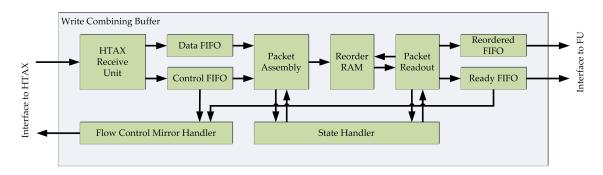

This chapter introduces two of the most often leveraged building blocks in chip designs, *arbiters* and *FIFOs*. Subsequently more sophisticated new HW structures are introduced that help to reduce the SW effort required for packet processing. In section 2.3 on page 22 the *Write Combining Buffer* is presented, a unit capable of reducing network traffic and simplifying both SW and HW for packet processing. In section 2.4 on page 24 a new HW

structure is introduced that is capable of efficiently maintaining large virtual ring buffers in main memory.

Section 2.5 on page 33 presents a module to parallelize the search of a communication partner when using Message Passing Interface (MPI) [11].

Finally in section 2.6 on page 42 an application of HW acceleration for HFT is shown. In contrast to section 2.5 on page 33, the proposed structure leverages the advantages of HW acceleration not by parallelizing independent tasks, but decoding a protocol which is highly serial in nature, using a specialized structure to process packets consecutively.

# 2.1 Arbiter Generator

Every chip design has some resources that are shared by several other resources. This is done for modules that are not performance critical or too complex, i.e. too large. Replicating them requires additional or too much area on the chip or field programmable gate array (FPGA). Thus, arbiters are a common building block required in almost every design. They are utilized to equally share that single structure whenever multiple units require access to it. In this case the arbiter makes sure that only one unit has access to the unique resource at a given time, but all units receive access sometime. Another scenario where arbiters are often deployed is to equally distribute elements generated by one instance to a number of units. This can for example be utilized to parallelize work and make sure all units have similar workloads.

Consumed area and maximum achievable clock frequency are the most important criteria for such arbiters. While being fast and small, they however also need to be fair. Fairness means two things, first there must be no starvation, i.e. no requesting unit has to wait for an indefinite time for the resource. Secondly, there must be no order or priority in any way, all units must be treated the same and receive access to the resource in the same amount.

The most commonly implemented arbiter is a *round-robin* arbiter. It selects the next grant by going through all set requests either clockwise or counterclockwise starting at the last given grant.

#### 2.1.1 State of the Art

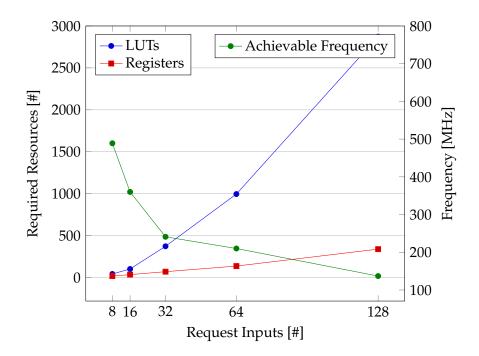

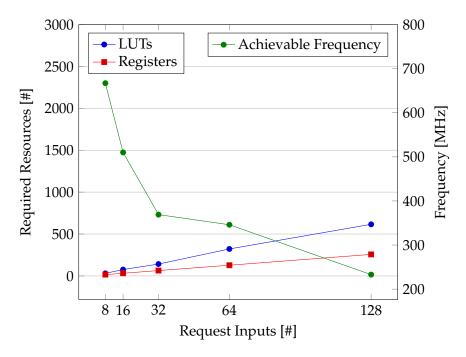

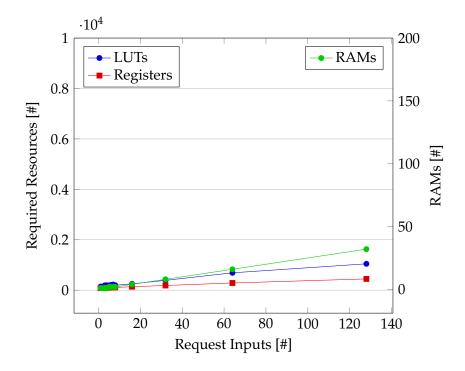

An arbiter generator has been developed at the Computer Architecture Group of the University of Heidelberg (CAG) by [12] which can be depicted using a finite state machine (FSM). Its size grows exponentially and its performance decreases accordingly with growing input numbers as it is shown in figure 2.1.

Figure 2.1: FSM based Arbiter Resource and Performance Evaluation

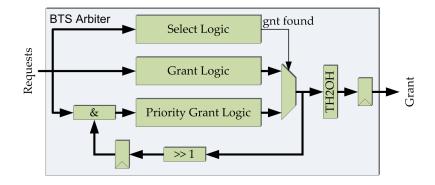

A good overview of other possible implementations is given in [13]. One particularly interesting is the one introduced in [14]. The arbiter proposed in this paper is based on a binary tree search (BTS) [15] to find the next request to be granted. It can be described best as two fixed priority arbiters that have been merged into a single one. A fixed priority arbiter is an arbiter which always finds the first request in the input vector. Thus, the first arbiter of these two finds the first request always starting at the very first bit position. The inputs of the other arbiter are masked by the last given grant and therefore finds the first request starting at the position of that last given grant. If the second arbiter finds a request, then its result is used, otherwise the result from the first arbiter is used.

The resulting block diagram is illustrated in figure 2.2 on the next page. Internally the arbitrer leverages a thermo code to implement the arbitration algorithm. This thermo code is then looped back to be used as mask and a thermo-to-one-hot code logic generates the one-hot coded output.

Figure 2.2: Simplified Block Diagram of the BTS Arbiter [14]

#### 2.1.2 Implementation

To prove the claims made in [14] a *Perl* [16] based script has been implemented to be able to generate arbiters with various variables. Configurable upon generation are not only the number of desired requests, but also which output encoding is to be used. Selectable are either binary, one-hot or both encodings. Further it can be decided whether or not an *any grant* signal is to be generated and whether or not a *stop* input is to be taken into account. Additionally all outputs of the generated arbiter can be either synchronous or asynchronous to a given clock. This feature can be used if one of the outputs is required for further logic within the instantiating module. However, these asynchronous outputs should only be used if very little additional logic is to be added before registering the results, as otherwise the clock frequency at which the design can operate decreases significantly.

Finally a rich set of *SystemVerilog* verification and coverage code [17] can be generated, making it easy to verify the correct functionality of the arbiter during simulation.

The BTS based arbiter design from [14] performs well in both area as well as timing. When comparing the results given in figure 2.1 on the facing page and figure 2.3 on the next page it can be seen that it scales significantly better as the previously used FSM based arbiter and achieves higher clock rates in any of the tested configurations. Its size increases only linear with growing input numbers. The increase is therefore significantly smaller than the one from the FSM based arbiter as it can be seen on both diagrams for look-up table (LUT) as well as register consumption.

Figure 2.3: BTS based Arbiter Resource and Performance Evaluation

# 2.2 FIFO Implementations

One of the most common building blocks in HW designs are FIFO buffers. The applications for FIFOs are versatile. They can for example be used to synchronize data between two clock domains, store data until an event happens or to decouple two modules. Often, additional logic is needed around these FIFOs to implement the required behavior. Therefore it is beneficial to have a set of different FIFOs with additional features at hand that can improve performance, simplify or reduce the latency of a design.

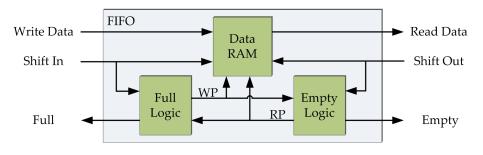

Figure 2.4: FIFO Block Diagram [18]

A FIFO is a HW storage structure where data can be pushed into or pulled from. The order of data is maintained while pushing data into or pulling data out of a FIFO. There are

two possible implementations to realize the FIFO functionality. It can either be described using a ring buffer or using shift registers.

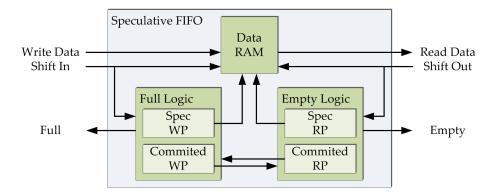

The ring buffer approach is realized using a random access memory (RAM) or a sea of registers for data storage and a set of a write- and a read pointer. The write pointer points to the next address to write data to and is thus incremented with every *shift-in* operation. The read pointer on the other hand points to the next data value that can be read and is incremented upon every *shift-out* operation. A block diagram of such a FIFO is shown in figure 2.4 on the facing page.

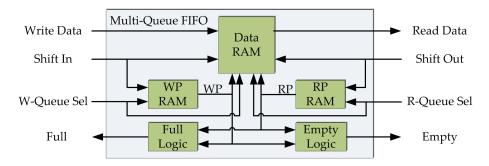

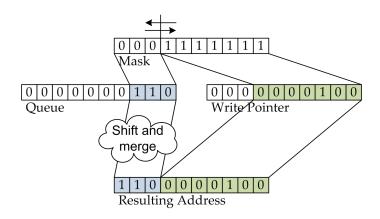

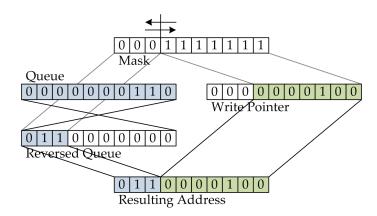

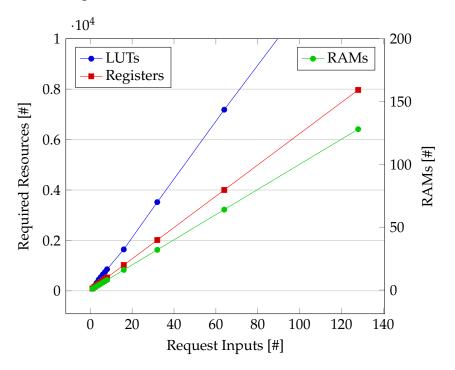

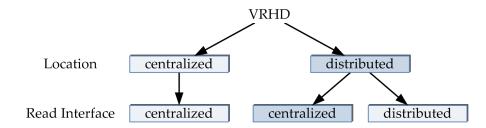

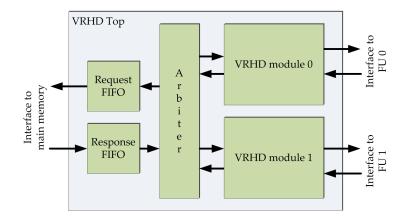

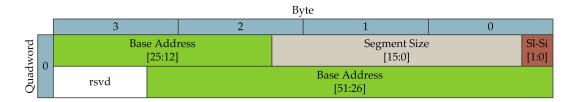

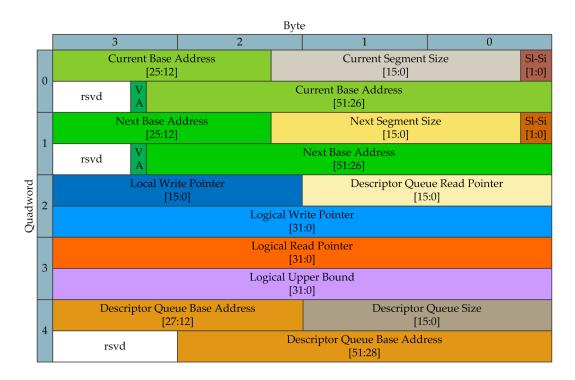

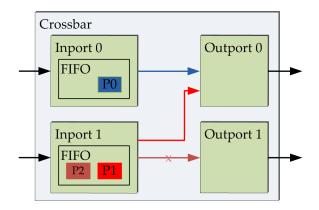

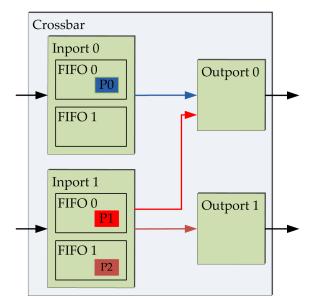

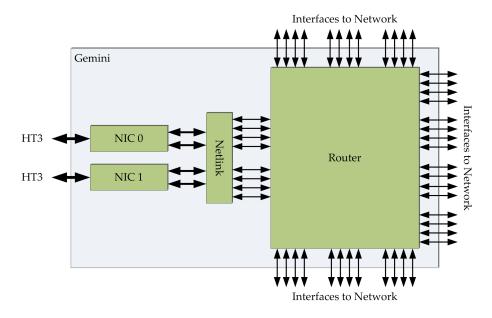

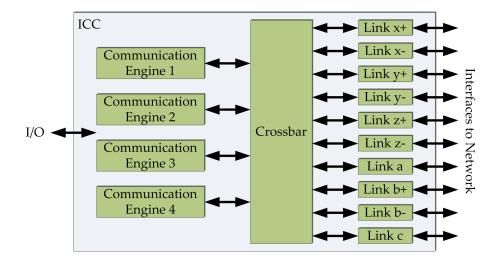

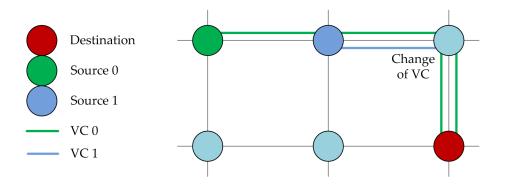

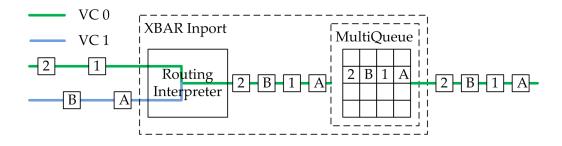

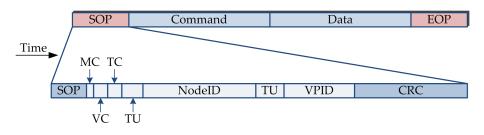

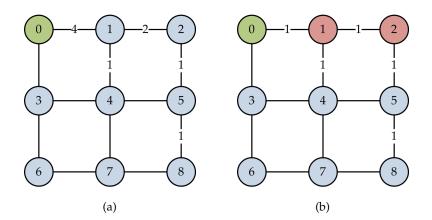

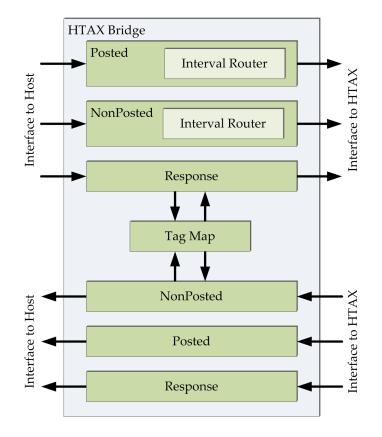

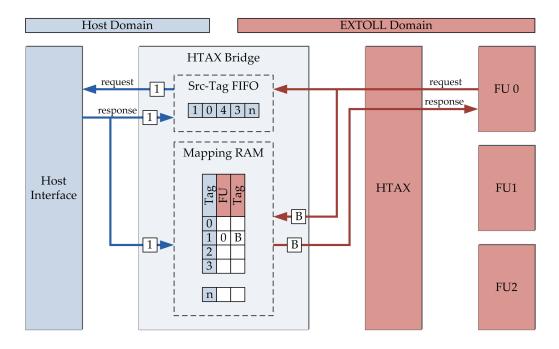

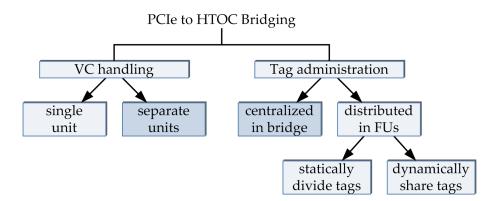

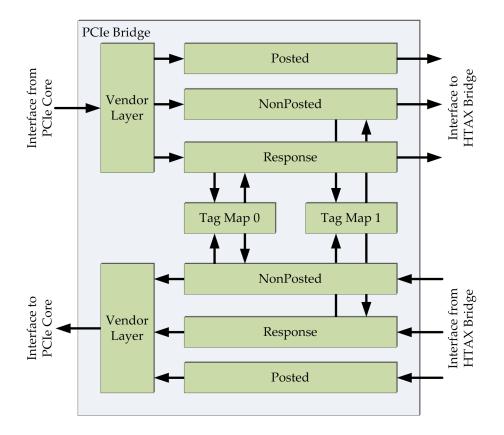

$$empty = (wp == rp) \tag{2.1}$$