# Das FPGA-Entwicklungssystem CHDL

# Eine vollständige, C++-basierte Entwicklungsumgebung für FPGA-Koprozessoren

Inauguraldissertation

zur Erlangung des akademischen Grades

eines Doktors der Naturwissenschaften

der Universität Mannheim

vorgelegt von

Diplom-Wirtschaftsinformatiker Klaus Kornmesser aus Mannheim

Mannheim, 2004

Dekan: Professor Dr. Jürgen Potthoff, Universität Mannheim

Referent: Professor Dr. Reinhard Männer, Universität Mannheim

Korreferent: Professor Dr. Peter Fischer, Universität Mannheim

Tag der mündlichen Prüfung: 12. Oktober 2004

# Inhaltsverzeichnis

| 1  | Lini  | enung und Mouvauon                                                        | 11       |

|----|-------|---------------------------------------------------------------------------|----------|

| 1  | Entv  | vicklungssoftware für FPGAs und FPGA-Koprozessoren                        | 12       |

|    | 1.1   | Einführung                                                                | 12       |

|    | 1.2   | Problembereiche                                                           | 12       |

|    |       | 1.2.1 Struktur eines FPGA-Koprozessors                                    | 12       |

|    |       | 1.2.2 Enge Kopplung zwischen Hardware- und Softwarebereich                | 13       |

|    |       | 1.2.3 Beherrschung von Umfang und Komplexität                             | 13       |

|    |       | 1.2.4 Realistische Simulation des Gesamtsystems                           | 14       |

|    |       | 1.2.5 Moderne Techniken zum Hardware-Debugging                            | 15       |

|    | 1.3   | Zusammenfassung                                                           | 15       |

| 2  | СНІ   | DL: Ein C++-basiertes Entwicklungssystem für FPGA-Koprozessoren           | 17       |

| _  | 2.1   | Einführung                                                                | 17       |

|    | 2.2   | Hardwarebeschreibung                                                      | 17       |

|    | 2.3   | Simulation                                                                | 18       |

|    | 2.4   | Synthese                                                                  | 19       |

|    | 2.5   | Hardware-Debugging                                                        | 19       |

|    | 2.6   | Zusammenfassung                                                           | 19       |

|    | 2.0   | Zusammemassung                                                            | 19       |

| II | Gr    | undlagen und Stand der Technik                                            | 20       |

| 2  | Diai  | tala Cahaltungataahnik                                                    | 21       |

| 3  | 3.1   | tale Schaltungstechnik Einführung                                         | 21       |

|    | 3.2   | Verknüpfungselemente                                                      | 21       |

|    | 3.3   | Schaltnetze                                                               | 21       |

|    | 3.4   |                                                                           | 23       |

|    |       | Speicherelemente                                                          | 23<br>24 |

|    | 3.5   | Zustandsmaschinen                                                         |          |

|    | 3.6   | Zeitverhalten von Schaltnetzen, Speicherelementen und Zustandsmaschinen . | 25       |

|    |       | 3.6.1 Schaltnetze                                                         | 25       |

|    |       | 3.6.2 Speicherelemente                                                    | 26       |

|    |       | 3.6.3 Zustandsmaschinen                                                   | 26       |

|    | 3.7   | Optimierung des Zeitverhaltens von Zustandsmaschinen                      | 27       |

|    |       | 3.7.1 Verringerung der Logikstufen                                        | 27       |

|    |       | 3.7.2 Sequentielle Bearbeitung von Operationen                            | 27       |

|    |       | 3.7.3 Pipelining                                                          | 28       |

|    |       | 3.7.4 Zerlegung von Zustandsmaschinen                                     | 29       |

| 4  | Field | l Programmable Gate Arrays (FPGAs)                                        | 30       |

|    | 4.1   | Einführung                                                                | 30       |

|    | 4.2   | Unterschiede zwischen FPGAs und konventionellen PLDs                      | 30       |

|    |       | 4.2.1 Anordnung der einzelnen Logikblöcke                                 | 30       |

|    |       | 4.2.2 Realisierung kombinatorischer Logik                                 | 31       |

|    |       | 4.2.3 Technologie der Konfigurationszellen                                | 32       |

|    |       | 4.2.4 Bedeutung für den Einsatzbereich von FPGAs                          | 32       |

|   | 4.3        | A robitalitur | der XILINX-FPGAs                                  |

|---|------------|---------------|---------------------------------------------------|

|   | 4.3        |               |                                                   |

|   |            | 4.3.1         | Allgemeines                                       |

|   |            | 4.3.2         | Configurable Logic Blocks (CLBs) und Slices       |

|   |            | 4.3.3         | I/O Blocks (IOBs)                                 |

|   |            | 4.3.4         | Block-RAMs (SelectRAM)                            |

|   | 4.4        | Anforderun    | gen an die Entwicklungswerkzeuge                  |

| 5 | FPG        | A-Koprozes    | soren 37                                          |

| • | 5.1        | _             |                                                   |

|   | 5.2        | _             | der FPGA-Koprozessoren                            |

|   | 5.3        | _             | Software-Codesign                                 |

|   | 5.5        | 5.3.1         | Pseudoregister (Special Function Registers, SFRs) |

|   |            | 5.3.2         |                                                   |

|   | <i>5</i> 1 |               | , , , , , , , , , , , , , , , , , , , ,           |

|   | 5.4        | Anwendung     | stypen von FPGA-Koprozessoren                     |

| 6 | Softv      |               | signentwicklung 42                                |

|   | 6.1        | Einführung    | 42                                                |

|   |            | 6.1.1         | Eingabe des Schaltungsentwurfes                   |

|   |            | 6.1.2         | Simulation                                        |

|   |            | 6.1.3         | Synthese                                          |

|   |            | 6.1.4         | Hardware-Debugging                                |

|   | 6.2        | Anforderun    | gen an ein optimales FPGA-Entwicklungssystem      |

|   |            | 6.2.1         | Einführung                                        |

|   |            | 6.2.2         | Hardwarebeschreibung                              |

|   |            | 6.2.3         | Simulation                                        |

|   |            | 6.2.4         | Synthese                                          |

|   |            | 6.2.5         | Hardware-Debugging                                |

|   | 6.3        |               | erte Entwicklungssysteme                          |

|   | 0.5        | 6.3.1         | 8                                                 |

|   |            |               | $\mathcal{E}$                                     |

|   |            | 6.3.2         | Hardwarebeschreibung                              |

|   |            | 6.3.3         | Simulation                                        |

|   | - 1        | 6.3.4         | Synthese                                          |

|   | 6.4        |               | 52                                                |

|   |            |               | Allgemeines                                       |

|   |            | 6.4.2         | Hardwarebeschreibung                              |

|   |            | 6.4.3         | Simulation                                        |

|   |            | 6.4.4         | Synthese                                          |

|   | 6.5        | JHDL          |                                                   |

|   |            | 6.5.1         | Allgemeines                                       |

|   |            | 6.5.2         | Hardwarebeschreibung                              |

|   |            | 6.5.3         | Simulation                                        |

|   |            | 6.5.4         | Synthese                                          |

|   | 6.6        | SystemC       | 57                                                |

|   |            | 6.6.1         | Allgemeines                                       |

|   |            | 6.6.2         | Hardwarebeschreibung                              |

|   |            | 6.6.3         | Simulation                                        |

|   |            | 6.6.4         | Synthese                                          |

|   | 6.7        |               | Version 3)                                        |

|   | 0.7        | 6.7.1         |                                                   |

|   |            |               | 8                                                 |

|   |            | 6.7.2         | Hardwarebeschreibung                              |

|   |            | 6.7.3         | Simulation                                        |

|   |            | 6.7.4         | Synthese                                          |

|   | 6.8        | •             | existierenden Systeme                             |

|   |            | 6.8.1         | Allgemeines                                       |

|     |       | 6.8.2<br>6.8.3<br>6.8.4 | Hardwarebeschreibung                                           | 66<br>68<br>69 |

|-----|-------|-------------------------|----------------------------------------------------------------|----------------|

| 7   | Zusa  | mmenfassui              | ng                                                             | 71             |

| III | . Da  | s FPGA-E                | ntwicklungssystem <i>CHDL</i>                                  | 73             |

| 8   | Einfi | ihrung                  |                                                                | 74             |

| 9   | Entw  | urfseingabe             | •                                                              | 75             |

|     | 9.1   | _                       | er optimalen universellen Programmiersprache für die Beschrei- |                |

|     |       |                         | ardware                                                        | 75             |

|     | 9.2   | _                       | ndigkeit mehrerer Abstraktionsebenen                           | 77             |

|     | 9.3   |                         | re Ausführungsmodelle                                          | 78             |

|     |       | 9.3.1                   | Das Ausführungsmodell von C++                                  | 78             |

|     |       | 9.3.2                   | Strukturelle Hardwarebeschreibung                              | 79             |

|     |       | 9.3.3                   | Verhaltensbeschreibung von Zustandsmaschinen                   | 79             |

|     | 9.4   |                         | Hardwarebeschreibung mit C++                                   | 82             |

|     |       | 9.4.1                   | Überblick                                                      | 82             |

|     |       | 9.4.2                   | Die Objektverwaltung                                           | 83             |

|     |       | 9.4.3                   | Die Hierarchieverwaltung                                       | 83             |

|     |       | 9.4.4                   | Die Lebensdauer von Objekten                                   | 84             |

|     |       | 9.4.5                   | Die eindeutige und nachvollziehbare Benennung der Objekte      |                |

|     |       | 0.46                    | zur Laufzeit                                                   | 84             |

|     |       | 9.4.6                   | Die Verwaltung von Netzen                                      | 85             |

|     |       | 9.4.7                   | Die Auswertung von Schaltfunktionen                            | 85             |

|     |       | 9.4.8                   | Vereinfachung der Schreibweise                                 | 87             |

|     |       | 9.4.9                   | Frühzeitige und präzise Erkennung von Fehlern                  | 88             |

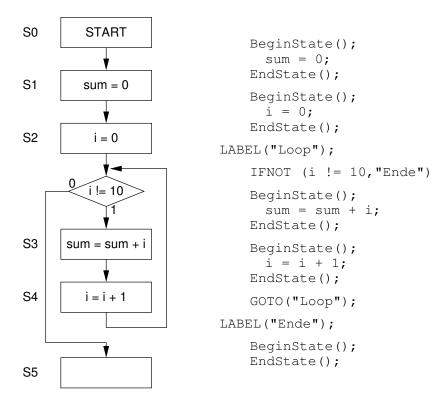

|     |       | 9.4.10                  | Implementierung von architekturunabhängigen Grundelementen     | 89             |

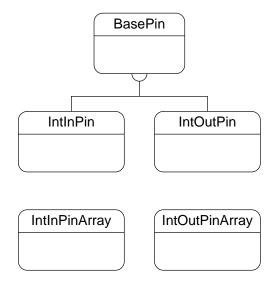

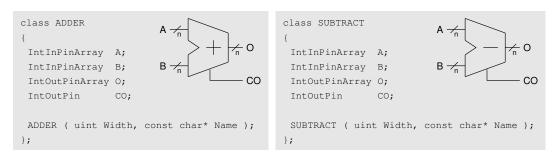

|     | o =   | 9.4.11                  | Übersicht über die Pin- und Bauteilklassen                     | 91             |

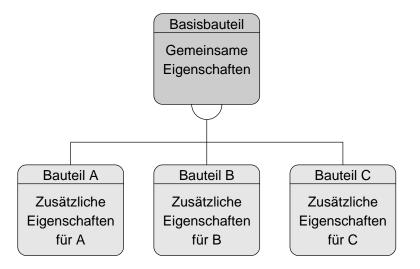

|     | 9.5   | Modularisie             |                                                                | 93             |

|     |       | 9.5.1                   | Bedeutung der Modularisierung                                  | 93             |

|     |       | 9.5.2                   | Erstellen von CHDL-Modulen                                     | 93             |

|     |       | 9.5.3                   | Aufbau von Anwenderbibliotheken                                | 95             |

|     | 9.6   | •                       | erung von Zustandsmaschinen                                    | 95             |

|     |       | 9.6.1                   | Modifizierte <i>Moore</i> -Maschine                            | 95             |

|     |       | 9.6.2                   | One-Hot-Encoding                                               | 96             |

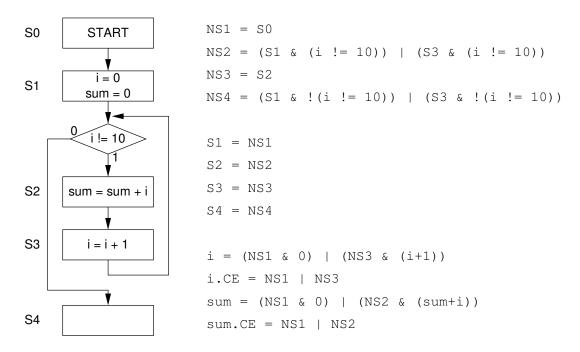

|     |       | 9.6.3                   | Flußdiagramme zur Beschreibung von Zustandsmaschinen           | 96             |

|     |       | 9.6.4                   | Automatische Erzeugung von Zustandsmaschinen aus Flußdia-      |                |

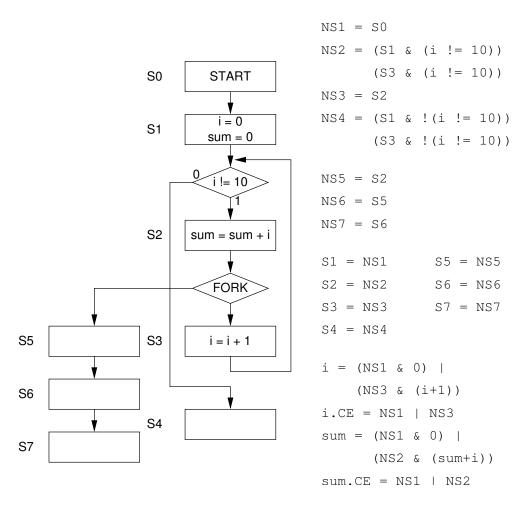

|     |       |                         | grammen                                                        | 96             |

|     |       | 9.6.5                   | Optimierungsmöglichkeiten                                      | 98             |

|     |       | 9.6.6                   | Mehrere Threads in Zustandsmaschinen                           |                |

|     |       | 9.6.7                   | Beschreibung von Zustandsmaschinen in <i>CHDL</i>              |                |

|     |       | 9.6.8                   | Pipeline-Kontroller                                            |                |

|     |       | 9.6.9                   | Unterstützung von Pipeline-Kontrollern in CHDL                 |                |

|     | 9.7   | _                       | g der Hardwarebeschreibung                                     |                |

|     |       | 9.7.1                   | Allgemeines                                                    |                |

|     |       | 9.7.2                   | CHDL-Grundelemente                                             | 105            |

|     |       | 9.7.3                   | Strukturelle Schaltungen                                       | 108            |

|     |       | 9.7.4                   | Vererbung und Polymorphismus                                   |                |

|     |       | 9.7.5                   | Zustandsmaschinen                                              | 113            |

|     | 9.8   | Vergleich de            | er CHDL-Beschreibung zu anderen Systemen                       |                |

|    |       | 9.8.1                                                                                 | SL - Structured Design Language                 | 115 |  |

|----|-------|---------------------------------------------------------------------------------------|-------------------------------------------------|-----|--|

|    |       | 9.8.2                                                                                 | Pebble                                          |     |  |

|    |       | 9.8.3                                                                                 | Codegenerator nach Chu/Weaver/Sulimma           |     |  |

|    |       | 9.8.3<br>9.8.4                                                                        | _                                               |     |  |

|    |       |                                                                                       | JHDL                                            |     |  |

|    |       | 9.8.5                                                                                 | PamDC                                           |     |  |

|    | 0.0   | 9.8.6                                                                                 | CHDL                                            |     |  |

|    | 9.9   | Zusamment                                                                             | assung                                          | 118 |  |

| 10 | Simu  | lation                                                                                |                                                 | 120 |  |

| 10 |       |                                                                                       | C++ zur Simulation von Hardwarebeschreibungen   |     |  |

|    |       |                                                                                       | rungsmodell der <i>CHDL</i> -Simulation         |     |  |

|    |       |                                                                                       | entierung des <i>CHDL</i> -Simulators           |     |  |

|    | 10.5  | 10.3.1                                                                                | Simulierte Logikzustände                        |     |  |

|    |       |                                                                                       |                                                 |     |  |

|    |       | 10.3.2                                                                                | Initialisierung der Simulation                  |     |  |

|    | 10.4  | 10.3.3                                                                                | Simulation der Teilschritte                     |     |  |

|    | 10.4  |                                                                                       | methoden                                        |     |  |

|    |       | 10.4.1                                                                                | Anlegen von Testvektoren                        |     |  |

|    |       | 10.4.2                                                                                | Implementierung von Testbenches                 |     |  |

|    |       | 10.4.3                                                                                | Hierarchische Simulation                        |     |  |

|    |       | 10.4.4                                                                                | Auswertung der Simulationsergebnisse            |     |  |

|    | 10.5  | Spezielle Si                                                                          | mulationsverfahren                              |     |  |

|    |       | 10.5.1                                                                                | Zugriffe auf Special-Function-Register          | 132 |  |

|    |       | 10.5.2                                                                                | Rekonfiguration von FPGAs                       |     |  |

|    |       | 10.5.3                                                                                | Simulation mehrerer FPGAs                       | 136 |  |

|    |       | 10.5.4                                                                                | Dynamisches Einbinden von Simulationsfunktionen | 136 |  |

|    | 10.6  | Zusammenf                                                                             | assung                                          | 138 |  |

|    | g 41  |                                                                                       |                                                 | 120 |  |

| 11 | Syntl |                                                                                       |                                                 | 139 |  |

|    |       |                                                                                       | s                                               |     |  |

|    |       |                                                                                       | sten                                            |     |  |

|    | 11.3  |                                                                                       | isten                                           |     |  |

|    | 11.4  | VHDL-Expo                                                                             | ort                                             | 145 |  |

| 12 | Llond | lware-Debug                                                                           | raina                                           | 148 |  |

| 14 |       | _                                                                                     | eit und Probleme des Hardware-Debugging         |     |  |

|    |       |                                                                                       | ck-Verfahren bei FPGAs                          |     |  |

|    | 12.2  |                                                                                       |                                                 |     |  |

|    |       | 12.2.1                                                                                | Allgemeines                                     |     |  |

|    |       | 12.2.2                                                                                | $\varepsilon$ 1                                 |     |  |

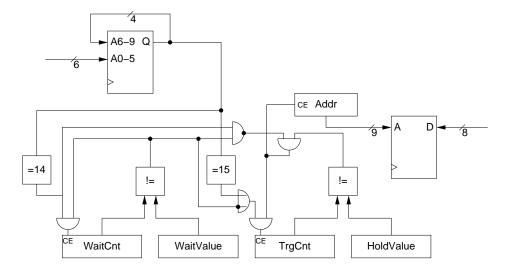

|    | 10.0  | 12.2.3                                                                                | Realisierung eines Logikanalyzers im Design     |     |  |

|    | 12.3  | _                                                                                     | rungen ohne erneutes Place&Route                |     |  |

|    |       | 12.3.1                                                                                | Einsatz von LUTs und partieller Rekonfiguration |     |  |

|    |       | 12.3.2                                                                                | Fernsteuerung des FPGA-Editor                   |     |  |

|    | 12.4  | Zusammenf                                                                             | assung                                          | 156 |  |

|    |       |                                                                                       |                                                 |     |  |

| IV | Ho    | chspracher                                                                            | norientierte Hardwarebeschreibung mit CHDL      | 157 |  |

| 12 | L:-c  | ihmma                                                                                 |                                                 | 150 |  |

| 13 |       | ihrung<br>Dia Problem                                                                 | notik haakanvaahanaviantiavtav Basahvaikuvaan   | 158 |  |

|    |       |                                                                                       | natik hochsprachenorientierter Beschreibungen   |     |  |

|    |       |                                                                                       | gen an eine Hochsprache                         |     |  |

|    | 13.3  | 3.3 Das Konzept der hochsprachenorientierten Hardwarebeschreibung mit <i>CHDL</i> 160 |                                                 |     |  |

| 14 |       | _             | CHDL-Hochsprachenkompilers                                 | 161 |

|----|-------|---------------|------------------------------------------------------------|-----|

|    |       |               |                                                            |     |

|    | 14.2  | Implementie   | erung von Variablen                                        | 161 |

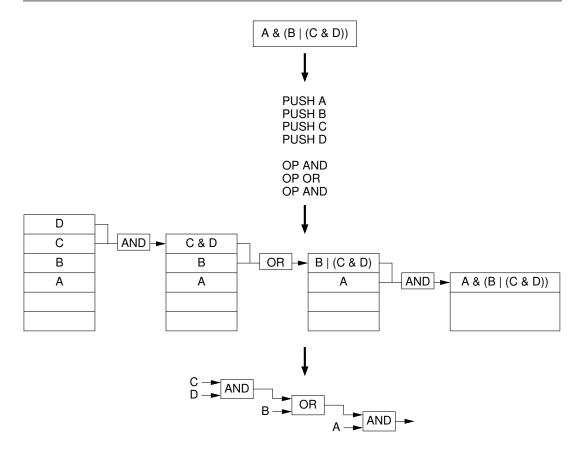

|    | 14.3  | Auswertung    | g arithmetischer Ausdrücke                                 |     |

|    |       | 14.3.1        | , , , , , , , , , , , , , , , , , , , ,                    |     |

|    |       |               | Der Arithmetikstack                                        |     |

|    |       |               | Die Anweisungen des Bytecodes                              |     |

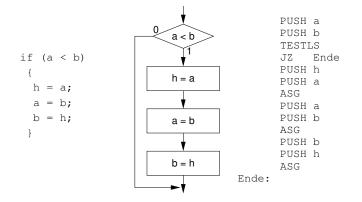

|    | 14.4  | Kontrollanw   | veisungen                                                  | 165 |

|    |       | 14.4.1        | Allgemeines                                                | 165 |

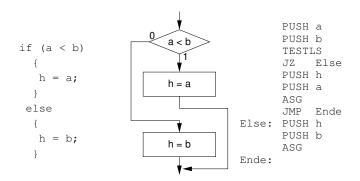

|    |       | 14.4.2        | Die if-Anweisung                                           | 166 |

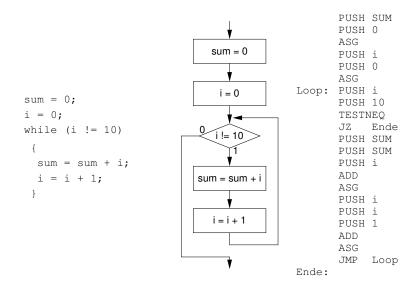

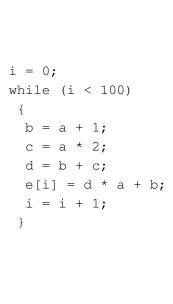

|    |       | 14.4.3        | Die while-Anweisung                                        |     |

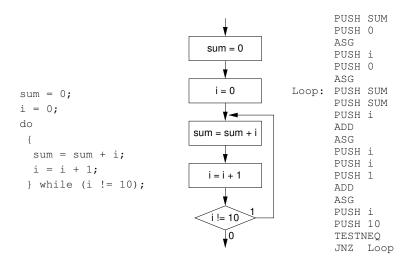

|    |       | 14.4.4        | Die dowhile-Anweisung                                      |     |

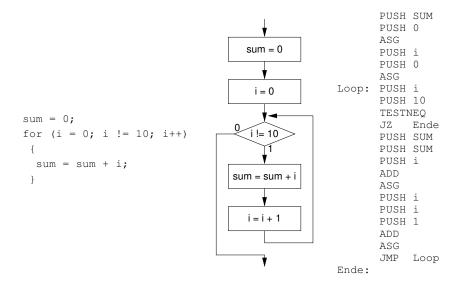

|    |       | 14.4.5        | Die for-Anweisung                                          |     |

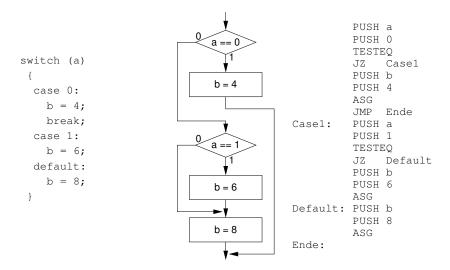

|    |       | 14.4.6        | Die switch-Anweisung                                       |     |

|    | 14.5  | Implemention  | erung von Funktionsaufrufen                                |     |

|    |       | 14.5.1        | Allgemeines                                                |     |

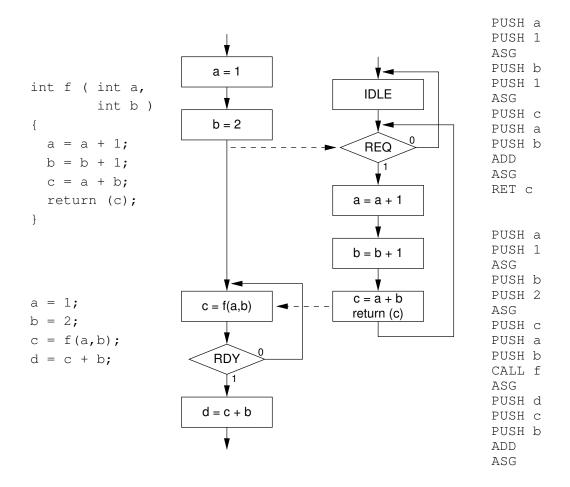

|    |       | 14.5.2        | Einfacher Funktionsaufruf                                  |     |

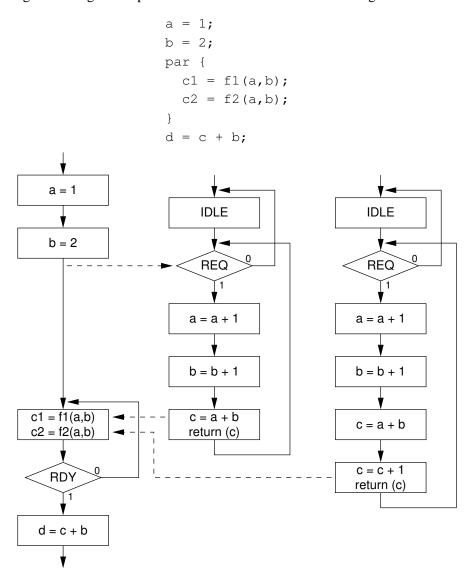

|    |       | 14.5.3        | Parallele Funktionsaufrufe                                 |     |

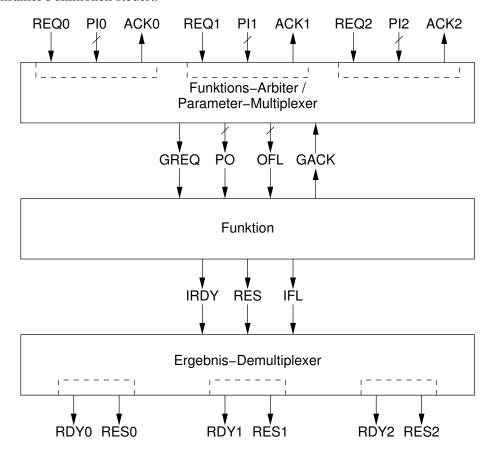

|    |       | 14.5.4        | Aufrufe gemeinsam verwendeter Funktionen                   |     |

|    | 14.6  |               | ng für Parallelität                                        |     |

|    |       | 14.6.1        | Parallele Anweisungen                                      |     |

|    |       | 14.6.2        | Parallele Ablaufpfade                                      |     |

|    |       | 14.6.3        | Synchronisierung paralleler Ablaufpfade                    |     |

|    |       | 14.6.4        | Spezifizierung von Parallelität                            |     |

|    |       | 14.6.5        | Implizite Parallelität                                     |     |

|    |       | 14.6.6        | Explizite Parallelität                                     |     |

|    |       | 14.6.7        | Realisierung von Mutex-Elementen                           |     |

|    | 14.7  |               | ng für Pipelining                                          |     |

|    |       | 14.7.1        | Implementierung von Pipelines                              |     |

|    |       | 14.7.2        | Bedeutung der Datenabhängigkeiten                          |     |

|    |       | 14.7.3        | Pipelining in Hochsprachenbeschreibungen                   |     |

|    |       | 14.7.4        | Nicht pipelinefähige Algorithmen                           |     |

|    | 14.8  |               | stelle zur strukturellen <i>CHDL</i> -Hardwarebeschreibung |     |

|    |       |               | Allgemeines                                                |     |

|    |       | 14.8.2        | Anwendungsbeispiel                                         | 184 |

| 15 | Verg  | leich mit and | leren Hochsprachensystemen                                 | 188 |

|    | 15.1  | SystemC       |                                                            | 188 |

|    | 15.2  | Handel-C.     |                                                            | 189 |

| 16 | Zusa  | mmenfassur    | ng                                                         | 190 |

|    |       |               |                                                            |     |

| V  | Ges   | amtbewert     | ung und Ausblick                                           | 191 |

| 17 | Errei | ichte Ziele   |                                                            | 192 |

|    |       |               | zept                                                       |     |

|    |       |               | schreibung                                                 |     |

|    |       | 17.2.1        | Allgemeines                                                |     |

|    |       | 17.2.2        | Strukturelle Ebene                                         |     |

|    |       | 17.2.3        | Zustandsmaschinenbeschreibung                              |     |

|    |       | 17.2.4        | Hochsprachenebene                                          |     |

|    | 17.3  | Simulation    | *                                                          |     |

|    | 17.4  | Synthese un   | d Hardware-Debugging                                       |     |

|    |       |               |                                                            |     |

| 18 | Bish | erige Einsatz | bereiche und Entwicklungsstand des CHDL-Systems           | 196 |

|----|------|---------------|-----------------------------------------------------------|-----|

|    |      | _             | insatzbereiche von <i>CHDL</i>                            | 196 |

|    |      | •             | schinenbeschreibung                                       |     |

|    |      |               | enorientierte Beschreibung                                |     |

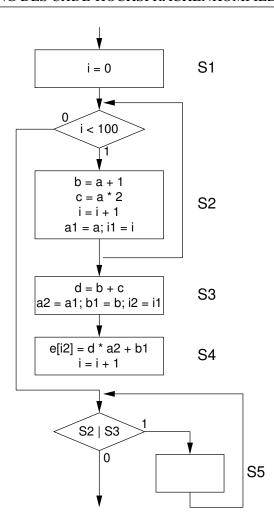

|    |      | 18.3.1        | Hochsprachenparser                                        |     |

|    |      | 18.3.2        | Hardware Virtual Machine (HVM)                            |     |

| 19 | Aush | lick          |                                                           | 198 |

|    | 19.1 | Akzeptanzp    | robleme kommerzieller Anwender                            | 198 |

|    |      | 19.1.1        | Umfangreiche existierende VHDL-Bibliotheken               | 198 |

|    |      | 19.1.2        | Kommerzielle Anwender sind skeptisch gegenüber dem, was   |     |

|    |      |               | nicht verbreiteter Standard ist                           | 198 |

|    |      | 19.1.3        | Weiterentwicklung                                         | 198 |

|    |      | 19.1.4        | Schnelle Fehlerbeseitigung                                |     |

|    | 19.2 | Mögliche W    | Veiterentwicklungen                                       |     |

|    |      | 19.2.1        | Verbesserte Schnittstellen zu klassischen Systemen        |     |

|    |      | 19.2.2        | Kombination der CHDL-Simulation mit anderen Systemen      |     |

|    |      | 19.2.3        | Kombination des CHDL-Hardware-Debuggings mit anderen Sys- |     |

|    |      |               | temen                                                     | 199 |

|    |      | 19.2.4        | Gestaltung offener Schnittstellen                         | 199 |

|    |      | 19.2.5        | Optimierung des Gesamtentwicklungsprozesses               |     |

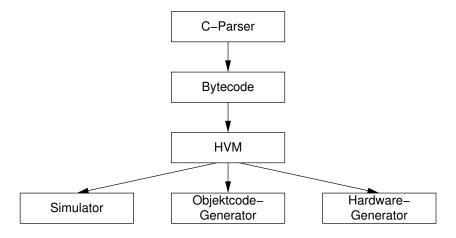

|    |      | 19.2.6        | Erweiterungen der <i>Hardware Virtual Machine</i> (HVM)   |     |

# Abbildungsverzeichnis

| 1.1  | Probleme bei der Simulation des Gesamtsystems        |    |

|------|------------------------------------------------------|----|

| 3.1  | Darstellung einiger Verknüpfungselemente             | 21 |

| 3.2  | Ergebnisse einiger Schaltfunktionen                  | 22 |

| 3.3  | Ein Schaltnetz                                       | 22 |

| 3.4  | Verschiedene Typen von Speicherelementen             | 24 |

| 3.5  | Mealy- und Moore-Zustandsmaschine                    | 25 |

| 3.6  | Ein Zustandsdiagramm                                 | 25 |

| 3.7  | Zeitverhalten in Schaltnetzen                        | 25 |

| 3.8  | Zeitverhalten eines D-Flip-Flops und eines D-Latches | 26 |

| 3.9  | Zeitverhalten bei Zustandsmaschinen                  | 27 |

| 3.10 | Optimierung von Schaltnetzen nach Logikstufen        | 28 |

| 3.11 | Pipeline-Verfahren                                   | 29 |

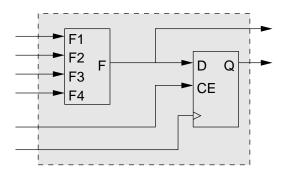

| 4.1  | Grundprinzip der FPGAs                               | 30 |

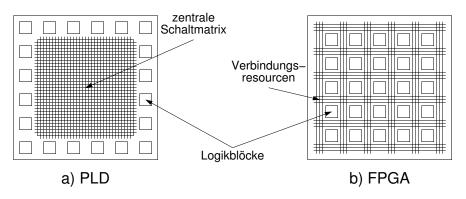

| 4.2  | Anordnung der Logikblöcke bei PLDs und FPGAs         | 31 |

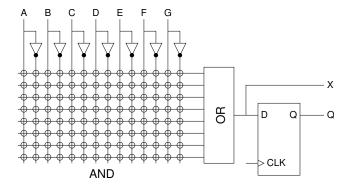

| 4.3  | Aufbau einer PLD-Logikzelle                          | 32 |

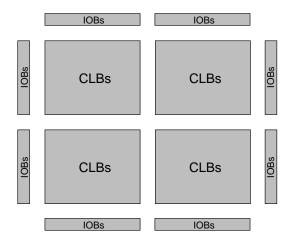

| 4.4  | Virtex Blockdiagramm                                 | 34 |

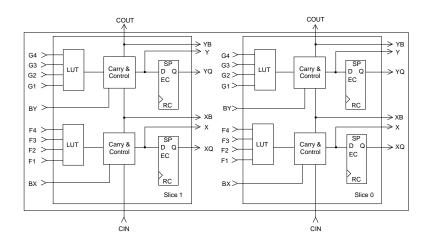

| 4.5  | Virtex / Spartan-II: Configurable Logic Block        | 34 |

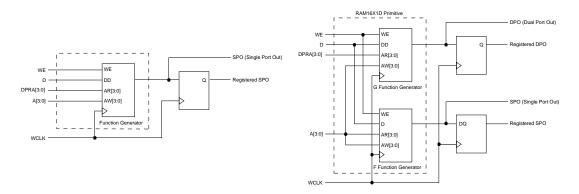

| 4.6  | Virtex Distributed RAM                               | 34 |

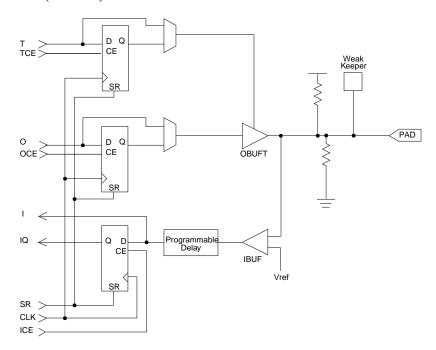

| 4.7  | Virtex I/O Block                                     | 35 |

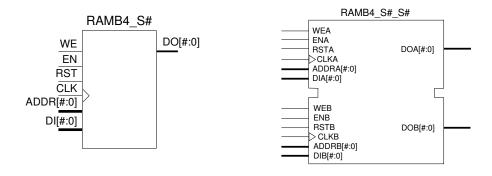

| 4.8  | Virtex SelectRAM                                     | 35 |

|      |                                                      |    |

| 5.1  | Struktur eines FPGA-Koprozessors                     | 38 |

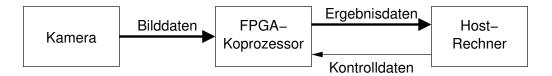

| 5.2  | FPGA-Koprozessor mit externer Datenquelle            | 41 |

| 5.3  | Hostrechner liefert und nimmt Daten ab               | 41 |

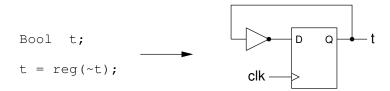

| 6.1  | Erzeugen von Speicherelementen                       | 52 |

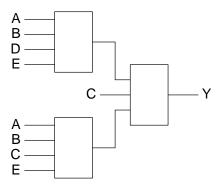

| 6.2  | Verschalten von vordefinierten Elementen             | 53 |

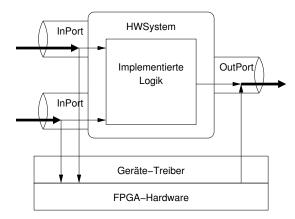

| 6.3  | Systemschnittstelle von JHDL                         | 56 |

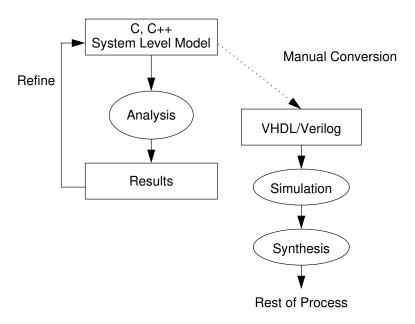

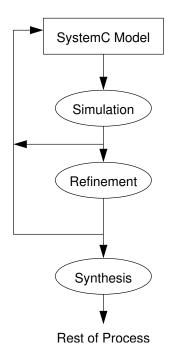

| 6.4  | Konventionelle Designmethode                         | 58 |

| 6.5  | <i>SystemC</i> -Designmethode                        | 58 |

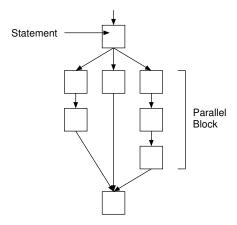

| 6.6  | Handel-C: Branching und Re-Joining                   | 62 |

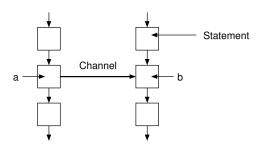

| 6.7  | Handel-C: Channels                                   | 62 |

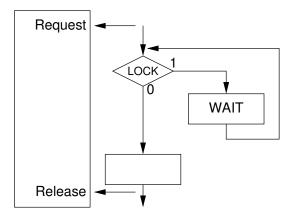

| 6.8  | Handel-C: Zugriff auf gemeinsame Resourcen           | 63 |

| 6.9  | Übersicht der Entwicklungssysteme                    | 70 |

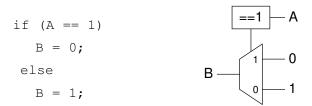

| 9.1  | if realisiert einen Multiplexer                      | 80 |

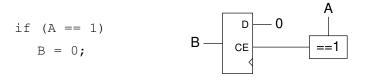

| 9.2  | if ersetzt Clock-Enable                              | 81 |

| 9.3  | Strukturelle Beschreibung                            | 85 |

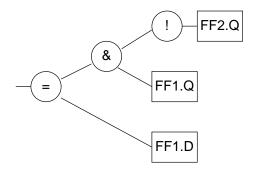

| 9.4  | Auswertungsbaum                                      | 86 |

| 9.5  | Partitionierung der Logik auf LUTs                   | 87 |

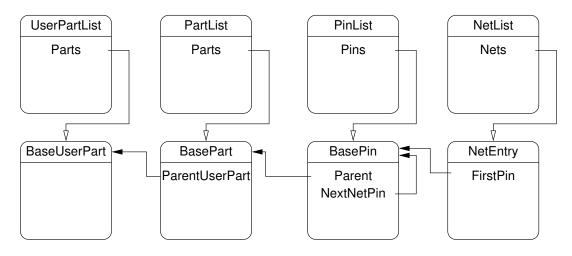

| 9.6  | CHDL-Verwaltungsklassen                              | 91 |

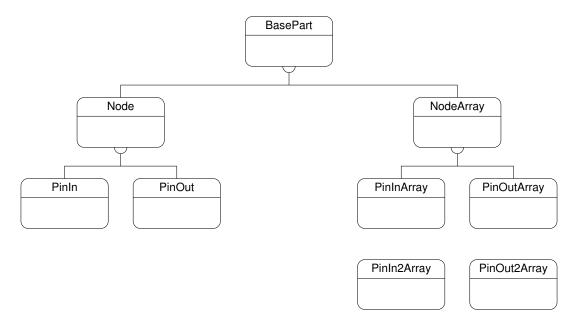

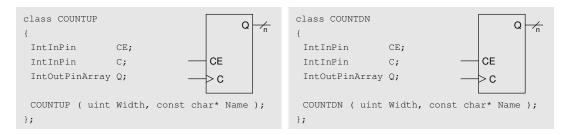

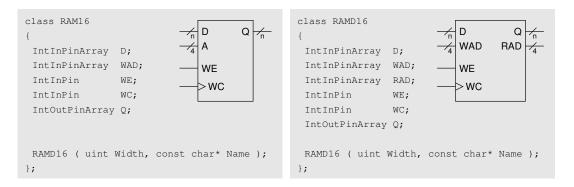

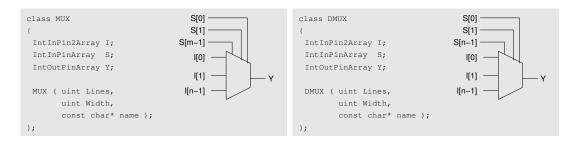

| 9.7  | CHDL-Pin-Klassen                                     | 92 |

| 9.8  | CHDL-Node-Klassen                                    | 92 |

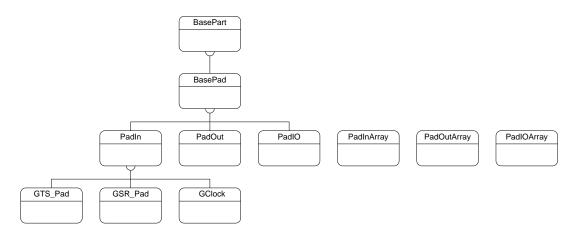

| 9 9  | CHDI_Pad_Klassen                                     | 92 |

| 9.10  | Modifizierte <i>Moore-</i> Zustandsmaschine  | 95  |

|-------|----------------------------------------------|-----|

| 9.11  | Darstellung als Flußdiagramm                 |     |

| 9.12  | Bildung der Gleichungen                      |     |

| 9.13  | Zustandsmaschine mit mehreren Threads        |     |

| 9.14  | CHDL-Beschreibung eines Flußdiagrammes       |     |

| 9.15  | Eingangs- und Ausgangs-Pads                  |     |

| 9.16  | D-Flip-Flops und D-Latches                   |     |

| 9.17  | n-Bit Addierer / Subtrahierer                |     |

| 9.18  | n-Bit binärer Aufwärts-/Abwärtszähler        |     |

| 9.19  | 16 x n Bit Single- / Dual-Port-Speicher      |     |

| 9.20  | n-Bit Multiplexer                            |     |

| 9.21  | n-Bit Vergleicher                            |     |

| 9.22  | Vererbung bei <i>CHDL</i> -Bauteilen         |     |

| 10.1  | Simulation mit parallelen Prozessen          | 123 |

| 10.2  | Eventbasierte Simulation                     | 123 |

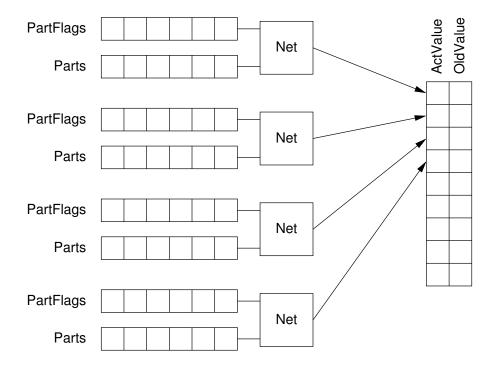

| 10.3  | Datenstrukturen des Simulatorkerns           | 124 |

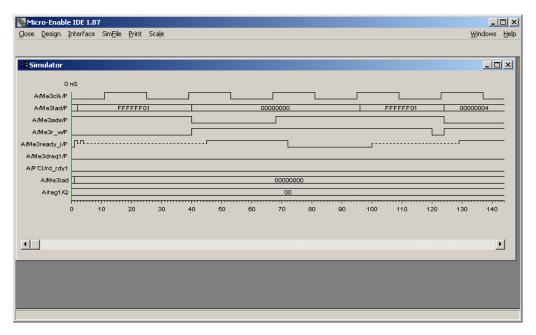

| 10.4  | Grafische Darstellung der Signalverläufe     | 131 |

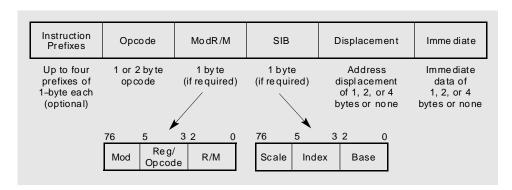

| 10.5  | Aufbau eines Intel x86-Befehls               | 134 |

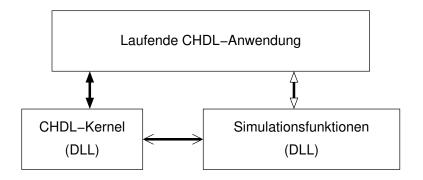

| 10.6  | Einbinden von Simulationsfunktionen aus DLLs | 137 |

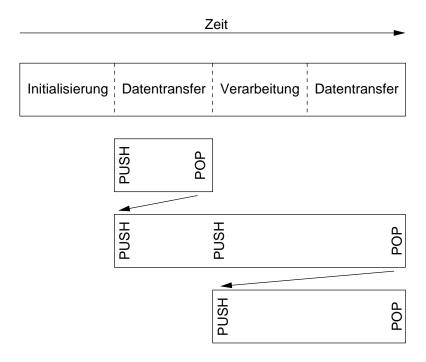

| 10.7  | Verwendung von Sicherungspunkten             | 137 |

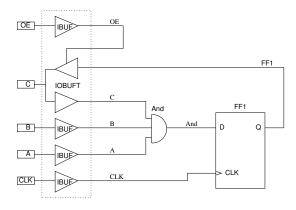

| 11.1  | Beispielschaltung für die Netzlistenformate  | 139 |

| 12.1  | Integrierter Logic Analyzer                  | 154 |

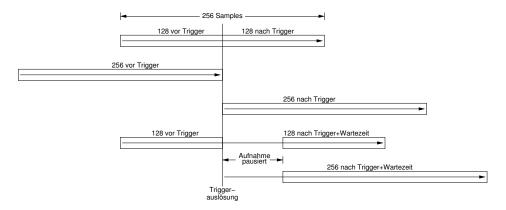

| 12.2  | Triggereinheit                               | 154 |

| 12.3  | Triggerzeiträume                             | 155 |

| 14.1  | Operatorprioritäten von C/C++                |     |

| 14.2  | Die Auswertung von Ausdrücken mittels Stack  |     |

| 14.3  | IF-Anweisung                                 | 166 |

| 14.4  | IFELSE-Anweisung                             |     |

| 14.5  | WHILE-Schleife                               |     |

| 14.6  | DOWHILE-Schleife                             | 168 |

| 14.7  | FOR-Schleife                                 |     |

| 14.8  | SWITCH-Anweisung                             |     |

| 14.9  | Funktionsaufruf                              |     |

|       | Parallele Funktionsaufrufe                   |     |

| 14.11 | Kontroller für Funktionsaufrufe              | 173 |

|       | Mutex-Element                                |     |

|       | Aufbau der Pipeline-Struktur                 |     |

|       | Nicht pipelinefähige Funktion                |     |

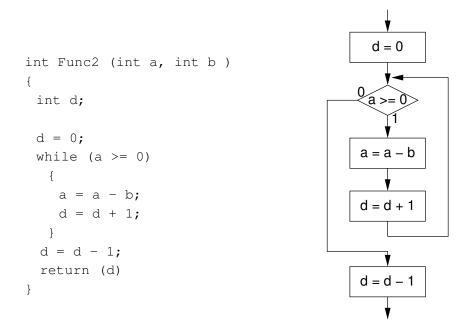

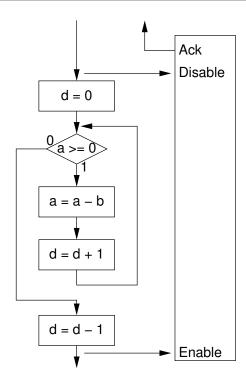

|       | Regelmechanismus für Func 2                  |     |

| 14.16 | Ablauf in Pipeline-Form                      | 184 |

| 19.1  | Erweiterter Einsatz der HVM                  | 200 |

# Teil I Einleitung und Motivation

# Kapitel 1

# Entwicklungssoftware für FPGAs und FPGA-Koprozessoren

#### 1.1 Einführung

Field Programmable Gate Arrays (FPGAs) haben durch ihr breites Anwendungsgebiet und ihre immer weiter steigende Integrationsdichte die Welt der konfigurierbaren Logik bedeutend verändert. Die Erstellung von Designs für Programmable Logic Devices (PLDs) war noch überschaubar und mit einfachen Entwicklungswerkzeugen beherrschbar. FPGAs dagegen beinhalten weitaus mehr konfigurierbare Resourcen als PLDs und die Entwicklungssysteme zur Designerstellung für FPGAs sind deutlich komplexer geworden.

Insbesondere FPGA-basierte Koprozessoren, die zur Hardwarebeschleunigung von Algorithmen eingesetzt werden, stellen durch ihr enges Zusammenwirken mit Mikroprozessoren besondere Anforderungen an die Entwicklungssysteme. Die Anwendungen können einen erheblichen Umfang und Komplexitätsgrad erreichen. Daher werden höhere und abstraktere Beschreibungsebenen benötigt. Auch eine Simulation des Gesamtsystems ist unverzichtbar. Debugging-Verfahren müssen durch zusätzliche Funktionen moderner FPGAs, wie etwa das Readback-Verfahren [118] und die partielle Rekonfiguration [116] ergänzt werden. Zur optimalen Designerstellung müssen alle diese Bereiche in geeigneter Weise durch die Entwicklungssysteme unterstützt werden.

Neben den konventionellen VHDL [104]-basierten Systemen wie etwa Leonardo Spectrum [64], Synplify [93] oder FPGA Express / FPGA Compiler II [92] sind in den letzten Jahren auch neue Entwicklungssysteme entstanden. Die bedeutendsten sind Handel-C [20], SystemC [95], JHDL [9] und PAM-Blox [62], die in unterschiedlicher Form C, C++ oder auch JAVA zur Hardwarebeschreibung einsetzen. Einige davon sind als Klassenbibliotheken realisiert und besitzen keine eigenen, speziellen Kompiler zur Übersetzung der Hardwarebeschreibung, sondern verwenden handelsübliche C++ oder JAVA-Kompiler.

Jedoch berücksichtigen sowohl die konventionellen als auch die neuen Entwicklungssysteme die oben genannten Anforderungen der FPGA-Koprozessoren nicht ausreichend. Insbesondere existiert kein System, das alle diese Anforderungen in gleichem Maße erfüllt. Die vorhandenen Systeme weisen darüberhinaus heterogene Strukturen auf, die den Gesamtentwicklungsprozeß nicht optimal unterstützen können.

In der vorliegenden Arbeit wurde das Konzept der C++-basierten Hardwarebeschreibung mittels Klassenbibliotheken und handelsüblichen Kompilern weiterentwickelt und optimiert. Das Ergebnis ist ein homogenes System, das eine deutlich verbesserte Unterstützung für FPGA-Koprozessoren bietet: Das FPGA-Entwicklungssystem *CHDL*.

*CHDL* verfügt über mehrere parallel einsetzbare Beschreibungsebenen von der detaillierten strukturellen Spezifikation bis hin zur modernen Hochsprachenbeschreibung. Die Simulation von Gesamtsystemen wird ebenso unterstützt wie die Anwendung moderner Debugging-Verfahren.

Im folgenden Abschnitt sollen die oben erwähnten Problembereiche anhand eines einfachen FPGA-Koprozessors verdeutlicht werden.

#### 1.2 Problembereiche

#### 1.2.1 Struktur eines FPGA-Koprozessors

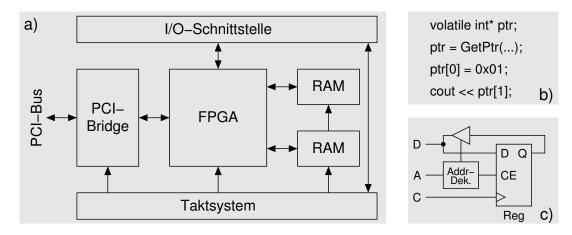

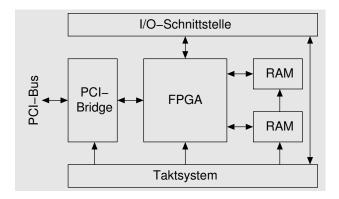

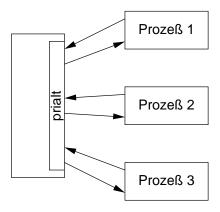

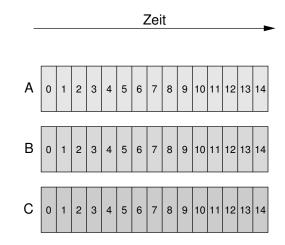

Abbildung 1.1 a zeigt die Grundstruktur eines PCI-basierten FPGA-Koprozessors. In der Regel sind solche Systeme in Form von Einsteckkarten für PCs realisiert. Sie enthalten einen oder mehrere FPGAs, in denen im Rahmen der vorhandenen Resourcen nahezu beliebige digitale Schaltungen implementiert werden können.

Abbildung 1.1: Komponenten eines FPGA-Koprozessors mit Übersicht (a), Software (b) und FPGA-Konfiguration (c)

#### 1.2.2 Enge Kopplung zwischen Hardware- und Softwarebereich

Auf dem Hostrechner, meist einem handelsüblichen PC, wird ein Programm ausgeführt, das entsprechend der gewünschten Anwendung den Datenaustausch mit der Koprozessorkarte durchführt. Dieser Datenaustausch wird über Pseudoregister ("special function registers") realisiert. Sie bilden die Schnittstelle zwischen der Software (Abb. 1.1 b) und der Hardwareimplementierung im FPGA (Abb. 1.1 c). Das Verhalten der Software ist in hohem Maße abhängig von der Schaltung im FPGA. Umgekehrt wird das Verhalten des FPGAs vom Ablauf des Programmes gesteuert. Keine der beiden Komponenten kann in sinnvoller Weise ohne die andere arbeiten.

Obwohl beide Bereiche eine hohe Abhängigkeit aufweisen, müssen sie mit grundlegend verschiedenen Entwicklungssystemen und -sprachen implementiert werden:

• Host-Software ("Applikation").

Diese umfaßt das Konfigurieren des FPGAs, den Datentransfer und alle weiteren Aufgaben, die nur vom Mikroprozessorsystem sinnvoll bearbeitet werden können (Dateizugriff, grafische Benutzerschnittstelle usw.). Die Implementierung erfolgt in der Regel mittels C oder C++.

• FPGA-Konfiguration ("Design").

Hier wird die im FPGA zu realisierende digitale Schaltung festgelegt. Zur Hardwarebeschreibung stehen *VHDL* bzw. C-ähnliche Sprachen der neueren Entwicklungssysteme zur Verfügung.

Der Entwickler muß beide Sprachen und die jeweils dazugehörigen Entwicklungsumgebungen beherrschen, um Anwendungen für FPGA-Koprozessoren erstellen zu können.

#### 1.2.3 Beherrschung von Umfang und Komplexität

Moderne FPGAs mit ihren enorm gestiegenen Resourcen (mehrere zehntausend Flip-Flop-Funktionen pro Baustein) ermöglichen es, umfangreiche und komplexe Implementierungen auf FPGA-Koprozessoren zu realisieren. Um jedoch diesen Umfang und die Komplexität beherrschen zu können, muß der Anwender von der Entwicklungssoftware auf geeignete Weise unterstützt werden.

So ist zur Implementierung effizienter FPGA-Designs notwendig, daß er verschieden hohe Abstraktionsebenen einsetzen kann. Den Hardwarebeschreibungssprachen VHDL und Verilog [103] sowie den Systemen JHDL und PAM-Blox fehlen höhere Ebenen, mit denen

z.B. das Erstellen komplexer Zustandsmaschinen erleichtert werden kann. Bei hochsprachenorientierten Systemen wie *Handel-C* dagegen ist keine direkte Integration niedriger Ebenen möglich.

Im Bereich der herkömmlichen Softwareentwicklung sind die Probleme von Umfang, Komplexität und Abstraktionsebenen schon seit langer Zeit bekannt. Hier wurden wirksame Lösungsmethoden entwickelt, so etwa der Übergang von Assembler- zu Hochsprachen oder das Konzept der Objektorientierung mit Vererbung und überladenen Methoden. An zeitkritischen Stellen kann jederzeit auf die Assemblerebene zurückgegriffen werden. In modernen Kompilern kann dies innerhalb des C/C++-Codes in Form von Inline-Assembler erfolgen. Auch die Source-Level-Debugger unterstützen diese Integration.

Auf den Bereich der Hardwarebeschreibungssprachen wurden diese Methoden bisher jedoch nicht ausreichend übertragen.

#### 1.2.4 Realistische Simulation des Gesamtsystems

Nach der heute üblichen Vorgehensweise führt der Entwickler eine softwaremäßige Simulation der Hardwarebeschreibung durch, bevor er das Design auf der Zielhardware in Betrieb nimmt. Die Simulation bietet bessere Untersuchungsmöglichkeiten der einzelnen Signale und vermeidet darüberhinaus bei Fehlern Schäden an der Hardware.

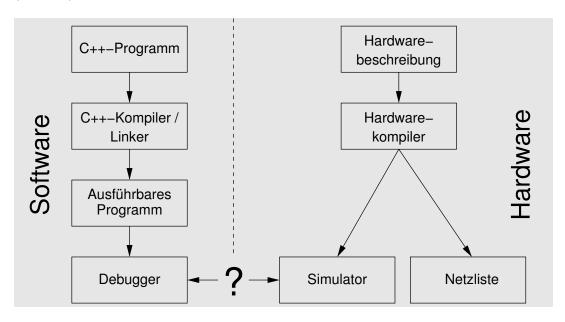

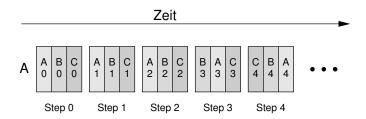

Aufgrund der engen Kopplung zwischen Mikroprozessor und FPGA ist eine realistische Simulation nur zusammen mit der Applikation möglich. Werden Applikation und FPGA-Design jedoch mit verschiedenen Entwicklungssystemen erstellt, führt dies in der Praxis oft zu Schwierigkeiten, weil sich die Systeme zur Simulation nur schwer verbinden lassen (Abb. 1.2).

Abbildung 1.2: Probleme bei der Simulation des Gesamtsystems

Die Applikation kann zwar mit einem handelsüblichen Debugger schrittweise ausgeführt und getestet werden, bei Zugriffen auf Pseudoregister ist jedoch ein Zusammenwirken mit dem Hardwaresimulator erforderlich. Ohne die Simulation des Verhaltens dieser Pseudoregister kann die Applikation nicht realistisch fortgesetzt werden.

Andererseits sind zur Simulation der Hardwarebeschreibung externe Stimuli erforderlich. Die existierenden *VHDL*-basierten Systeme ermöglichen die Erzeugung solcher Stimuli mittels *VHDL*-Testbenches oder Testvektoren. Die Möglichkeiten sind jedoch eingeschränkt, da *VHDL* eine Hardwarebeschreibungssprache, aber keine vollständige und effiziente Programmiersprache darstellt. Bereits das Simulieren großer Speicherbausteine, etwa

SDRAMs, bereitet in der Praxis aufgrund der erforderlichen Rechenzeit und des Speicherbedarfes der *VHDL*-Simulatoren Schwierigkeiten. Die Simulation einer vollständigen FPGA-Koprozessoranwendung einschließlich Softwarekomponente ist nahezu unmöglich.

Moderne VHDL-Simulatoren beinhalten eine spezielle Schnittstelle, über die konventioneller Programmcode in Form von dynamischen Linkbibliotheken (DLLs) integriert werden kann. Diese Schnittstellen sind jedoch in der Praxis unhandlich und die Gesamtsimulation läuft nicht schnell genug ab, um komplexe Anwendungen in akzeptabler Zeit zu simulieren.

Das *SystemC*-Konzept erlaubt die Erstellung kompletter Koprozessoranwendungen mit C++, wobei auch ein Schwerpunkt auf die Simulation von Gesamtsystemen gelegt wird. Simulation und Synthese der Hardwarebeschreibung werden jedoch unterschiedlich behandelt: Die Simulation erfolgt mittels C++-Klassenbibliothek, die Synthese mittels speziellen Kompilern. Daher kann nicht jede simulierbare Beschreibung auch synthetisiert werden. Darüberhinaus ist das konkrete Syntheseergebnis kompilerabhängig.

Simulation und Synthese müssen jedoch auf derselben Datenbasis beruhen, um eine realistische Simulation von Gesamtsystemen zu ermöglichen.

#### 1.2.5 Moderne Techniken zum Hardware-Debugging

Auch eine sorgfältig durchgeführte Simulation kann kein allgemein fehlerfreies Funktionieren eines FPGA-Designs garantieren. Dies gilt besonders im Zusammenhang mit Mikroprozessorsystemen, die aufgrund von Busarbitrierung und Multitasking-Betriebssystemen ein stark schwankendes und schwer vorhersehbares Zeitverhalten aufweisen. Hier kann eine Simulation immer nur eine beschränkte Anzahl von Ablaufkombinationen abdecken. Damit ist es zwar möglich, die Existenz eines Fehlers nachzuweisen, aber niemals die Fehlerfreiheit.

Tritt im Echtzeitbetrieb ein Fehler auf, der in der Simulation nicht reproduzierbar ist, wird ein Hardware-Debugging notwendig sein. Dazu stehen in der Praxis spezielle Geräte, wie etwa Logikanalyzer, zur Verfügung, mit denen das Verhalten des Systems überwacht und aufgezeichnet werden kann. Es ist jedoch auf diese Weise nicht ohne weiteres möglich, interne Signale des FPGA-Designs zu beobachten, was für die Fehlersuche von erheblicher Bedeutung ist.

Das Readback-Verfahren der FPGAs ermöglicht es, zu jedem beliebigen Zeitpunkt während des normalen Betriebes den Zustand aller internen Flip-Flops, Speicherblöcke und weiterer Signale auszulesen.

Durch partielle Rekonfiguration können am konfigurierten FPGA Änderungen vorgenommen werden. So sind die Zustände der Flip-Flops, Funktionsgeneratoren und Block-RAMs modifizierbar.

Diese beiden Verfahren erfordern jedoch eine Unterstützung durch das zur Hardwarebeschreibung verwendete Entwicklungssystem. Das größte Problem besteht darin, daß bei den herkömmlichen Systemen die Namen der Elemente in der Hardwarebeschreibung nicht unverändert in die Netzliste übernommen werden. Es ist daher schwierig, ein Symbol der Netzliste einem Bauteil der ursprünglichen Hardwarebeschreibung zuzuordnen. Ohne diese Zuordnung können jedoch Readback und partielle Rekonfiguration nicht automatisiert eingesetzt werden.

#### 1.3 Zusammenfassung

Moderne FPGA-Koprozessoren stellen besondere Anforderungen an die Entwicklungssysteme bezüglich:

- Enger Kopplung zwischen Hardwarebereich (FPGA) und Softwarebereich (Mikroprozessor).

- Beherrschung von Umfang und Komplexität.

- Realistischer Simulation des Gesamtsystems.

- Moderner Techniken zum Hardware-Debugging.

Die konventionellen *VHDL*-basierten Systeme sind hierbei im wesentlichen durch die Eigenschaften der Sprache *VHDL* beschränkt. Diese ermöglicht keine höheren Abstraktionsebenen und keine vollständige Simulation von Koprozessoranwendungen. Bei einer Implementierung von Testbenches mittels *VHDL* sind zudem zwei Entwicklungssprachen notwendig. Weiterhin übernehmen *VHDL*-Kompiler Bauteilnamen nicht unverändert in die Netzliste, wodurch kein automatisierter Einsatz von Readback und partieller Rekonfiguration möglich ist.

Neuere C/C++-basierte Entwicklungssysteme überwinden die Sprachbarriere zwischen Hardware- und Softwarebereich. Jedoch werden Beherrschung von Umfang und Komplexität und Simulation komplexer externer Bausteine nicht ausreichend unterstützt. Darüberhinaus ist eine gleichzeitige Anwendung verschiedener Abstraktionsebenen sowie die Anwendung der Readback-Funktion bei diesen Systemen nicht vorgesehen.

*SystemC* hat zwar explizit die Simulationsmöglichkeit von Gesamtsystemen zum Ziel. Dieses Entwicklungssystem zeigt jedoch durch die unterschiedliche Behandlung von Simulation und Synthese Schwächen bei der Übereinstimmung dieser beiden Bereiche.

Das hochsprachenorientierte *Handel-C* stellt keine direkte Integration struktureller Ebenen zur Verfügung und besitzt keine ausreichende Unterstützung für die Simulation von FPGA-Koprozessoren. Wie auch bei *SystemC* ist keine automatisierte Anwendung von Readback und partieller Rekonfiguration möglich.

Zusammenfassend läßt sich feststellen, daß keines der bisher existierenden Systeme die Anforderungen erfüllt, die moderne FPGA-Koprozessoren an die Entwicklungssoftware stellen.

## Kapitel 2

# CHDL: Ein C++-basiertes Entwicklungssystem für FPGA-Koprozessoren

#### 2.1 Einführung

Aufgrund der im vorigen Kapitel aufgezeigten Probleme herkömmlicher Systeme wurde im Rahmen dieser Arbeit ein homogenes C++-basiertes Entwicklungssystem implementiert, *CHDL* (C++-based Hardware Description Language). Es setzt die konventionelle Programmiersprache C++ sowohl zur Hardwarebeschreibung als auch zur Simulation ein.

Ein Vorteil von *CHDL* besteht darin, daß zum Übersetzen der strukturellen Hardwarebeschreibung kein spezieller proprietärer Kompiler benötigt wird. *CHDL* beruht auf dem Prinzip einer C++-Klassenbibliothek, daher genügt ein handelsüblicher C++-Kompiler, um die Beschreibung zu übersetzen. Das resultierende Programm führt dann sowohl die Simulation als auch die Synthese durch.

CHDL kann prinzipiell alle verfügbaren FPGAs unterstützen. Implementiert sind zur Zeit alle FPGAs der Firma XILINX von XC4000 bis Virtex-II Pro. Aufgrund des kompatiblen Netzlistenformates kann CHDL auch zur Entwicklung von Designs für XILINX-XC9500 PLDs sowie FPGAs der Reihe AT40K von Atmel verwendet werden.

Die folgenden Abschnitte vermitteln einen kurzen Einblick in die Fähigkeiten des *CHDL*-Systems. Die Darstellung orientiert sich dabei an der üblichen Vorgehensweise beim Hardware-Design:

- Hardwarebeschreibung.

- Simulation.

- Synthese.

- Hardware-Debugging.

#### 2.2 Hardwarebeschreibung

Zur Hardwarebeschreibung auf der untersten Ebene werden speziell definierte C++-Klassen und überladene Operatoren verwendet. Damit läßt sich eine strukturelle Beschreibung realisieren, die in ihrem Aussehen den klassischen strukturellen Hardwarebeschreibungssprachen wie etwa *ABEL* [117] stark ähnelt:

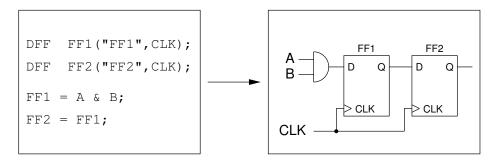

```

PadIn A("A");

PadIn CLK("CLK");

PadOut O("O");

DFF FF1("FF1",CLK);

FF1 = (!FF1 & A) | (FF1 & !A);

O = FF1;

```

Innerhalb der Hardwarebeschreibung können alle Mechanismen, die die Programmiersprache C++ zur Verfügung stellt, verwendet werden. So sind etwa bedingte Anweisungen, Parametrisierungen, Vererbung und virtuelle Methoden einsetzbar. Diese Kombinationsmöglichkeit stellt eine mächtige Methode dar, mit der sich selbst umfangreiche und komplexe FPGA-Designs erstellen und beherrschen lassen.

*CHDL* erlaubt weiterhin Beschreibungen auf höheren Abstraktionsebenen, um z.B. Zustandsmaschinen durch textuelle Beschreibung von Flußdiagrammen zu implementieren:

```

BeginState();

A = 0;

EndState();

LABEL("Start");

BeginState();

A++;

EndState();

IF (A < 10, "Start");</pre>

```

Dieses Verfahren wird in Kapitel 9 detailliert beschrieben.

Eine noch höhere Ebene bietet die Hochsprachenbeschreibung, die in Teil IV erläutert wird:

```

A = 0; S = 0;

while (A < 10)

{

S = S + A;

A = A + 1;

}</pre>

```

Ein wichtiges Merkmal des *CHDL*-Systems liegt darin, daß alle diese verschiedenen Ebenen gleichberechigt nebeneinander in einer homogenen Entwicklungsumgebung eingesetzt werden können.

Der Entwickler kann bei der Arbeit mit *CHDL* alle für C++ verfügbaren Entwicklungswerkzeuge verwenden, so etwa auch Debugger, spezielle Quelltexteditoren oder Klassenbrowser.

#### 2.3 Simulation

*CHDL* unterstützt ohne Einschränkungen die funktionale Simulation der Hardwarebeschreibung sowie der kompletten FPGA-Umgebung.

Das funktionale Verfahren ermöglicht durch den geringeren Rechenaufwand eine umfangreichere Simulation des Gesamtsystems als ein zeitbasiertes. Eine solche ist bei der Arbeit mit FPGA-Koprozessoren von größerer Bedeutung als eine zeitgenaue, jedoch rechenintensive Simulation eines Teilsystems. Zudem sind genaue Informationen über das zeitliche Verhalten eines FPGA-Designs erst nach Abschluß des Place&Route-Prozesses verfügbar. Zur Bestimmung der maximalen Taktfrequenz muß in jedem Fall der Timing-Analyzer von XILINX verwendet werden, da nur dieser alle internen Charakteristika der FPGAs berücksichtigt. Aus diesen Gründen wurde bei *CHDL* auf eine exakte zeitbasierte Simulation bewußt verzichtet.

Der Anwender kann beliebige externe Hardwarekomponenten in die Simulation einbeziehen. Das Verhalten dieser Komponenten wird dabei durch eine entsprechende C++-Funktion modelliert. Da *CHDL* als Klassenbibliothek konzipiert ist, können die Simulationsmodelle direkt ohne den Umweg über schwierig zu handhabende DLL-Schnittstellen integriert werden.

Auch interne Komponenten eines FPGA-Designs, die noch nicht im Detail implementiert wurden, können zunächst als angenäherte Simulationsmodelle einbezogen werden. Weiterhin ist zur Beschleunigung eine hierarchische Simulation möglich. Hierbei werden bereits erfolgreich getestete Module durch ihr Simulationsmodell ersetzt. Auf diese Weise lassen sich die Simulationszeiten erheblich verkürzen.

Durch eine spezielle Verbindung zwischen Hostsoftware und Hardwaresimulator können Zugriffe auf Pseudoregister realistisch simuliert werden. Die Hostsoftware läuft dabei in Echtzeit auf dem Prozessor und gegebenenfalls unter der Kontrolle eines konventionellen C++-Debuggers ab.

#### 2.4 Synthese

CHDL unterstützt die direkte Ausgabe von Netzlisten im XNF- oder EDIF-Format. Die erzeugten Netzlisten können ohne weitere Bearbeitung direkt an die Place&Route-Software übergeben werden. Außer dieser ist keine weitere Synthesesoftware erforderlich, insbesondere keine VHDL-Kompiler.

Alle in der *CHDL*-Hardwarebeschreibung enthaltene Vorplazierungs- und Timinginformationen werden automatisch in die Netzliste integriert.

Die Synthese erfolgt wie die Simulation durch Ausführen der kompilierten Hardwarebeschreibung. Simulation und Synthese verwenden dieselbe Datenbasis, so daß eine nahezu vollständige Übereinstimmung erreicht wird.

#### 2.5 Hardware-Debugging

*CHDL* unterstützt die Debugging-Verfahren, die von modernen FPGAs zur Verfügung gestellt werden.

Ermöglicht wird dies durch eine eindeutige und vorhersehbare Zuordnung der Bauteilnamen in der Netzliste. Mittels Readback können zu jedem beliebigen Zeitpunkt die aktuellen Zustände von Flip-Flops und RAMs ausgelesen werden.

Die partielle Rekonfiguration erlaubt weiterhin die schnelle Modifizierung dieser Zustände ohne erneuten Place&Route-Durchlauf. Damit lassen sich mächtige Verfahren zum Hardware-Debugging, wie etwa integrierte Logikanalyzer mit veränderbaren Triggerbedingungen, implementieren.

Durch die eindeutigen Netzlistennamen ergeben sich auch automatisierte Anwendungen zur nachträglichen schnellen Modifizierung von bereits gerouteten FPGA-Designs. Dies kann über eine Fernsteuerung des "fpga\_editor"-Programmes mittels Batchdateien erfolgen.

#### 2.6 Zusammenfassung

Es wurde ein erster Eindruck vermittelt, wie *CHDL* die Probleme moderner FPGA-Koprozessoren unterstützen kann. *CHDL* weist gegenüber anderen Entwicklungssystemen insbesondere folgende Vorteile auf:

- Die Kenntnis einer einzigen Programmiersprache (C++) ist ausreichend, um sowohl den Hardware- als auch den Softwarebereich eines FPGA-Koprozessors implementieren zu können.

- CHDL beruht vollständig auf handelsüblichem C++ ohne jegliche Modifikationen und ist als Klassenbibliothek realisiert. Jeder Softwareentwickler, der über Kenntnisse der wichtigsten Prinzipien der objektorientierten Programmierung und der digitalen Schaltungstechnik verfügt, ist damit in der Lage, Algorithmen auf FPGAs zu implementieren. Er kann dabei seine ihm vertraute C++-Entwicklungsumgebung, z.B. Microsoft Visual Studio, benutzen. Die Methoden, mit denen CHDL-Implementierungen erstellt werden, entsprechen denen der herkömmlichen Softwareentwicklung.

- Beim Erstellen komplexer und umfangreicher Implementierungen können die Vorteile der objektorientierten C++-Programmierung genutzt werden.

- Durch die Einbindung benutzerdefinierter Simulationsmodelle und der Simulation von Pseudoregistern werden FPGA-Koprozessoren optimal unterstützt.

- Außer einem handelsüblichen C++-Kompiler sowie der Place&Route-Software des FPGA-Herstellers sind keine weiteren Entwicklungswerkzeuge notwendig.

- Die Methoden, die moderne FPGAs zum Hardware-Debugging bereitstellen, werden vollständig unterstützt.

# Teil II Grundlagen und Stand der Technik

## Kapitel 3

# Digitale Schaltungstechnik

#### 3.1 Einführung

Die digitale Schaltungstechnik bildet die Grundlage für die Realisierung von Schaltungen in FPGAs.

Die wichtigsten Grundelemente sind zunächst die elektronischen Verknüpfungselemente (Gatter), die einfache Schaltfunktionen ausführen. Aus diesen können Schaltnetze und Speicherelemente konstruiert werden, welche wiederum die Basis für Zustandsmaschinen darstellen

Schaltnetze, Speicherelemente und Zustandsmaschinen bilden die Grundbausteine bei der Implementierung von Algorithmen in Hardware.

Diese Grundbausteine besitzen zeitliche Eigenschaften, die die maximal erreichbare Taktfrequenz der Hardwareimplementierung festlegen. Mit Hilfe verschiedener Optimierungsverfahren läßt sich die Taktfrequenz erhöhen.

#### 3.2 Verknüpfungselemente

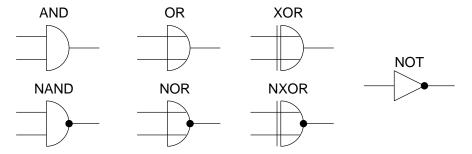

Elektronische Verknüpfungselemente, auch Gatter genannt, sind Schaltungen mit einem oder mehreren Eingängen sowie einem Ausgang, die einfache Schaltfunktionen ausführen. Eingänge und Ausgänge lassen sich durch binäre Schaltvariablen darstellen, die die Werte "0" bzw. "1" annehmen können. Eine Schaltfunktion ist eine eindeutige Zuordnungsvorschrift, die jeder Wertekombination ihrer Schaltvariablen den Ergebniswert "0" oder "1" zuordnet [49, 74, 11, 26].

Es gibt drei Grundverknüpfungen: "UND", "ODER" und "NICHT". Obwohl sich jede beliebige Schaltfunktion bereits mit diesen Grundverknüpfungen realisieren ließe, gibt es in der Praxis noch weitere, abgeleitete Verknüpfungen, mit denen Schaltfunktionen gelegentlich kompakter ausgedrückt werden können, z.B. "UND NICHT", "ODER NICHT" und "EXKLUSIV-ODER".

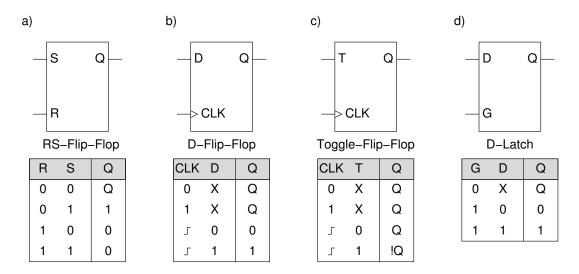

Die Abbildungen 3.1 und 3.2 zeigen einige Verknüpfungselemente mit ihrer grafischen Darstellung, wie sie im wissenschaftlichen Bereich verbreitet ist, und ihre Ergebniswerte im Überblick.

Abbildung 3.1: Darstellung einiger Verknüpfungselemente

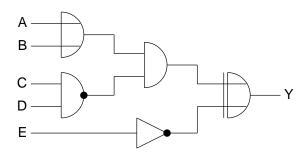

#### 3.3 Schaltnetze

Verknüpfungselemente lassen sich zu Schaltnetzen (Abb. 3.3) zusammenstellen, um beliebig komplexe Schaltfunktionen zu realisieren. In den folgenden Ausführungen werden als Schaltnetze nur solche Anordnungen bezeichnet, die keine Zyklen aufweisen. Sind Zyklen vorhanden, handelt es sich nicht um Schaltnetze, sondern bei sinnvoller Struktur um Speicherelemente.

| Α | В | NOT A | NOT B | A AND B | A OR B | A XOR B | A NAND B | A NOR B | A NXOR B |

|---|---|-------|-------|---------|--------|---------|----------|---------|----------|

| 0 | 0 | 1     | 1     | 0       | 0      | 0       | 1        | 1       | 1        |

| 0 | 1 | 1     | 0     | 0       | 1      | 1       | 1        | 0       | 0        |

| 1 | 0 | 0     | 1     | 0       | 1      | 1       | 1        | 0       | 0        |

| 1 | 1 | 0     | 0     | 1       | 1      | 0       | 0        | 0       | 1        |

Abbildung 3.2: Ergebnisse einiger Schaltfunktionen

Abbildung 3.3: Ein Schaltnetz

Es stehen verschiedene Methoden zur Verfügung, um Schaltnetze in geeigneter Form zu beschreiben:

#### • Grafische Darstellung.

Die grafische Darstellung eines Schaltnetzes in Form eines Schaltplanes (Abb. 3.3) ist für einfache Anordnungen zweckmäßig. Mit zunehmender Komplexität wird sie jedoch schnell unübersichtlich.

#### Wertetabellen.

Wertetabellen (Abb. 3.2) enthalten alle kombinatorisch möglichen Eingangszustände und den jeweiligen Ergebniswert. Sie können für Schaltnetze mit wenigen Eingängen schnell erstellt werden und lassen sich leicht verifizieren. n Schaltvariablen ermöglichen insgesamt  $2^n$  verschiedene Kombinationen. Mit zunehmender Anzahl von Eingängen werden sie folglich sehr umfangreich. Zur kompakteren Darstellung können mehrere Zeilen mit gleichem Ergebniswert zusammengefaßt werden, wenn gemeinsame Eingänge innerhalb der Gruppierung unerheblich sind. Diese Eingänge werden dann durch ein "Don't-Care"-Symbol (X) gekennzeichnet [74].

#### Verhaltensbeschreibungen.

Dies sind verbale Formulierungen, mit denen das Verhalten eines Schaltnetzes in Abhängigkeit von seinen Schaltvariablen beschrieben wird. Die Formulierungen müssen eindeutig spezifiziert sein, um Mißverständnisse oder Mehrdeutigkeiten zu vermeiden. Verhaltensbeschreibungen von Schaltnetzen werden z.B. von der Hardwarebeschreibungssprache *VHDL* [104] unterstützt:

```

if (A = '1' or B = '1') then

Y <= '1';

else

Y <= '0';

end if;</pre>

```

oder:

```

Y \le '1' when A = '1' or B = '1' else '0';

```

Beide Formulierungen legen fest, daß das Schaltnetz den Ausgangswert "1" liefern soll, wenn eine der beiden Schaltvariablen den Wert "1" annimmt. Ansonsten soll der Ausgangswert den Zustand "0" besitzen.

• Formelmäßige Darstellung mit Schaltvariablen und Operatoren.

Schaltnetze können durch Formeln dargestellt werden, in denen die Schaltvariablen mit Operatoren verknüpft sind. Dabei lassen sich Klammerungen verwenden, um die Prioritäten bei der Auswertung festzulegen. Auf diese Weise wird auch die Beschreibung komplexer Schaltfunktionen auf übersichtliche und kompakte Weise möglich. Solche formelmäßigen Darstellungen werden z.B. bei der Hardwarebeschreibungssprache *ABEL* [117] verwendet. Das Zeichen "&" repräsentiert dabei eine "UND"-Verknüpfung, ein "#" eine "ODER"-Verknüpfung und ein "!" eine "NICHT"-Operation.

```

Y = ((A \# B) \& (C \# D)) \# !E

```

#### 3.4 Speicherelemente

Anordnungen von Verknüpfungselementen können Zyklen enthalten. Stellen diese eine negative Rückkopplung dar, so wird die entstehende Konstruktion bei einigen oder allen Eingangskombinationen keinen stabilen Zustand einnehmen können. Sie gerät ins Schwingen und ist in der Digitaltechnik nicht sinnvoll einsetzbar.

Eine positive Rückkopplung dagegen kann einen erwünschten Speichereffekt verursachen. Bei geeigneter Verschaltung befindet sich die Anordnung stets stabil in einem von mehreren Zuständen. Nur bestimmte Eingangskombinationen können einen Zustandswechsel herbeiführen. Damit ist das Verhalten nicht, wie bei Schaltnetzen, nur vom Zustand der Eingänge abhängig, sondern zusätzlich noch vom aktuellen inneren Zustand.

Es lassen sich verschiedene Typen von Speicherelementen bilden, die sich in ihrem Verhalten unterscheiden [49, 74, 26]:

• RS-Flip-Flop (Abb. 3.4 a).

Ein RS-Flip-Flop besitzt einen Reset- und einen Set-Eingang. Der Reset-Eingang versetzt das Flip-Flop in den Zustand "0", der Set-Eingang in den Zustand "1". Sind beide Eingänge inaktiv, bleibt der aktuelle Zustand erhalten.

• D-Flip-Flop (Abb. 3.4 b).

Ein D-Flip-Flop ändert seinen aktuellen Zustand nur bei einer steigenden Signalflanke des Takteinganges. Es wird dann der Wert übernommen, der zu diesem Zeitpunkt am Dateneingang anliegt.

• Toggle-Flip-Flop (Abb. 3.4 c).

Ein Toggle-Flip-Flop ändert wie das D-Flip-Flop seinen aktuellen Zustand nur bei einer steigenden Taktflanke. Hat zu diesem Zeitpunkt der T-Eingang den Wert "1", wechselt es in den anderen Zustand. Beim Wert "0" erfolgt kein Zustandswechsel.

• D-Latch (Abb. 3.4 d).

Ein D-Latch übernimmt den Wert am Dateneingang, solange der Gate-Eingang aktiv ist. Sobald der Gate-Eingang inaktiv wird, bleibt der aktuelle Zustand fixiert.

Abbildung 3.4: Verschiedene Typen von Speicherelementen

#### 3.5 Zustandsmaschinen

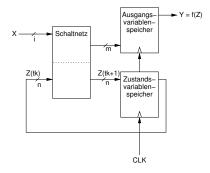

Zustandsmaschinen bestehen aus Schaltnetzen und Speicherelementen. Üblicherweise werden D-Flip-Flops als Speicherelemente verwendet. Die damit entstehende Anordnung besitzt den Vorteil, daß sie innerhalb ihrer zulässigen Taktfrequenz unabhängig von der Durchlaufverzögerung des Schaltnetzes arbeiten kann.

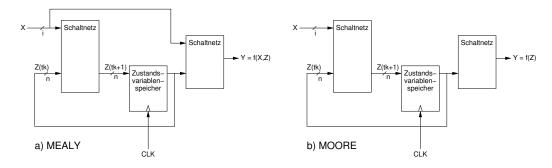

In Abhängigkeit von der konkreten Anordnung der Schaltnetze und Speicherelemente können zwei Grundmodelle von Zustandsmaschinen unterschieden werden [11]:

- Die *Mealy*-Maschine (Abb. 3.5 a).

Bei der *Mealy*-Maschine ändert sich der Ausgangsvektor *Y*, sobald sich ein Eingangssignal ändert. Es existiert ein direkter Logikpfad von *X* zu *Y* durch ein Schaltnetz.

- Die Moore-Maschine (Abb. 3.5 b).

Bei der *Moore*-Maschine ändert sich der Ausgangsvektor Y erst mit dem nächsten Takt nach Änderung eines Eingangssignals. Die Ausgänge werden hier ausschließlich durch eine Verknüpfung der Speicherelemente gebildet. Es existiert kein direkter Logikpfad von X nach Y.

Die *Moore*-Maschine besitzt in konkreten Anwendungen den Nachteil, daß sie mit dem Ausgangsvektor *Y* nicht sofort auf ein Ereignis an den Eingangssignalen reagieren kann.

Ein Vorteil dieser Maschine ist jedoch in der zeitlichen Entkopplung der Ausgänge von den Eingängen zu sehen. Bei einer Aneinanderreihung mehrerer Zustandsmaschinen läßt sich damit eine Aufsummierung der Verzögerungszeiten mit den vor- und nachgeschalteten Maschinen vermeiden.

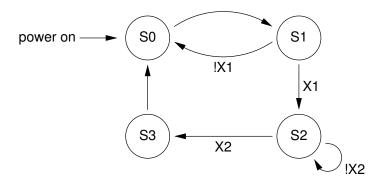

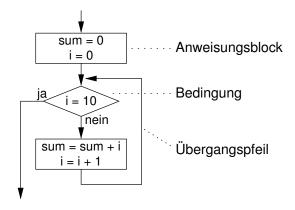

Das Verhalten von Zustandsmaschinen läßt sich durch Zustandsdiagramme (Abb. 3.6) beschreiben. Darin wird jeder Zustand durch einen Kreis repräsentiert. Ein Übergang von einem Zustand zu einem anderen wird durch einen Pfeil gekennzeichnet und muß eindeutig sein. Die Bezeichnung des Pfeils gibt dabei an, unter welchen Bedingungen der jeweilige Übergang stattfinden soll. Ein unbeschrifteter Pfeil kennzeichnet einen unbedingten Übergang. Führt für eine bestimmte Bedingung der Pfeil zum selben Zustand zurück, so muß er nicht eingezeichnet werden. Für jede Bedingung kann nur ein Pfeil zu einem anderen Zustand existieren. Es darf auch Zustände geben, die nie erreicht werden.

Zustandswechsel erfolgen nur bei steigenden Taktflanken. Kurzzeitige Änderungen der Eingangssignale zwischen den Taktflanken haben keine Auswirkungen auf die Zustände. Sie können bei *Mealy*-Maschinen jedoch eine entsprechende zeitweilige Änderung der Ausgangssignale bewirken.

Abbildung 3.5: Mealy- und Moore-Zustandsmaschine

Abbildung 3.6: Ein Zustandsdiagramm

# 3.6 Zeitverhalten von Schaltnetzen, Speicherelementen und Zustandsmaschinen

#### 3.6.1 Schaltnetze

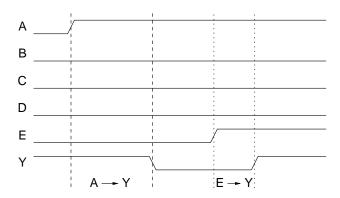

Änderungen an den Eingängen eines Schaltnetzes wirken sich nicht sofort auf die Ausgänge aus. Vielmehr erfolgt die Änderung erst nach einer zeitlichen Verzögerung. Diese Zeit wird Durchlaufverzögerung (*propagation delay*) genannt. Sie ist abhängig vom Signalpfad durch das Schaltnetz und insbesondere von der Anzahl an Einzelgattern, die sich in diesem Pfad befinden. Somit kann die Verzögerung für jeden Signalpfad unterschiedlich sein (Abb. 3.7, 3.3). Auch die Richtung des Zustandswechsels kann Einfluß auf das Zeitverhalten haben [49, 11].

Abbildung 3.7: Zeitverhalten in Schaltnetzen

#### 3.6.2 Speicherelemente

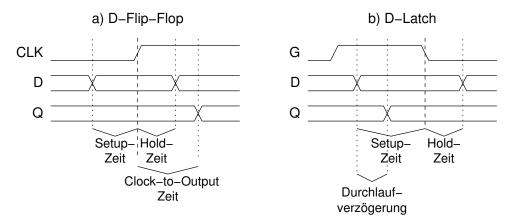

Bei den flankengesteuerten Flip-Flops sind folgende Zeiten von Bedeutung (Abb. 3.8 a):

• Clock-to-output-Zeit.

Der Ausgang eines Flip-Flops ändert sich nicht sofort bei einer positiven Taktflanke, sondern erst nach einer bestimmten Verzögerungszeit.

#### • Setup-Zeit.

Ein Eingangssignal wird von einem Flip-Flop nur dann bei der positiven Taktflanke zuverlässig übernommen, wenn es vorher für eine bestimmte Mindestzeit konstant angelegen hat.

#### • Hold-Zeit.

Das Eingangssignal muß auch nach der positiven Taktflanke noch eine bestimmte Zeit lang stabil bleiben, um zuverlässig übernommen zu werden.

Dagegen ist bei den D-Latches anstelle der Clock-to-output-Zeit die Durchlaufverzögerung zu berücksichtigen (Abb. 3.8 b).

Abbildung 3.8: Zeitverhalten eines D-Flip-Flops und eines D-Latches

#### 3.6.3 Zustandsmaschinen

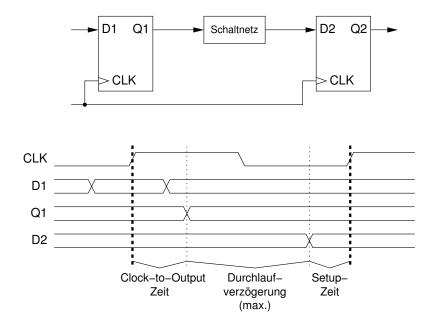

Für die maximale Betriebsfrequenz einer Zustandsmaschine sind folgende Zeiten von Bedeutung:

- Die Clock-to-output-Zeit der Speicherelemente.

- Die Verzögerungszeit durch das Schaltnetz.

- Die Setup-Zeit der Speicherelemente.

Diese drei Werte ergeben addiert die minimale Zeit, die zwischen zwei positiven Taktflanken vergehen muß (Abb. 3.9). Ist aufgrund einer zu hohen Taktfrequenz die Periodenlänge zu kurz, führt dies zu einer Verletzung der Setup-Zeit am empfangenden Flip-Flop. Dadurch wird der nächste Zustand nicht zuverlässig übernommen und die Schaltung arbeitet fehlerhaft.

Für die Bestimmung der maximalen Taktfrequenz einer Gesamtschaltung muß für jeden Signalpfad die oben beschriebene Zeitsumme ermittelt werden. Der Maximalwert aller Pfade legt dann die Mindestperiodenlänge des Taktes fest.

Abbildung 3.9: Zeitverhalten bei Zustandsmaschinen

#### 3.7 Optimierung des Zeitverhaltens von Zustandsmaschinen

#### 3.7.1 Verringerung der Logikstufen

Der Entwickler ist in der Regel bestrebt, eine möglichst hohe Taktfrequenz seiner Schaltung zu erreichen. Dazu muß er die Mindestperiodenlänge so gering wie möglich halten. Die Clock-to-output- sowie die Setup-Zeiten werden durch die eingesetzten Logikbausteine festgelegt und sind damit vorgegeben.

Die Verzögerungszeit durch das Schaltnetz wird durch die einzelnen Verzögerungszeiten der darin enthaltenen Elemente bestimmt. Diese addieren sich, wenn auf einem Signalpfad mehrere Elemente durchlaufen werden müssen.

Das in der Praxis gängigste Optimierungsverfahren besteht darin, die Schaltnetze so anzuordnen, daß möglichst wenig einzelne Logikstufen auf den Signalpfaden liegen. Bei vorgegebenen Hardwarekomponenten, so auch in FPGAs, stellt dies die einzige Einflußmöglichkeit dar, die der Entwickler auf die Durchlaufverzögerung hat.

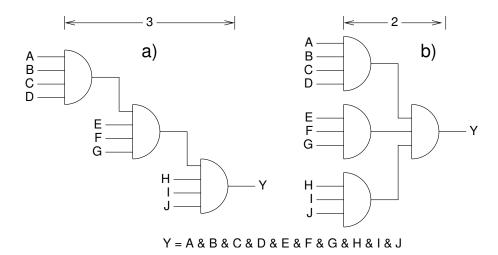

Abbildung 3.10 zeigt zwei verschiedene Anordnungen eines Schaltnetzes, in dem eine "UND"-Verknüpfung von 10 Signalen implementiert werden soll. Dem Entwickler stehen jedoch nur einzelne "UND"-Gatter mit maximal 4 Eingängen zur Verfügung.

Anordnung a) realisiert die Schaltfunktion mit 3 Einzelkomponenten. Der längste Signalpfad von den Eingängen A, B, C und D zum Ausgang durchläuft 3 Komponenten. Angenommen, jede Komponente verursacht eine Verzögerung von 5 ns, beträgt die Gesamtverzögerung 15 ns.

Anordnung b) realisiert die Schaltfunktion mit 4 Einzelkomponenten. Der Signalpfad von allen Eingängen zum Ausgang durchläuft hier jedoch nur 2 Komponenten. Die Gesamtverzögerung beträgt 10 ns. Diese Anordnung benötigt jedoch mehr Einzelkomponenten als die vorige.

Bei einer Clock-to-output-Zeit von 2 ns und einer Setup-Zeit von 3 ns liegt die Maximalfrequenz von Anordnung a) bei 50 MHz, von Anordnung b) jedoch bei 67 MHz.

#### 3.7.2 Sequentielle Bearbeitung von Operationen

Die Optimierung durch Verringerung der Logikstufen reicht insbesondere bei komplexen Schaltfunktionen oft nicht aus, um die gewünschte Taktfrequenz zu erreichen.

Es kann dann sinnvoll sein, die Schaltfunktion in mehrere Teilfunktionen zu zerlegen und in aufeinanderfolgenden Takten zu bearbeiten. Bei geeigneter Zerlegung weisen die einzelnen

Abbildung 3.10: Optimierung von Schaltnetzen nach Logikstufen

Teilfunktionen eine geringere Durchlaufverzögerung auf.

Damit kann die mögliche Taktfrequenz erhöht werden. Dabei ist jedoch zu beachten, daß durch die zusätzlich notwendigen Takte wiederum die Gesamtausführungszeit steigt.

Angenommen, eine Schaltfunktion besitzt eine Durchlaufverzögerung von 20 ns. Clockto-output- und Setup-Zeit betragen zusammen 5 ns. Damit liegt die maximale Taktfrequenz bei 40 MHz. Durch Zerlegung der Schaltfunktion in zwei Teile kann nun die Durchlaufverzögerung reduziert werden. Danach sind 2 Schritte für die Operation notwendig. Die Gesamtausführungszeit verkürzt sich nur, wenn durch die Zerlegung eine Taktfrequenz von mehr als 80 MHz erreicht werden kann. Dazu müsste sich die Durchlaufverzögerung jedoch auf weniger als 7.5 ns reduzieren lassen. In vielen Fällen ist der praktische Nutzen dieser Methode daher eingeschränkt.

Eine mehrtaktige Ausführung von Operationen kann jedoch auch aus anderen Gründen erforderlich sein:

- Ein sequentieller Eingangsdatenstrom zwingt die verarbeitende Logik, ebenfalls sequentiell vorzugehen.

- Resourcen, die nur in begrenzter Zahl vorhanden sind, müssen zur gemeinsamen Nutzung zeitlich aufgeteilt werden.

- Der auszuführende Algorithmus verlangt eine sequentielle Steuerung (z.B. Schleifen).

- Algorithmen können sich durch Mehrstufigkeit vereinfachen, da weniger kombinatorische Varianten notwendig sind.

- Beim Algorithmus ist der Umfang der Rechenoperation laufzeitabhängig (z.B. Prüfsummenberechnung von Datenpaketen unterschiedlicher Länge).

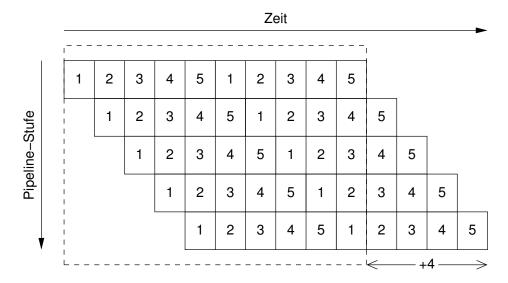

#### 3.7.3 Pipelining

Wie oben erörtert, ist die Zerlegung einer Schaltfunktion in mehrere sequentielle Operationen nur bedingt geeignet, um die Gesamtausführungszeit zu reduzieren.

In vielen Fällen ist es jedoch möglich, die Aufteilung der Logik so vorzunehmen, daß die entstehenden einzelnen Teilstufen unabhängig voneinander arbeiten. Dann kann der Entwickler durch Überlappung dieser Teilstufen durchaus eine Verkürzung der Gesamtausführungszeit erreichen. Diese Methode wird als Pipelining bezeichnet [11, 48].

Pipelining stellt ein bedeutendes Verfahren dar, die maximale Taktfrequenz einer Schaltung durch Aufteilung von Schaltfunktionen zu erhöhen, ohne daß dadurch die Anzahl der notwendigen Takte durch die Zerlegung wesentlich ansteigt.

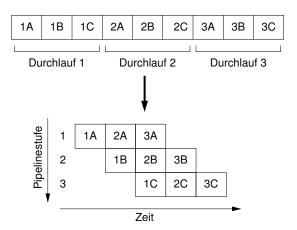

Angenommen, eine komplexe Schaltfunktion wird in 5 Teilstufen zerlegt, die nach dem Pipeline-Verfahren arbeiten können. Dann erhöht sich die Gesamtausführungszeit nicht auf das Fünffache, sondern nur um den absoluten Wert von 4 Takten. Diese sind notwendig, um am Ende die letzten 4 Ergebniswerte aus der Pipeline auszulesen (*pipeline flush*).

Abbildung 3.11: Pipeline-Verfahren

Voraussetzung für das Pipeline-Verfahren ist, daß sich die einzelnen Teilstufen unabhängig voneinander konstruieren lassen. Um dies zu erreichen, kann es notwendig sein, den auszuführenden Algorithmus deutlich umzustrukturieren.

#### 3.7.4 Zerlegung von Zustandsmaschinen

Die Komplexität der Schaltnetze, mit denen Zustandsmaschinen realisiert werden, ergibt sich aus den implementierten Zustandsübergängen sowie den in den Bedingungen verwendeten Signalen. Sind die Zustände durch viele Übergangsbedingungen miteinander vernetzt, können sich Schaltnetze mit hohen Durchlaufverzögerungen ergeben. Aber auch komplexe Berechnungen, die in den einzelnen Übergangsbedingungen ausgeführt werden müssen, können die Komplexität erhöhen.