# **Evaluation of an FPGA and PCI Bus based Readout Buffer for the Atlas Experiment**

Inauguraldissertation zur Erlangung des akademischen Grades eines Doktors der Naturwissenschaften der Universität Mannheim

vorgelegt von

Diplom-Physiker Matthias Müller aus Worms

Mannheim, 2004

Dekan:Prof. Dr. Jürgen Potthoff, Universität MannheimReferent:Prof. Dr. Reinhard Männer, Universität MannheimKorreferent:Prof. Dr. Peter Fischer, Universität Mannheim

Tag der mündlichen Prüfung: 14. Februar 2005

## Evaluation of an FPGA and PCI Bus based Readout Buffer for the Atlas Experiment

### Abstract

This dissertation evaluates a readout buffer system for the ATLAS detector trigger and data acquisition system. ATLAS is a high energy physics experiment at the large hadron collider (LHC) with the aim to reach new frontiers in the investigation of the structure of matter. The high precision ATLAS detector produces a huge amount of data, 40 TByte/s, which is reduced by a three-level trigger system for online event data selection.

The readout buffer system acts as a data buffer while the second trigger level computes the trigger decision. ATLAS uses a sequential selection in the level 2 trigger which means that all event data required for the trigger decision is requested from the readout buffer component subsequently. This increases the complexity of the readout buffer device and its output event rate. Furthermore a region-of-interest (RoI) concept limits the amount of data necessary for the processing of one event inside the level 2 processor by defining the detector region with interesting data. Thus, approximately 10 kHz output rate have to be provided while feeding  $\sim$ 1 kByte data packets with 100 kHz at the input.

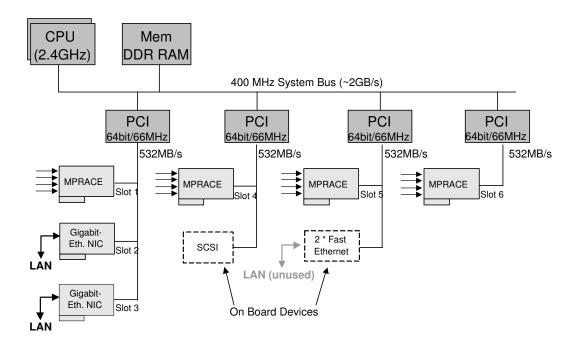

The evaluated implementation of this readout buffer should be based on commercial "ofthe-shelf" hardware. Thus a conventional Linux server PC with four PCI Bus segments has been used. This approach leads to uniformity in the ATLAS data acquisition system because all hardware beginning with the second trigger level is built of similar PCs. But a standard PC is not able to meet the previously mentioned requirements. Therefore it is extended (or accelerated) by a number of PCI based FPGA co-processor boards. Considering the above mentioned sequential selection and RoI concept, such a complex buffer component based on standard server PCs and FPGA co-processors has never been investigated before in high energy physics.

The FPGA co-processor is a simple component extending the PC for the time critical receiving and buffering of data. It is able to process data from four ATLAS detector links which allows the grouping of 12 to 16 links in one PC. Measurements show that this system is able to sustain the ATLAS requirements. Currently Linux OS, running on the PC system and handling the Gigabit Ethernet network I/O with the rest of the data acquisition system, is the main bottleneck. Improving this could be the subject of future investigations.

## Evaluierung eines FPGA und PCI Bus basierten Auslesespeichers für das Atlas Experiment

#### Zusammenfassung

Die vorliegende Arbeit evaluiert einen PCI Bus basierten Auslesespeicher für das Datenerfassungssystem des ATLAS Detektors. ATLAS ist ein Hochenergiephysikexperiment am Large Hadron Collider (LHC), mit dem Ziel neue Erkenntnisse über die Struktur der Materie zu gewinnen. Der hochempfindliche ATLAS Detektor produziert eine große Menge an Ereignisdaten, etwa 40 Tbyte/s, die von einem dreistufigen Triggersystem in Echtzeit analysiert werden müssen.

Die in dieser Arbeit vorgestellte Auslesespeicherkomponente speichert die Ereignisdaten während die zweite Triggerstufe über deren weitere Verwendung entscheidet. Dabei werden alle zur Triggerentscheidung erforderlichen Daten nach und nach vom Auslesespeicher angefordert. Dies erhöht sowohl die Komplexität des Auslesespeichers wie auch die Anforderungen an seine Ausgangsrate. Um die Menge der notwendigen Daten zu reduzieren wird die Detektorregion, in der sich interessante Ereignisse befinden, bereits vom Level 1 Trigger erkannt und an die zweite Triggerstufe weitergegeben. Dadurch reduziert sich die Ausgangsrate auf 10 kHz, während Datenpakete in der Größenordung von 1 kByte mit 100 kHz an die Komponente übertragen werden.

Ein wesentliches Ziel ist die Implementierung des Auslesespeichers mit kommerzieller, weit verbreiteter "standart" Hardware. Deshalb wurde ein konventioneller Linux PC mit vier PCI Bus Segmenten benutzt. Dies erhöht den Anteil an einheitlichen Hardware Komponenten im gesamten Triggersystem. Da ein solcher PC nicht in der Lage ist die hohen ATLAS Anforderungen an Eingangs und Ausgangsrate zu erfüllen, wurde er mit PCI Bus basierten FPGA Beschleunigerkarten erweitert. Unter Berücksichtigung der Komplexität der Komponente aufgrund der Verarbeitung von Level 2 Anfragen, ist dieser Ansatz für einen Auslesespeicher, bestehend aus Standart PC und FPGA Beschleuniger Hardware, einmalig in der Hochenergiepyhsik.

Die FPGA Beschleunigerkarte ist eine einfache Komponente, die den PC in zeitkritischen Aufgaben (Entgegennehmen und Speichern der Daten) unterstützt. Sie ist in der Lage, Daten von vier Detektorverbindungen gleichzeitig zu verarbeiten. Dies ermöglicht den Aufbau eines Auslesespeicher – PCs der 12 oder sogar 16 Detektorverbindungen verwalten kann. Messungen bestätigen, dass eine solche Komponente die ATLAS Anforderungen erfüllen kann. Der bandbreitenbegrenzende Faktor ist im Moment das Linux Betriebssystem. Dies hat unter anderem die Aufgabe die Gigabit Ethernet Verbindungen zu den Triggerprozessoren zu verwalten. Hier sind noch weitere Verbesserungen möglich.

# Contents

| Int | trodu | ction    |                                                     | 1  |  |  |  |  |

|-----|-------|----------|-----------------------------------------------------|----|--|--|--|--|

| 1   | Atla  | s Data A | Aquisition                                          | 5  |  |  |  |  |

|     | 1.1   |          | l Overview                                          | 5  |  |  |  |  |

|     | 1.2   |          | TLAS Detector                                       | 8  |  |  |  |  |

|     | 1.3   | The AT   | TLAS Data Acquisition Chain                         | 9  |  |  |  |  |

|     | 1.4   |          | FLAS Data Acquisition Event Format                  | 14 |  |  |  |  |

| 2   | The   | Atlas R  | eadout Subsystem Architecture                       | 17 |  |  |  |  |

|     | 2.1   | Requi    | rements for the ATLAS Readout Subsystem             | 17 |  |  |  |  |

|     | 2.2   | Readou   | ut Buffers in Other Experiments                     | 20 |  |  |  |  |

|     | 2.3   | ATLAS    | S Readout Subsystem Architecture                    | 23 |  |  |  |  |

|     |       | 2.3.1    | Architectural and Technology Choices                | 23 |  |  |  |  |

|     |       | 2.3.2    | Cost Modelling                                      | 25 |  |  |  |  |

|     |       | 2.3.3    | Previous Implementation Approaches                  | 27 |  |  |  |  |

|     |       | 2.3.4    | The ATLAS Baseline Architecture                     | 32 |  |  |  |  |

|     | 2.4   | Summa    | ary                                                 | 34 |  |  |  |  |

| 3   | ROF   | BIN Dev  | elopment with a Multi-Purpose PCI FPGA Co-Processor | 35 |  |  |  |  |

|     | 3.1   |          | PGA Co-Processor MPRACE                             | 36 |  |  |  |  |

|     | 3.2   |          |                                                     |    |  |  |  |  |

|     |       | 3.2.1    | Hardware Usage                                      | 39 |  |  |  |  |

|     |       | 3.2.2    | FPGA Firmware Overview                              | 40 |  |  |  |  |

|     |       | 3.2.3    | Event Buffer Management                             | 42 |  |  |  |  |

|     |       | 3.2.4    | SLink Input and Event Data Generator                | 43 |  |  |  |  |

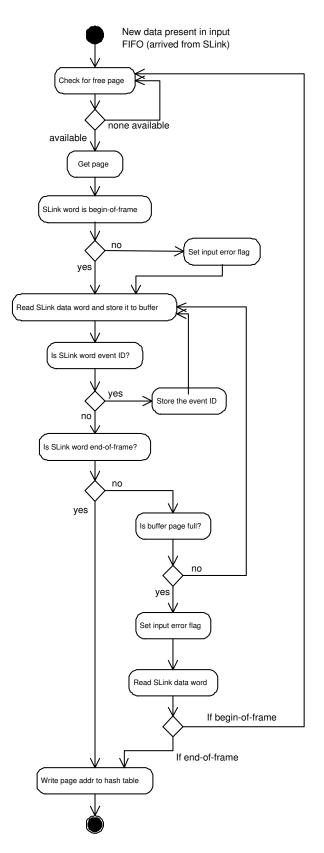

|     |       | 3.2.5    | Input Handler                                       | 44 |  |  |  |  |

|     |       | 3.2.6    | Message Decoder                                     | 45 |  |  |  |  |

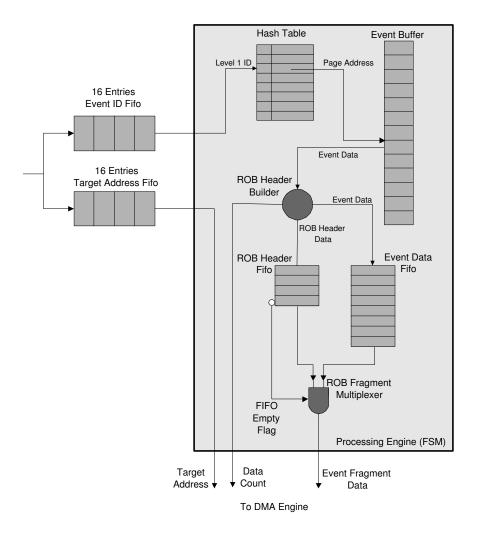

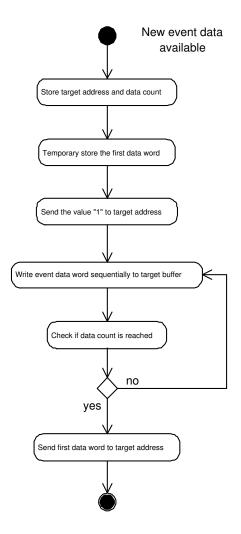

|     |       | 3.2.7    | Request Handler                                     | 48 |  |  |  |  |

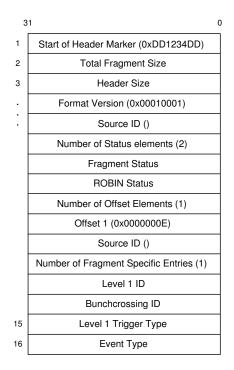

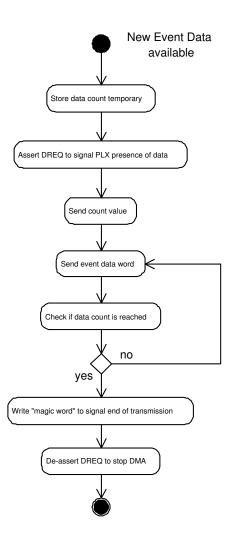

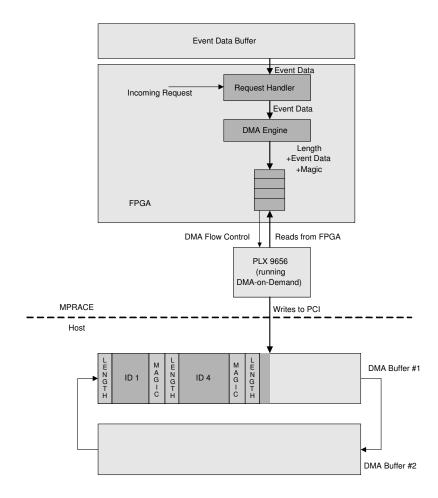

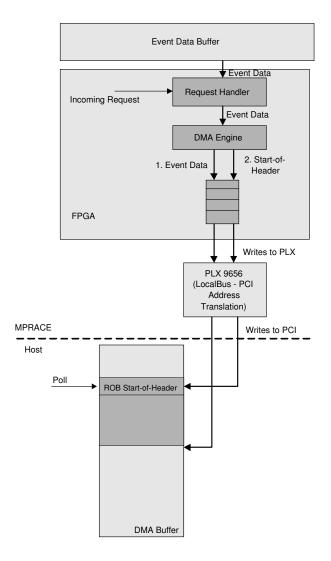

|     |       | 3.2.8    | DMA Engine                                          | 50 |  |  |  |  |

|     |       | 3.2.9    | Delete Handler                                      | 52 |  |  |  |  |

|     |       | 3.2.10   | RAM and DMA Arbiter                                 | 54 |  |  |  |  |

|     |       | 3.2.11   | The Controller Module                               | 54 |  |  |  |  |

|     | 3.3   | VHDL     | Design, Synthesis and Verification                  | 55 |  |  |  |  |

|     | 3.4   | Summa    | ary                                                 | 56 |  |  |  |  |

| 4 | ROI  | BIN Messaging and Readout System Software Design                | 57 |

|---|------|-----------------------------------------------------------------|----|

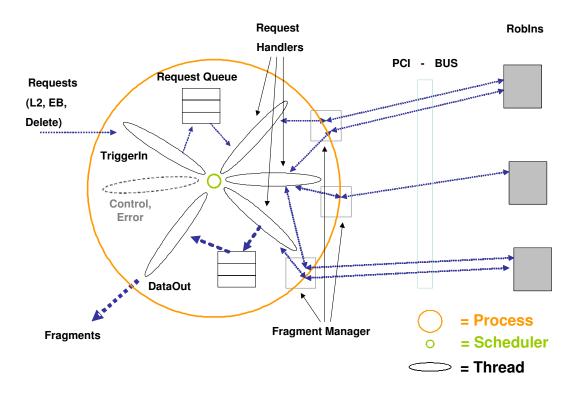

|   | 4.1  | ROS Host PC                                                     | 57 |

|   | 4.2  | ROS PC Software                                                 | 59 |

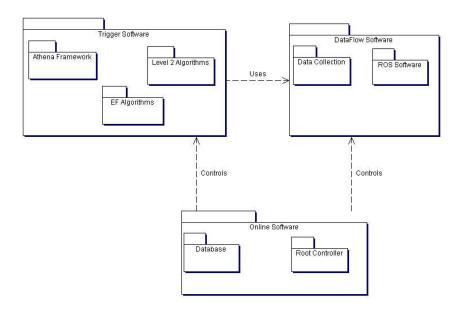

|   |      | 4.2.1 Atlas Software Overview                                   | 59 |

|   |      | 4.2.2 ROS Software Layer Model                                  | 60 |

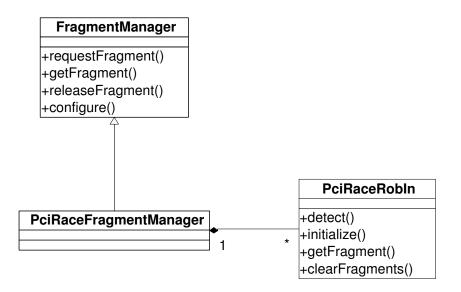

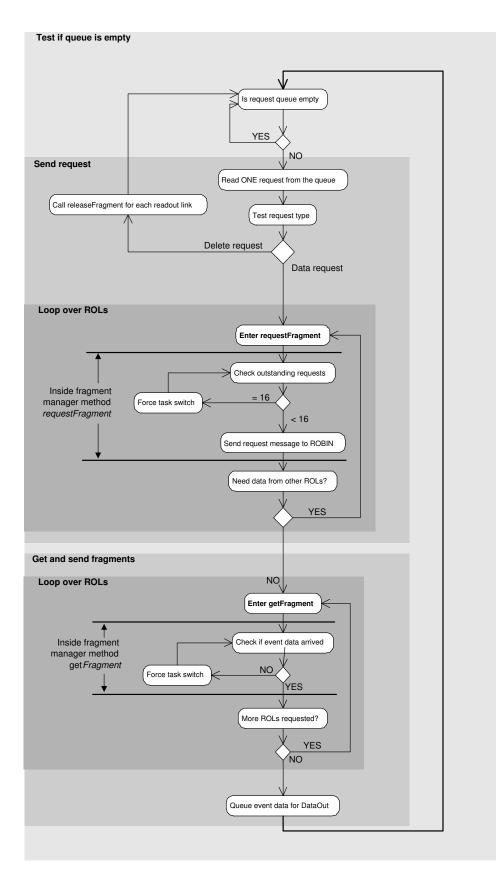

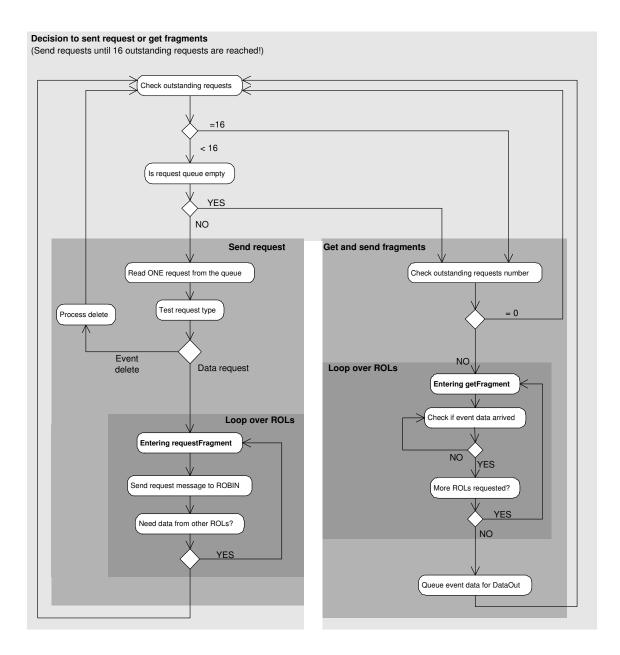

|   |      | 4.2.3 Main Application and Fragment Manager Interface           | 61 |

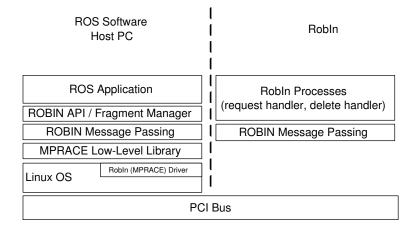

|   |      | 4.2.4 ROBIN Message Passing                                     | 66 |

|   |      | 4.2.5 Low-Level MPRACE Library and Device Driver                | 72 |

|   | 4.3  | Summary                                                         | 72 |

| 5 | Res  | ults and Analysis                                               | 75 |

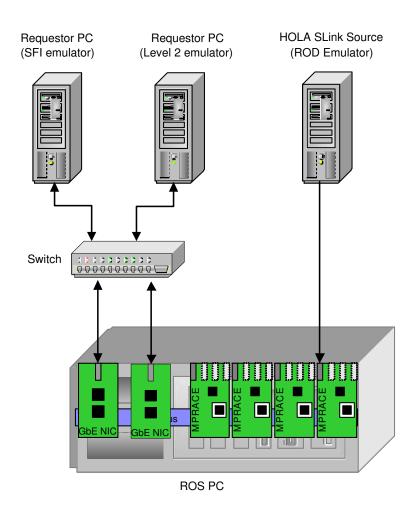

|   | 5.1  | The Test Setup                                                  | 75 |

|   | 5.2  | System Test Results                                             | 76 |

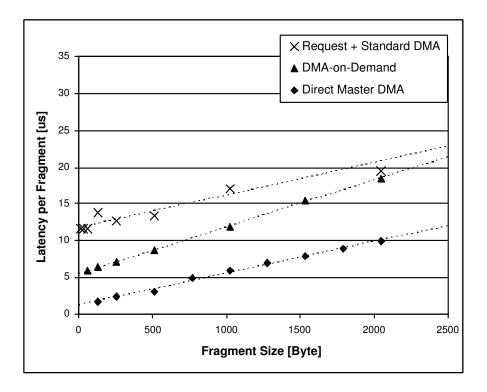

|   |      | 5.2.1 MPRACE Request Performance                                | 77 |

|   |      | 5.2.2 Influence of Delete Messages                              | 79 |

|   |      | 5.2.3 Influence of SLink Input                                  | 80 |

|   |      | 5.2.4 Multi-Threaded Versus Single-Threaded ROS Software Design | 81 |

|   |      | 5.2.5 Performance of a ROS PC with Multiple MPRACE ROBINs       | 84 |

|   |      | 5.2.6 Influence of Network I/O                                  | 87 |

|   | 5.3  | Conclusions                                                     | 89 |

| 6 | Con  | clusion and Outlook                                             | 91 |

|   | 6.1  | Summary                                                         | 91 |

|   | 6.2  | Discussion of the Current Design                                | 92 |

|   |      | 6.2.1 The MPRACE ROBIN                                          | 92 |

|   |      | 6.2.2 ROS PC and Software                                       | 94 |

|   | 6.3  | The Final ATLAS Readout System                                  | 95 |

|   | 6.4  | Future Experiments                                              | 96 |

| A | Glos | ssary                                                           | 99 |

# Introduction

In today's picture of the structure of matter physicists still have a large number of open questions. Currently the physics of the ingredients of the matter, their properties, and mutual interactions is described by the Standard Model [PRSZ95]. It classifies particles in two basic types of fermions<sup>1</sup>: leptons and quarks and their interactions: electromagnetic, weak, and strong. Each particle of matter up to the atoms can be assembled and its properties explained out of the concept of leptons and quarks and the physics described by the Standard Model. But some assumptions of the Standard Model are not yet experimentally proved.

The electroweak interaction, which unifies the electromagnetic and weak interaction, is mediated by four gauge bosons<sup>2</sup>: three massive ( $W^{\pm}$  and  $Z_0$ ) for the weak interaction and one massless (Photon) for the electromagnetic interaction [PRSZ95]. The appearance of massive together with massless gauge bosons could be explained by the existence of a Higgs particle with a mass of up to 800 GeV [Col99]. This postulation of the Standard Model has not been experimentally proved yet.

If the existence of the Higgs particle can not be proved, a theory beyond the Standard Model postulates new supersymmetric structures at energies above 1 TeV with a whole set of new particles [Col99].

Only the Tevatron accelerator at Fermilab, with its centre-of-mass energy of 1.96 TeV, can currently reach these energy regions. To extend the opportunities for physics experiments in these energy regions, the LHC (Large Hadron Collider) project has been raised at the European Particle Research Laboratory CERN. LHC is a proton-proton collider with an energy level of up to 14 TeV well suited to investigate the above mentioned physical questions. Its interaction cross-sections for various physics events is increased by one order of magnitude compared to the Tevatron accelerator. This raises the probability to observe new phenomena around 1 TeV [Ses00].

Additionally a more precise measurement of the b quark and the latest observed top quark can be done with LHC allowing to measure rare decay channels and the CP violation of the  $b\bar{b}$  decay (see [Ses00] for more details).

For a measurement of the proton-proton interaction a particle detector is needed. ATLAS [Col99] is one of four LHC detectors which will start in 2007. It has been designed to have sufficient physics performance to study the previously mentioned fundamental questions.

To achieve a reasonable precision a high effort is necessary. ATLAS consists of a number of sub-detectors to precisely record a high variation of particles created by the proton-proton

<sup>&</sup>lt;sup>1</sup>Fermions are particles with spin 1/2, 3/2, 5/2 or more.

<sup>&</sup>lt;sup>2</sup>Bosons are particles with spin 1, 2, 3 or more

scatter process and their tracks. Each event recorded by the detector generates approximately 1 MByte of data. Every 25 ns a new event appears in the LHC which leads to an event rate of 40 MHz, and a data volume of 40 TByte/s. Since this huge data volume can not be recorded, a pre-selection of physically reasonable and desirable events must be done within the detector's data acquisition system. This requires at least a partial analysis of the event which has to be done before the data is permanently recorded without disturbing further event detection. The detector's dead-time, the time in which no event data can be acquired, should not increase due to the online data analysis.

Thus staged hierarchical trigger systems are used for event pre-selection. Every stage receives event data with a lower rate and investigates it in more detail. Powerful algorithms have to be developed which analyse the event's physics and filter background or uninteresting events. A powerful computing architecture must be present together with facilities to move event data partly over long distances between the detector and the "counting rooms".

ATLAS uses three trigger levels to reduce the amount of data by a factor of 10<sup>5</sup> to a recordable event rate of 100 Hz [Col99]. Only the first of them processes events with custom hardware based on radiation-hard ASICs (Application-Specific Integrated Circuits) or FPGAs (Field-Programmable Gate Arrays). The other two trigger stages are based on large PC farms.

Due to the rapid increase of computing power and network technology in the past decade, more and more commercial products can be used even for time-critical tasks. This comprises computing nodes usable as trigger processors and network or data-bus technologies. Commercial "off-the-shelf" (COTS) components have a number of advantages compared with custom electronics components:

- Parts of the system can be exchanged against more powerful components without a redesign of electronics. This requires the compatibility of new components which is also a widespread issue in industrial applications.

- The manufacturers can give functional guarantees and support.

- The components are more cost effective then custom hardware.

- The components can be purchased in a short time. Thus recent hardware can be used at the experiment's start-up.

The ATLAS community has decided to use as many COTS components as possible within the trigger and data acquisition system [Gro03]. Nearly all components starting with the second trigger level are planned to be commercial products. Level 2 and level 3 trigger will use large PC farms. They are connected with Gigabit Ethernet [KH98] using commercial switches.

Another concept followed by the ATLAS trigger and data acquisition system is to keep the system as uniform as possible. The usage of similar PC technologies in the various subsystems reduces the administration effort and the amount of different software.

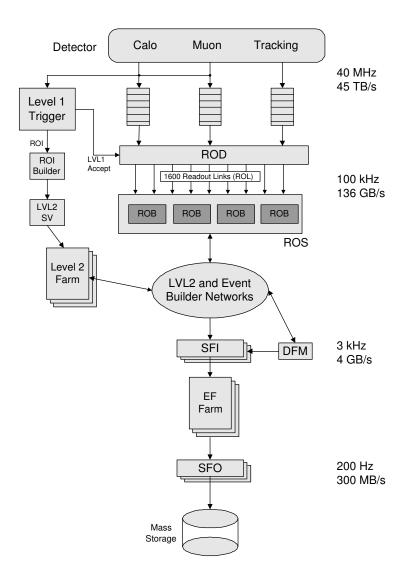

This thesis focuses on the boundary between the detector readout electronics and the commercial network to the second and third trigger level stage. The component present at this place, the readout subsystem (ROS), receives the detector data on 1600 point-to-point link connections with up to 100 kHz and forwards it to the trigger networks (Gigabit Ethernet) on demand.

Contrary to almost all other high energy physics experiments, the ATLAS level 2 trigger requests all event data required for the trigger decision from the ROS. Depending on the trigger

algorithm flow, event data from different sub-detectors is requested sequentially. Furthermore only data within a detector region, called region-of-interest and defined by the level 1 trigger, is asked. Both concepts reduce the network load at the input of the level 2 trigger, but complicates the ROS implementation and increases the event data output rate of this component. This makes the ROS architecture and implementation, evaluated within the thesis, a new and unique system in high energy physics.

Readout buffer components in the previous generation of high energy physics experiments have been less demanding. These components where based on the VME <sup>3</sup> bus in most cases combined with a large amount of custom hardware. Contrary, ATLAS follows the guideline to use as many standard, widespread commercial "of-the-shelf" components as possible. This thesis follows this idea and tries realising it within the ROS. The goal of this thesis is to implement a readout subsystem component with the following characteristics:

- Following the ATLAS community decision, the readout subsystem implementation should be based on commercially available PC hardware. Custom hardware development should be done as less and as simple as possible. Currently widespread PC systems provide 66 MHz / 64 Bit PCI buses which should be used for event data transport instead of the VME bus utilised by previous experiments.

- The readout buffer should concentrate many input links to one network output. This concept is suggested by the proportion between incoming data and the data required by the trigger farms. It helps to minimise the necessary amount of ROS hardware and level 2 and Event Building network switches and reduces the systems costs. But it puts also higher demands on each single component.

- The readout buffer should be the first instance of event building when a level 2 accept for an event occurs. It should perform partial event building on the data stored within all ROB's inside a crate and thus remove load from the ATLAS event building farm (SFI).

- The readout buffer should be tested in a realistic data-flow test environment.

The readout subsystem, presented in this thesis, uses a PC with multiple 66 MHz/64 Bit PCI buses similar to the components used within the trigger farms. This generates uniformity between the components of the ATLAS data acquisition system.

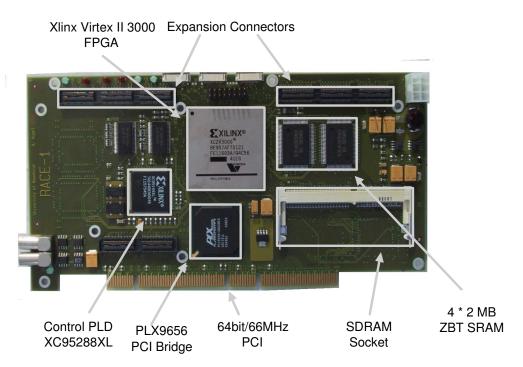

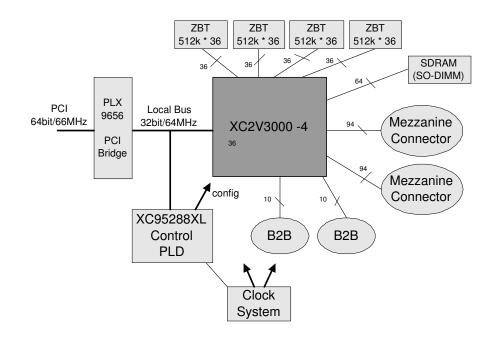

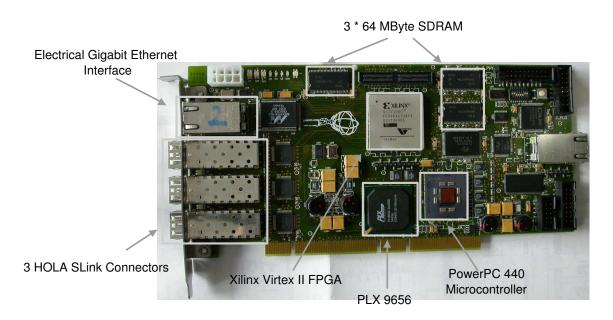

Only the hardware interface to the detector front-end via SLink is done by a custom electronics component. Its first prototype has been based on the MPRACE FPGA co-processor [MPR]. MPRACE has been developed as a multi-purpose PCI based FPGA hardware. It is used in various physics and computer science applications:

- Acceleration of astrophysical simulations [Lie04].

- Image processing [Hez04].

- Trigger algorithm acceleration for High Energy Physics Experiments [Bro04] [HAK<sup>+</sup>04].

The board is flexible and can be equipped easily with four connectors for ATLAS detector readout links. This is an important issue to achieve cost-effectiveness and reduce the number

<sup>&</sup>lt;sup>3</sup>Versa Module Europa

of PC components in the readout system. MPRACE is also a simple component comprising only an FPGA, memory, a PCI bridge, and the detector links.

The present thesis describes the development of a PCI bus based ATLAS readout buffer using the MPRACE FPGA co-processor. Test results show its usability. The thesis is divided as follows:

The first chapter introduces the ATLAS detector and its data acquisition system. It presents the ATLAS experiment and compares it to previous experiments. Furthermore this first chapter explains how detector data is acquired, processed, and recorded by the ATLAS trigger and data acquisition chain. The readout subsystem which is a central part of this chain gets also introduced here.

Chapter 2 focuses on the presentation of the ATLAS readout subsystem. It explains its task more detailed and shows the demands imposed by other ATLAS components. In the second part this chapter discusses various ROS implementation approaches and previous solutions.

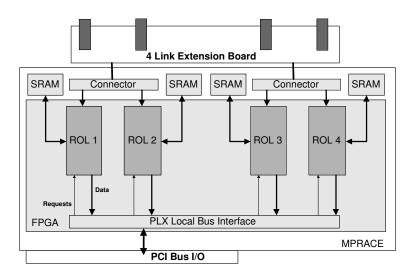

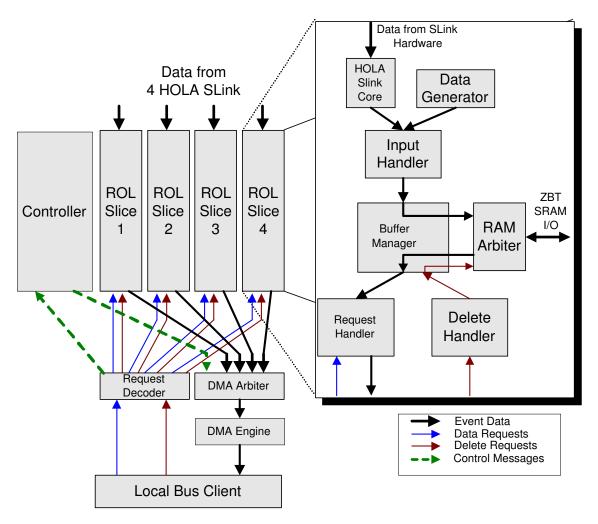

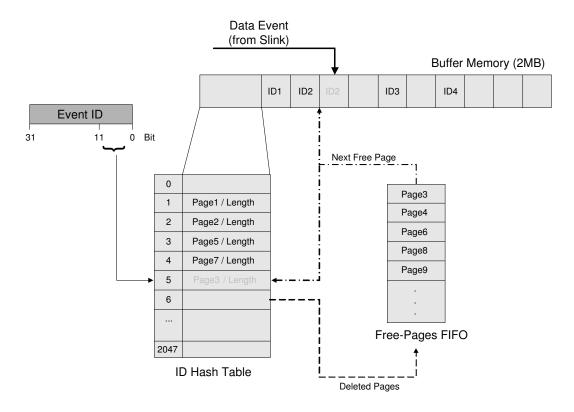

Chapter 3 describes the MPRACE hardware and the FPGA firmware developed for the ROS application. It shows how data is received on four readout links, buffered, and made available on demand.

The software application running on the multi PCI bus host PC is described in chapter 4. The software design has major influence to the system performance. Chapter 5 shows test and measurement results and discusses them.

Finally chapter 6 discusses the approach presented within this thesis, points out possible improvements, and gives an outlook to readout systems in future experiments.

## | Chapter

# Atlas Data Aquisition

The present chapter introduces the ATLAS experiment and the ATLAS data acquisition (DAQ) system. The ATLAS detector generates a huge amount of data which has to be pre-selected and recorded in real-time. This task is performed by the trigger and data acquisition system. It is constructed out of several processors, buffers, and data transportation elements. One of them is the readout subsystem (ROS). Its implementation is the main topic of the present thesis. The ROS position, task, and external boundaries in the ATLAS data acquisition system will be clarified here.

The first section of this chapter gives a general overview on the LHC accelerator and the ATLAS experiment. The second section introduces the ATLAS detector setup and the third section describes its data acquisition chain.

## **1.1 General Overview**

To reach new frontiers in particle physics, experiments at a very high energy level are necessary. New particles, postulated by physicists as a prove or extension of the Standard Model [PRSZ95], are expected to appear at energies around 1 TeV [Col99]. The probability of physical processes to be investigated is very low [Col99] wherefore the rate of events has to be very high to observe sufficient target processes in a reasonable time.

| Accelerator       | Institute | Centre-of-Mass | Crossing | Event Rate |

|-------------------|-----------|----------------|----------|------------|

|                   |           | Energy [GeV]   | [ns]     | [MHz]      |

| PEP II            | SLAC      | 10.58          | 4.2      | 238        |

| KEK B             | KEK       | 10.58          | 2        | 500        |

| HERA              | DESY      | 314            | 96       | 10.4       |

| Tevatron (Run II) | Fermilab  | 1960           | 132      | 7.6        |

| LHC               | CERN      | 14000          | 25       | 40         |

Table 1.1: Centre-of-mass energy and event rates for various recent and future colliders [FRB+00][Col95a] [Col02b] [Wol98].

These requirements characterise recent accelerator machines. Table 1.1 shows parameters of a selection of accelerators which are currently in use or under construction. The most challenging accelerator LHC (Large Hadron Collider), which will start operating at 2007, will reach a new order of magnitude in centre-of-mass energy. By colliding two proton beams accelerated to 7 TeV a centre-of-mass energy of 14 TeV can be reached. This is substantially more then the present most powerful accelerator Tevatron at Fermilab and will extend the ability to study the physics mentioned above and in the introduction. LHC also provides an increase of the event rate compared to the Tevatron accelerator which raises the probability to observe rare physical events. Other accelerators (e.g. PEP II, KEK B, or HERA) have much lower centre-of-mass energies and are used for other physics studies.

To record rare physical events at these colliders, highly precise detectors are necessary. Typically those consist of a number of different sub-detectors to ensure that a large variation of particles can be observed precisely. Each sub-detector delivers the data in a high number of readout channels which transport either analog or digital data. Together with the high event rate provided by the accelerator this results in a large amount of data for each recorded event.

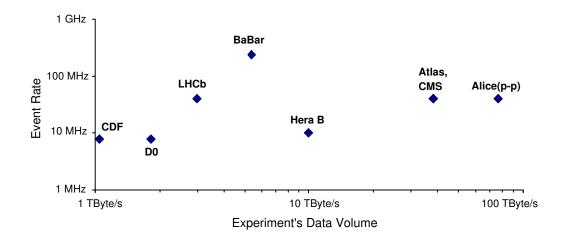

Figure 1.1 shows the event rate against the generated data volume for various experiments at the above mentioned accelerators. The two Tevatron experiments CDF and D0 deliver a comparatively small data volume at an event rate of 7.6 MHz. The BaBar experiment, running at the PEP II accelerator, is one of the most demanding currently running experiments in terms of data acquisition and event processing. It delivers 5.4 TByte/s with an event rate of 238 MHz.

Compared to these already operating experiments, the four new detectors at LHC (ATLAS, CMS, LHCb, and ALICE) will run at a rate of 40 MHz which is more than four times the rate of Tevatron. Excluding LHCb, the data volume generated by these experiments will be one order of magnitude higher. ATLAS and CMS will deliver nearly 40 TByte/s, ALICE even 80 TByte/s. This will substantially increase the demand on the experiment's data acquisition compared to today's experiments.

But the basic operation of the data acquisition of all mentioned experiments is similar. Since the data volume of none of them can be permanently written to storage media like harddisk arrays or tapes, a pre-selection of events has to be done. To pre-select or "trigger" on single events, the analysis of at least parts of the detector event data is required to separate these from background or irrelevant events. The latency for this process is a critical value for the efficiency of an experiment because no data can be taken meanwhile. Computing this trigger decision introduces an additional dead-time (a duration where no data can be acquired) into the data acquisition process [FRB+00].

To ensure that no physics process is lost during the trigger process, the dead-time has to be smaller than the rate of physical events to investigate. Its maximum allowable value has to be smaller than the event rate (25 ns in case of the LHC experiments). Thus trigger systems with a small execution time are required. Contrary high data reduction factors are needed to deal with the large event rates of modern accelerator machines. This requires a deep investigation of the event data with complex algorithms having long execution times.

To solve this contradiction, staged triggers are used which increase the data reduction factor, the complexity of the analysis algorithm, and the used fraction of event data with each stage [FRB $^+00$ ]. The overall performance of a data acquisition system is influenced by:

- The efficiency of the analysis algorithm

- The performance of the trigger hardware

- The data transport between the trigger stages

The last two items mainly depend on technology choices and their efficient use inside the DAQ chain whereas the first one depends on the choice of the trigger algorithm and its implementation.

Trigger algorithms can be classified into [FRB<sup>+</sup>00] [Con84]:

- · Fixed-flow triggers

- Variable-flow triggers

- Logical triggers

- Arithmetical triggers

Fixed-flow triggers need a fixed amount of time to compute an accept or reject decision. The processing time is independent of the event complexity. Most fixed-flow triggers are simple and fast algorithms used in the first trigger level. Contrary variable-flow triggers consume a variable amount of time which depends on the complexity of the event. This class of triggers contains counters, loops, and programs. Only a minimum and maximum execution time can be specified. Logical trigger are implemented with Boolean logic operations like AND and OR whereas arithmetical triggers use pulse height and counter values to calculate the trigger decision.

Variable-flow trigger processors can be distinguished into data-driven processors and programdriven processors [FRB<sup>+</sup>00]. Data-driven processors are pushed by the arriving of event data. The algorithm does not influence the quantity of data provided to the processor. The execution time does not depend on the event data. Contrary, in program-driven processors the program decides on the executed data. The execution time depends on the processed event data.

During the execution time of a trigger processor data must be stored in buffer elements. This requires memory which is large enough to keep all data arriving from the detector while the trigger decision is taking place. Furthermore, rejected events have to be sorted out within the buffer element. Buffer elements attached to fixed-flow triggers can be implemented with simple pipelines (see level 1 trigger in [Col96]) or circular buffers (see level 1 trigger in [Col95a]) which are long enough to keep the event data for the fixed processing time. On trigger reject, event data leaving the buffer is simply not forwarded to the next trigger level.

Variable-flow triggers require a more flexible buffer mechanism. Depending on the execution time of the algorithm, only a maximum storage time is known per event. The buffer, typically fast SRAM, Dual-Port RAM<sup>1</sup>, or similar (see e.g. [Col95a]), must be able to keep all events at least for this time. In case of an accept the event has to be localised inside the buffer and sent to the successive trigger level.

## **1.2 The ATLAS Detector**

ATLAS is one of the experiments currently built at the new LHC accelerator at CERN (see 1.1). It is a general purpose detector to discover new physics at the boundary of current knowledge such as the Higgs boson or supersymmetrical extensions to the Standard Model. An international collaboration of approximately 2000 physicists from 33 countries participate in building up the experiment.

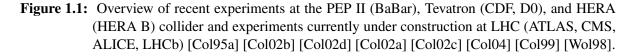

Figure 1.2: The Atlas Detector [Ses00].

To meet the physical goals the ATLAS detector has to recognize and track various particle signatures from electrons,  $\gamma$ , muons, jets, or missing energies [Sin00]. Therefore ATLAS comprises a number of sub-detectors which are placed in a number of layers around the proton beam interaction point. This is shown in Figure 1.2.

The area close to the interaction point, the innermost radius, is covered by the ATLAS inner detector which is divided again in three sub-detectors: Pixel, SCT, and TRT [Col99] [Ses00].

8.

<sup>&</sup>lt;sup>1</sup>Dual-Port RAM can be independently accessed for reading and writing.

It allows a precise recognition, track recording, and momentum measurement of particles. The whole inner detector is embedded in a solenoid magnet having a 2T central field. External to this solenoid are the electromagnetic calorimeter to identify and measure electrons and photons, and the hadronic calorimeters to identify and measure hadronic particles. The outermost parts of the detector contain the muon spectrometer for a precise muon track recording [Col99] [Ses00].

All these sub-detectors deliver the data about the recorded events in up to  $150 \cdot 10^6$  data channels resulting finally in approximately 1 MByte data for each event when permanently recorded. With an event rate of 40 MHz ATLAS generates a data volume of 40 TByte/s which has to be handled by the data acquisition chain.

## **1.3 The ATLAS Data Acquisition Chain**

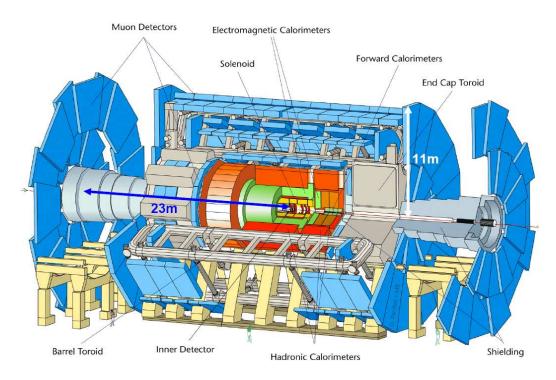

As already described in the previous chapter, the precision of the ATLAS sub-detectors results in a high data volume processed by the data acquisition with the experiment's interaction rate of 40 MHz. An overall data of 40 TByte/s is produced by ATLAS. To reduce this to a rate of 300 MB/s, which can be written to a permanent storage medium, an efficient trigger system is needed. This has to be flexible enough to adapted it to the various physics phenomena targeted by ATLAS.

Section 1.1 already introduced the concept of staged triggers in high energy physics to reduce the huge amount of data delivered by the experiment's detectors. ATLAS makes use of this concept too. Its DAQ system is implemented by three trigger levels, which reduce the event rate by a factor of  $10^5$ .

Figure 1.3 shows the ATLAS trigger and DAQ system. Beside the three trigger levels various other modules are integrated into the ATLAS DAQ. They are described in the following sub-sections.

## Level 1 Trigger

The level 1 trigger examines event data from the ATLAS calorimeter and muon sub-detector to form a trigger decision. The trigger algorithm analyses threshold information of energy and momentum to find signatures of possible particles. This level 1 arithmetic trigger (see 1.1) is implemented using synchronous, pipelined, parallel processors driven by the LHC 40 MHz clock. ASIC<sup>2</sup> and FPGA<sup>3</sup> technology is used for the processors which are partly placed very close to the detector to prevent signal synchronisation problems due to the wide spread area of ATLAS.

Computing the level 1 decision takes  $2 \mu s$ , every 25 ns a new calculation must be initiated [Gro98a]. During this decision process the event data of all sub-detector is stored inside fast pipeline memories. On accept, event data is passed by the readout drivers to the readout buffers. Both are described later in this chapter.

The rate of level 1 accepts can be estimated by simulating the physical processes in the LHC proton-proton interaction together with the behaviour of the level 1 trigger processors [Gro98b]. The result is a table which assigns various particle signatures an estimated rate. This table is called "Trigger Menu" and gives a detailed report on the expected level 1 accept

<sup>&</sup>lt;sup>2</sup>ASIC: Application-Specific Integrated Circuit

<sup>&</sup>lt;sup>3</sup>FPGA: Field Programmable Gate Array

Figure 1.3: The ATLAS trigger and event data acquisition. [Col99]

rate and how it distributes on the various physical events. Figure 1.4 shows the most recent trigger menu for the initial LHC luminosity<sup>4</sup> of  $2 \cdot 10^{33}$  cm<sup>-2</sup>s<sup>-1</sup> [VVT03].

According to this trigger menu a level 1 accept rate of 25 kHz is expected. Since this estimation does not contain any safety factor, a larger accept rate must be targeted within the trigger development. It has been decided to design the level 1 trigger and also all other instances of the DAQ chain for supporting an accept rate of 75 kHz. Furthermore an extension to 100 kHz is foreseen for a later experiment upgrade [Gro98a].

On accept, the level 1 trigger passes the detector area coordinates in which particles have been found to the next trigger level. This area, called region-of-interest (RoI), is defined as a pair of angles which describe a cone inside the ATLAS Detector with its top in the experiment's interaction point. It clearly shows the area where the next trigger stage (level 2) has to run the search algorithms. This substantially reduces the amount of data required by the level 2 trigger (see the level 2 trigger subsection within this section).

<sup>&</sup>lt;sup>4</sup>The luminosity is the number of particles per time and per area within an accelerator beam. [FRB<sup>+</sup>00]

| Selection                        | <b>2 10<sup>33</sup></b><br>cm <sup>-2</sup> s <sup>-1</sup> |

|----------------------------------|--------------------------------------------------------------|

| MU20                             | 0.8                                                          |

| 2MU6                             | 0.2                                                          |

| EM251                            | 12.0                                                         |

| 2EM15I                           | 4.0                                                          |

| <b>J</b> 200                     | 0.2                                                          |

| <b>3J</b> 90                     | 0.2                                                          |

| <b>4J</b> 65                     | 0.2                                                          |

| J60 + xE60                       | 0.4                                                          |

| TAU25 + xE30                     | 2.0                                                          |

| MU10 + EM15I                     | 0.1                                                          |

| Others (prescaled, calibration,) | 5.0                                                          |

| Total                            | ~ 25                                                         |

Figure 1.4: Level 1 trigger menu for the initial LHC luminosity of  $2 \cdot 10^{33}$  cm<sup>-2</sup>s<sup>-1</sup>. The notations of particle signatures are explained in [Col99]. The recent values have been obtained from [VVT03].

### **Readout Driver (ROD)**

In case of a level 1 accept decision the event data is passed over to the readout drivers (ROD). 1600 Readout drivers organised in a number of VME crates collect the event data from the detector's data channels. Their task is to provide a general interface from the detector to the DAQ system, pre-format the event data by adding a header and a trailer (see section 1.4) or performing zero suppression [Gro98a], and de-randomizing the event data. The latter ensures that event data is sequentially transferred to the DAQ system. Furthermore a small buffer with a size in the order of 16 words is present.

## **Readout Links**

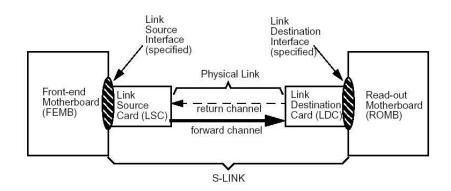

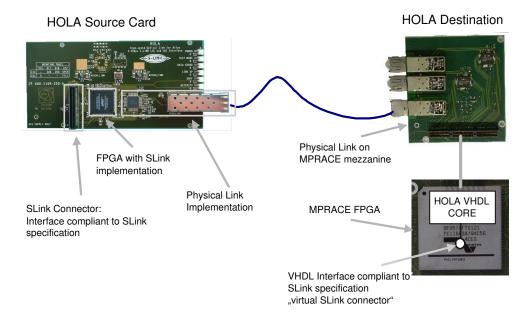

Altogether 1600 readout links (ROL) transport the event data over a distance of up to a few hundred meters from the RODs to the readout buffers. The used technology is SLink a custom unidirectional point-to-point link standard developed at CERN [BMvdB97]. Its concept is shown in Figure 1.5.

SLink defines the interface between link implementation hardware and the user electronics. Data is always transferred in one direction from the SLink source card (LSC) to the SLink destination card (LDC). The interface to the source card prescribes 32 data signals and a clock signal with up to 40 MHz which have to be supplied to the LSC. Data arrives on a 32 Bit bus on the receiver (LDC) side together with the 40 MHz clock. Furthermore an error signal is raised when data has been corrupted during transmission.

The return channel (from the LDC to the LSC) plays a minor role and comprises 4 data bits and a flow control signal. The latter can be used to signal a link full condition to the user hardware.

**Figure 1.5:** The CERN SLink standard. Only the link source and destination interfaces are specified together with the outline of the interface cards. The physical implementation is application dependent [BMvdB97].

The link technology is not fixed in the SLink standard. It has to be implemented on a mezzanine which uses the electrical signals from the SLink connector. The outline of the mezzanine and the SLink connector are determined by the SLink specification. Various physical link implementations are available: electrical parallel, electrical serial, and optical [vdBH].

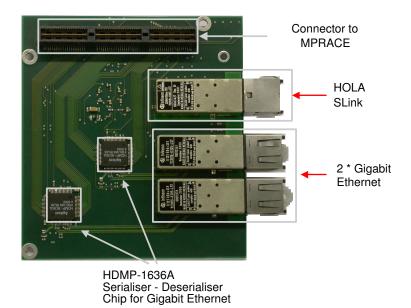

The ATLAS experiment uses an optical implementation, which is called HOLA (High Speed Optical Link for ATLAS), between the RODs and the ROBs. It is based on a 2 GBit/s optical transceiver [RvdBH] with a throughput of up to 160 MByte/s. The source and destination cards use an FPGA to implement the SLink functionality. This FPGA controls the optical transceiver and the serialiser to transfer the data and control words and communicates with the SLink user through the standardised SLink connector.

### Level 2 Trigger

The level 2 trigger is the second instance for trigger decisions in the ATLAS DAQ chain. It takes the RoI information from level 1 which has been collected from the level 1 trigger processors by the RoI builder. The trigger is implemented within a large farm of dual-CPU PCs connected over a Gigabit Ethernet network. A number of supervisor PCs control the level 2 farm and distribute the trigger tasks and the RoI information collected by the RoI builder.

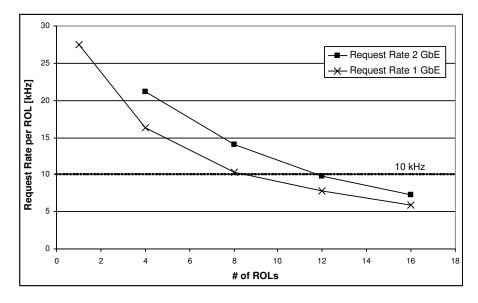

Level 2 is based on program driven trigger processor (see 1.1). Furthermore it requests the required event data from the readout buffers. This might happen in several steps depending on the trigger decision algorithm ("sequential selection"). Each event accepted by the level 1 trigger is investigated by one level 2 processor. The RoI concept prevents that all event data is requested by the trigger with a rate of 100 kHz. Since the data of only a small number of readout buffers, covering the desired area of the detector, is required, the amount of data to the level 2 processor is very limited. In average the level 2 trigger requests only 7% of all event data arriving from the detector per ROL. This corresponds to 7 kHz in average for a level 1 rate of 100 kHz per readout buffer.

The level 2 farm size can be obtained from a detailed model of the ATLAS DAQ chain. This is done within a C++ program [Ver] simulating the level 2 trigger, succeeding stages, and data transport and assembling delays. It is expected by this model that 496 PCs will be needed to process all events accepted from level 1 with the above mentioned trigger menu. The calculation is based on the assumption to have 8 MIPS (million instructions per second) CPUs

within the PCs available. The mean latency for computing the trigger decision is expected to be approximately 10 ms [Gro03] with a large variation from event to event. In the worst case single events may require many times the mean latency for decision while events may also be processed within a much smaller time. Finally 2-3% of all events accepted from level 1 also pass the level 2 trigger.

## Readout Subsystem (ROS)

The readout subsystem (ROS) stores the event data received from the readout drivers during the level 2 decision. For each of the 1600 readout links, coming from the RODs, one readout buffer (ROB) has to be provided which is large enough to cover the level 2 latency of 10 ms with its large variation for single events.

Besides buffering of data, the ROS also serves requests for RoI data coming from the level 2 farm via Gigabit Ethernet. In case of a level 2 accept all data has to be passed to the event building process with a second Gigabit Ethernet interface. Thus approximately 10% (7% RoI requests + 2-3% level 2 accept) of all event data coming from the ROD leaves the ROBs towards the level 2 and event building farms.

Due to the large difference between input and output the main architecture concept for the ROS implementation is to group a number of ROL inputs and buffers to one network output. This guides the architecture design choice for the ROS which will be explained in detail within the next chapter.

### **Sub-Farm Input**

On level 2 accept all fragments inside the 1600 ROBs are merged into one event data block for a final investigation by the third trigger level, the event filter. This merging is done within the sub-farm interface (SFI). A farm of approx. 59 PC's [Gro03], all of them interconnected via a Gigabit Ethernet switching network, is responsible for the collection of event data fragments from all ROBs. The farm merges them into one and passes this data block over to the event filter processors. The whole process is initiated and controlled by the dataflow manager (DFM) which assigns each accepted event one SFI node to perform the event building operation.

The SFI farm must reach an overall event building rate which is equal to the level 2 accept rate of 2-3 kHz (having a level 1 accept rate of 100 kHz). This requirement determines the farm size of 59 PC's which has been again calculated using the ATLAS DAQ model from [Ver]. Another value influencing the SFI farm size is the number of event data fragment sources. These are the ROB outputs. Their number depends on the proportion between ROB inputs and outputs. This will be explained in detail in the next chapter.

## **Event Filter**

The event filter (EF) is the final trigger level of the ATLAS DAQ. It analyses the whole event in detail thereby reducing the data rate by a factor of 10-20. This is done using modified versions of offline algorithms which are normally used for the analysis of the already recorded data.

The EF is again implemented in a PC farm connected to the SFI farm via a Gigabit Ethernet switching network. On event filter accept the data leaves the DAQ chain through the sub-farm outputs (SFO) to be permanently recorded on a disk array. The final event rate at the SFO is

in the order of 200 Hz. A data stream of  $\sim$ 200 MByte/s has to be written to the permanent storage medium.

## **1.4 The ATLAS Data Acquisition Event Format**

The event data running through the previously described ATLAS data acquisition chain follows certain data format guidelines. These are specified in  $[BFM^+04]$ . The data format has been developed to support various features (from  $[BFM^+04]$ ):

- The event data format contains information redundancy to allow self consistency checks of the event.

- The event format provides information whether the event has been corrupted during transmission within the data flow.

- The event formatting information does not exceed 20% of the typical ATLAS event data size.

- The event format is modular.

- The event format facilitates the identification of fragments.

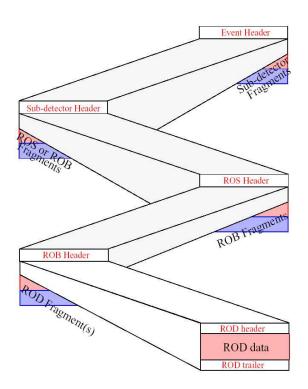

Figure 1.6: The ATLAS event format [BFM<sup>+</sup>04].

Starting at the readout drivers (ROD) each instance of the ATLAS DAQ adds a header, containing a set of information, to the event data. This is shown in Figure 1.6. The complete event consists out of a number of sub-detector fragments. Each of them again consists out

**Figure 1.7:** The ROD event fragment format [BFM<sup>+</sup>04].

of multiple ROS or ROB fragments. A ROS fragment is built on the level of a ROS, which groups a number of readout buffers (ROBs). Thus a ROS fragment contains a number of ROB fragments. The ROB fragment is built on the level of the readout buffer. Each ROB fragment contains one ROD fragment, supplied and formatted by the ROD out of the ATLAS raw event data.

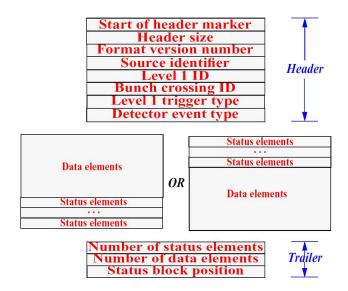

Firstly, the ROD adds a header and a trailer to the data containing information about data sizes, event source, the level 1 ID (a unique number within a certain time assigned by the level 1 trigger), the bunchcrossing ID (a unique number within a certain time for each LHC event), and some information why level 1 has accepted this event. This ROD data format is shown in Figure 1.7.

| Fragment Type | Start-of-Header Marker |  |  |

|---------------|------------------------|--|--|

| ROD           | 0xee1234ee             |  |  |

| ROB           | 0xdd1234dd             |  |  |

| ROS           | 0xcc1234cc             |  |  |

| Sub-Detector  | 0xbb1234bb             |  |  |

| Full Event    | 0xaa1234aa             |  |  |

Table 1.2: The Start-of-Header Marker encodings for the various event fragment types up to the full event [BFM<sup>+</sup>04].

Secondly, the readout buffer adds a similar header to the event data containing redundant information from the ROD header and status information. The result is a ROB fragment. This continues on the level of the ROS (a composition of ROB fragments), the sub-detector (containing all ROS fragments of one sub-detector), and finally the complete event which is built by the SFI (see the previous section).

The first word of each header contains a value defining the type of the header. This allows the identification of the instance which has built the fragment. Table 1.2 shows these "Start-of-Header" markers used within the event data format. Upon this marker the data format and type of contained fragments can be determined.

# Chapter 2

# The Atlas Readout Subsystem Architecture

This chapter describes in detail the ATLAS readout subsystem (ROS) for which this thesis will present an implementation approach. The first section summarises the external dependencies of the ROS component. The second gives an overview of previous readout buffer implementation approaches and presents ATLAS ROS architectural choices.

## 2.1 Requirements for the ATLAS Readout Subsystem

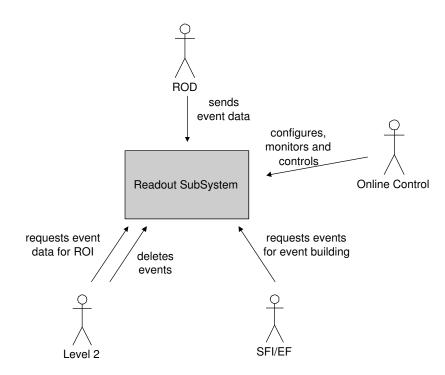

The readout subsystem (ROS) is one of the central devices in the ATLAS data acquisition chain. It collects all data accepted by the level 1 trigger and makes them available to the level 2 trigger on demand. As it is placed in the main ATLAS data flow, it has to fulfil a number of requirements in terms of performance and usability.

Figure 2.1: The ROS dependencies [RMR02].

Figure 2.1 shows the dependencies of the ATLAS ROS and external DAQ components. Input data is coming from the readout drivers (ROD) while the level 2 trigger and the subfarm input (SFI) are located at the ROS output. Finally the ATLAS online control configures and controls the ROS component. All external dependencies are presented in more detail below complemented with a quantification of the load.

## **Readout Driver**

The readout driver pushes event data, accepted by the level 1 trigger, into the readout buffer system. 1600 readout links, conform to the HOLA SLink implementation [RvdBH], are used to transfer the data of the seven sub-detectors to the ROS. Each of these links has a nominal bandwidth of 160 MB/s. Data arrives with the level 1 accept rate of up to 75 kHz upgradeable to 100 kHz (see 1.3).

Each of the sub-detectors delivers a different event fragment size via the SLink connection. This size is determined by the quantity of physical processes and also by the luminosity of the LHC accelerator. It can be estimated by a detailed examination of the physical processes inside the ATLAS detector. Table 2.1 summarises the results for the initial LHC luminosity of  $2 \cdot 10^{33} \, cm^{-2} \, s^{-1}$  and the design luminosity of  $1 \cdot 10^{34} \, cm^{-2} \, s^{-1}$  which will be achieved later by the experiment.

| Sub-Detector       | Number of ROLs | Initial Luminosity | Design Luminosity |

|--------------------|----------------|--------------------|-------------------|

|                    |                | [Byte]             | [Byte]            |

| Pixels             | 120            | 200                | 500               |

| SCT                | 92             | 300                | 1100              |

| TRT                | 232            | 300                | 1200              |

| EM Calorimeter     | 740            | 752                | 752               |

| Hadron Calorimeter | 88             | 752                | 752               |

| Muon precision     | 192            | 800                | 800               |

| Muon trigger       | 48             | 380                | 380               |

| CSC                | 32             | 200                | 200               |

| Level 1 trigger    | 56             | 1200               | 1200              |

| Total              | 1600           | 1.0 MByte          | 1.3 MByte         |

**Table 2.1:** The number of readout links (ROL) and the fragment sizes per link for the ATLAS subdetectors. The experiment starts at the initial luminosity of  $2 \cdot 10^{33} \text{ cm}^{-2} \text{s}^{-1}$ . Later the design luminosity of  $1 \cdot 10^{34} \text{ cm}^{-2} \text{s}^{-1}$  will be reached [Col99].

These numbers are based on the assumption that the RODs perform a zero suppression and compression of data for some sub-detectors (especially the electromagnetic calorimeter). This has not yet been decided. Thus data fragment sizes of up to 1.6 kByte may be possible for the electromagnetic calorimeter [Fra04].

## Level 2 Farm

The level 2 trigger supervisor receives on level 1 accept a set of RoI definitions for further investigation within the level 2 farm. It assigns a farm processor which starts to collect event data fragments from the ROS. Due to the RoI principle of the level 2 operation, only event

data from a specific area of the detector is required (see section 1.3). Furthermore the data from a number of sub-detectors is taken into account and data may be requested subsequently in several steps by the trigger algorithm.

Thus estimating the event data rate which each ROB inside the ROS has to deliver to the level 2 farm needs a model of the level 2 algorithms and the knowledge of the ATLAS trigger menu. This modelling effort is done within the ATLAS modelling group [Atl]. A complete model of the ATLAS DAQ chain, starting with the level 1 trigger, is done within this group [Ver]. Its major assumptions are:

- The trigger menu from Figure 1.4 determinating the level 1 accept rate.

- The event fragment sizes from Table 2.1.

- Dual CPU PCs with 8 MIPS processors for the level 2 farm.

- A Gigabit Ethernet network to connect the level 2 farm with the ROS using the UDP/IP protocol [Pos80] [Pos81].

- A custom transport layer protocol on the top of UDP defined by the ATLAS DataCollection Group [Hau03].

| Sub-Detector       | Low Lur | ninosity | Design Luminosity |         |

|--------------------|---------|----------|-------------------|---------|

|                    | Average | Max.     | Average           | Max.    |

|                    | [ kHz ] | [ kHz ]  | [ kHz ]           | [ kHz ] |

| Pixels             | 0.67    | 0.98     | 0.99              | 1.42    |

| SCT                | 0.53    | 0.74     | 0.79              | 1.08    |

| TRT                | 0.19    | 0.22     | 0.04              | 0.05    |

| EM Calorimeter     | 2.03    | 7.42     | 1.74              | 6.34    |

| Hadron Calorimeter | 1.36    | 1.99     | 0.89              | 1.30    |

| Muon precision     | 0.10    | 0.20     | 0.29              | 0.57    |

| Muon trigger       | 0.22    | 0.30     | 0.62              | 0.86    |

• A bandwidth limit of 60 Mbyte/s to the SFI event building farm.

Table 2.2: Estimation of the level 2 request rates per readout buffer. One readout buffer stores the data from one ROL [Col99].

An estimation of the level 2 request rate per readout buffer (ROB), obtained using this model, is summarised in Table 2.2. One ROB stores the data arriving from one ROL. Table 2.2 presents a maximum and average request rate per ROB depending on the sub-detector. Together with the event sizes shown in Table 2.1 each ROB generates the data volume listed in Table 2.3.

Both tables show that the most request load is generated on Buffers handling the data from the calorimeter sub-detector. Up to 7.43 kHz or 5.58 MByte/s flow from the readout buffer to the level 2 farm at initial luminosity. This is caused by the level 2 trigger algorithm which needs in most cases data from the calorimeter first. At design luminosity this value decreases.

The readout buffers have to keep the event data at least for the level 2 processing time which is expected to be up to 10 ms with a large event by event variation (see 1.3). With an input rate of 100 kHz and the event fragment sizes listed in Table 2.1 a minimum memory size (without any safety factor) of 1200 kByte must be available in each ROB.

| Sub-Detector       | Low Lu    | minosity  | Design Luminosity |           |  |

|--------------------|-----------|-----------|-------------------|-----------|--|

|                    | Average   | Max.      | Average           | Max.      |  |

|                    | [MByte/s] | [MByte/s] | [MByte/s]         | [MByte/s] |  |

| Pixels             | 0.13      | 0.20      | 0.50              | 0.71      |  |

| SCT                | 0.16      | 0.22      | 0.87              | 1.19      |  |

| TRT                | 0.06      | 0.07      | 0.05              | 0.06      |  |

| EM Calorimeter     | 1.53      | 5.58      | 1.31              | 4.77      |  |

| Hadron Calorimeter | 1.02      | 1.50      | 0.67              | 0.98      |  |

| Muon precision     | 0.08      | 0.16      | 0.23              | 0.46      |  |

| Muon trigger       | 0.08      | 0.11      | 0.24              | 0.33      |  |

Table 2.3: The bandwidth needed for data requests per readout buffer. One readout buffer stores the data from one ROL [Col99].

## **SFI and Event Filter**

On level 2 accept the event data of all ROBs within the ROS is requested by the sub-farm input (SFI) PCs for event building. In average 3% of all events accepted by level 1 are left at this point. With a level 1 accept rate of 100 kHz, this adds another 3 kHz to the output rate of each ROB. Depending on the sub-detector, between 0.6 and 3.6 Mbyte/s additional bandwidth is used per ROB for this process. All event data rejected by level 2 will no longer be used within the ATLAS DAQ and is deleted at the ROB level.

### **Online Control**

Finally the ATLAS online control system is responsible for ROS configuration and control. This requires the ROS to provide an implementation of a generalised software interface. Having this, the online control can pass configuration data and is able to switch between various run levels. Errors are also reported through this interface [Gro03].

Event monitoring may also be requested by online control. This means that the ROS collects and delivers event data by a configurable set of parameters [Gro03]. Currently requirements and implementation details for event monitoring on the level of the ROS are not completely specified.

## 2.2 Readout Buffers in Other Experiments

The staged trigger architecture is widespread at various currently operational high energy physics experiments. The trigger strategy is in most cases similar. Only the number of trigger levels and their implementation differs from experiment to experiment.

The currently most demanding are CDF and D0 at Tevatron (Run IIb) and BaBar at PEPII (see 1.1). The data acquisition and trigger strategy of the two Tevatron experiments is very similar. There are three trigger levels to reduce the detector event data. The first two use custom hardware operating on partial event data. The third level, a PC farm, analyses the complete event after it has been reconstructed ([Col02b] [Col02d]).

The BaBar experiment has only two trigger levels. The first level trigger is built with custom hardware and on accept the event building process immediately starts. Finally a PC

farm analysis the complete event as it is done at D0 and CDF [Col95a].

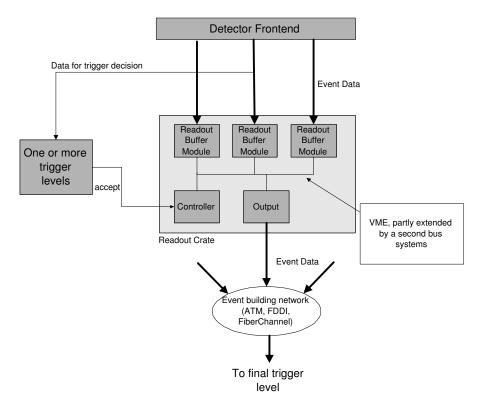

**Figure 2.2:** The generalised and simplified event data flow through trigger and readout buffer components used by many experiments. A similar system can be found in the data acquisition of CDF [Col02b], D0 [Col02d], BaBar [Col95a], [RMR02], and others.

In all experiments a readout buffer component stores the detector data prior to event building. The event data fraction required by the trigger is previously branched and directed into the trigger processor(s). If the level 2 (CDF, D0) or level 1 (BaBar) has accepted the event, data leaves the readout buffer component for event building and further analysis.

This data acquisition and trigger strategy is shown in Figure 2.2 with the focus on the readout buffer component. Its main operation in all above mentioned experiments is to read the event data from the detector, buffer it, and forward it on trigger accept. Therefore VME bus crates with a number of custom modules or single board computers are present. These readout modules provide the detector link destination and store the event data. On accept, data is transported over the VME bus to the output component and sent to the event building network. Partly the bandwidth of VME is extended by the use of a custom bus system (e.g. the "Magic Bus" in D0).

All LHC experiments, except ATLAS, follow the same trigger and data acquisition strategy. The main difference to previous experiments is the extended use of standard, "of-theshelf" components. PC farms are used already in early trigger stages; in most cases already for level 2.

This is continued in the design of the readout buffer components used by the LHC experiments ALICE [Col04] and CMS [Col02c]. In all cases the bus system has changed from VME to PCI and the crate is a standard, industrial, high performance PC.

The readout modules are based on FPGAs and receive the event data on custom, high performance links. The ALICE readout buffer forwards this data directly into the memory of

the PC. At CMS memory is attached to the FPGA to store the event data received from the detector.

Only LHCb has decided to use a Gigabit Ethernet network approach instead of the PCI bus. There, a number of readout buffer modules handle the custom detector link and buffer the event data. Each of them has a Gigabit Ethernet port to deliver the data on trigger accept.

The ATLAS trigger and data acquisition is different to all of the above mentioned experiments. The level 2 trigger operates as a program-driven trigger processor (see 1.1). Furthermore it uses "sequential selection". This means that only that event data, required for the trigger decision, is requested from the readout buffers. Another specific characteristic is the RoI concept which reduces the amount of necessary data for the level 2 trigger decision. This is only rarely found at high energy physics experiments.

Sequential selection has a major impact on the readout buffer component since it must supply the event data on request. This puts additional complexity to the design of the readout buffer compared to all previously mentioned experiments.

One already operating experiment with a similar mechanism inside the level 2 trigger is HERA B. This experiment has a four level trigger architecture. The first level is implemented completely in custom hardware. Starting from trigger level 2 all computations are done by PC farms.

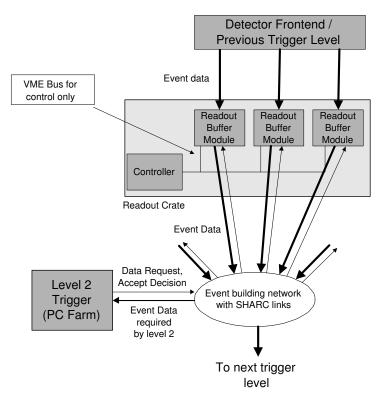

Figure 2.3 shows the HERA B event data flow with the focus on the level 2 trigger and buffer.

Figure 2.3: The HERA B event data flow with the focus on the second trigger level. This uses similar mechanisms than ATLAS [Wol98] [Col95b].

Detector data accepted from the first trigger level is stored in the readout buffer with a rate of 50 kHz. The readout buffer is based on SHARC DSP processors placed on VME crate modules. Each processor provides a number of 40 MByte/s serial links used for event

data transport towards the second trigger level and event building. The second trigger level requests and receives all required event data by theses SHARC links. Approximately 3% of all data is required for level 2. On accept, event building starts by sending the event data fragments from the various SHARC processors to one level 3 trigger node. This is done with the level 2 accept rate of approximately 2 kHz [Wol98].

Thus the ATLAS trigger and data acquisition with its level 2 trigger requesting the required event data from the readout buffers has a unique position within the high energy physics experiments. The architecture can not be compared to other LHC or Tevatron experiments. Only the HERA B trigger has similar conditions, but with a four times smaller detector event rate and using different technologies (SHARC links instead of Gigabit Ethernet). This comprises also the ATLAS readout subsystem. Contrary to all other experiments it has to provide the RoI event data to the level 2 farm on demand. This complicates the architecture and implementation and makes it a new development.

## 2.3 ATLAS Readout Subsystem Architecture

## 2.3.1 Architectural and Technology Choices

## **ROS** grouping

For the ATLAS readout subsystem various architecture approaches have been discussed in the ATLAS community. Due to the high input and the low output rate, the concentration of a number of input links to one network output has been accomplished as a basic rule to all approaches. This principle can also be found by all other high energy physics experiments (see 2.2).

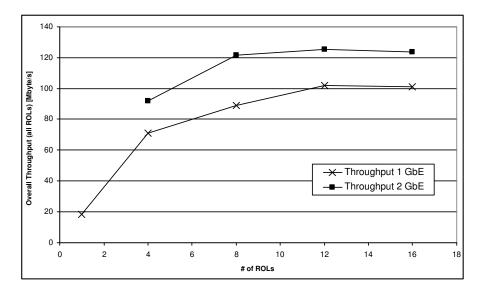

The number of combined input links are limited by the Gigabit Ethernet bandwidth and varies for different ATLAS sub-detectors. A first evaluation, only based on a simple comparison between the required input and output bandwidth (presented in section 2.1), estimates that between 14 and 70 inputs can be connected to one Gigabit Ethernet output depending on the sub-detector. This approach drastically decreases the number of Ethernet links between the ROS and the level 2 and SFI farm.

An extension to the combining of input links to one output is the possibility of local, partial event building inside the ROS. This means that a number of ROB packets are merged into one ROS packet as defined in the ATLAS Data Format specification 1.4. The result is a reduced number of messages and data packet frames exchanged between the SFI and ROS.

Estimations with the paper-model from [Ver] (already introduced in the previous chapter) show that this can reduce the SFI farm size. Without merging of fragments inside the ROS, 83 PCs have to be present in the SFI farm to meet the 2-3 kHz event building rate <sup>1</sup>. With a grouping of 16 inputs to one output and partial event building this decreases to 28 PCs. Thus approximately 50 PCs can be saved in the SFI farm. Also the level 2 farm decreases by a 5-8 PCs due to the reduced number of messages (again with a grouping factor of 16).

<sup>&</sup>lt;sup>1</sup>The SFI farm size has been obtained from the model contrary to the values presented in the TDAQ TDR [Gro03] with a Gigabit Ethernet bandwidth of 100 MByte/s. The original bandwidth was assumed to be 60 MByte/s (see section 2.1).

## **Technology Choices**

Regarding the other experiments described in section 2.2 a number of implementations for the ATLAS ROS can be considered and discussed.

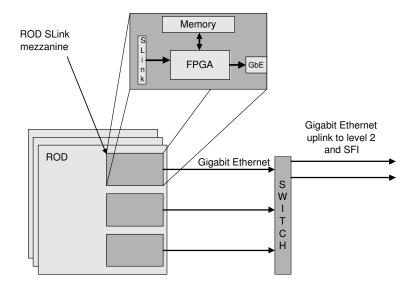

**Figure 2.4:** The ROB-on-the-ROD scenario. A readout buffer mezzanine replaces the SLink implementation mezzanine on the ROB VME board. [BBF<sup>+</sup>02]

One of the simplest scenarios for ATLAS uses one readout buffer module per detector ROL equipped with SLink input, some memory, an FPGA, and Gigabit Ethernet output. This is similar to the CMS approach (or HERA B, but without the SHARK links).

One possibility is to place this hardware directly on the readout driver replacing the foreseen SLink mezzanine hardware (see 1.3). This simple approach is called "ROB-on-the-ROD" concept [BBF<sup>+</sup>02](see Figure 2.4).

The fragments, sent by the readout driver (ROD), are buffered inside the on-board memory and delivered via Gigabit Ethernet to the level 2 or SFI event builder farm. A concentrator switch combines the Ethernet links of a number of modules into one or two up-links to the level 2 and SFI farm.

In a similar scenario the readout buffer modules could be placed on 3, 6, or 9  $HU^2$  boards hosted in a simple crate with only a power supply. Up to 5 buffers could be implemented on a 6 HU board each having one HOLA SLink input and one Gigabit Ethernet output, up to 8 on a 9 HU board and only 2 on a 3 HU board. The number of links is limited by the available space on the front of the board. One link (either Ethernet or HOLA SLink) is estimated to allocate 2 cm of the board's front panel.

Still one Gigabit Ethernet link per ROL is present which is grouped by a number of concentrator switches into a number of up-links towards the trigger and SFI farms. All scenarios mentioned up to now do not merge event data fragments. The number of Ethernet messages and thus the SFI farm size is not reduced.

This can be taken into account by increasing the logic of the above mentioned boards. This may increases the number of ROLs handled and reduces the number of messages between the level 2 / SFI farms and the ROS. Out of space considerations up to 8 links could be placed on a

$<sup>^{2}</sup>$ HU is a unit for the height of electronic boards. Each HU is equal to 1.75 inches. Thus 9 HU corresponds to 400.5 mm, 6 HU to 266.7 mm, and 3 HU to 133,35 mm.

6 HU, 14 on a 9 HU, and 3 on a 3 HU board while always 2 Gigabit Ethernet links are present. This approach requires a completely custom ROS design which is not intended by the ATLAS community.

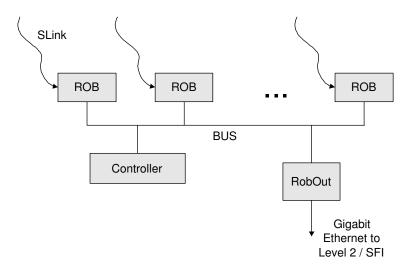

**Figure 2.5:** ROS Module with local event building via a standard bus (VME, PCI). A number of ROBs receive data from the ROL, buffer it, and send it to the bus on request. The network interface is attached to the module bus too.

Many other experiments (see 2.2) use commercial bus technologies like VME or PCI. This has also been discussed within the ATLAS community. A scenario where a number of simple custom or commercial boards receive the event data from the ROLs, buffer it, and deliver it via a commercial bus system is shown in Figure 2.5. The Gigabit Ethernet network connection, which is sitting on the module bus too, delivers the event data packets to the level 2 and event filter farm.

Multiple ROLs may be handled by one custom VME or PCI board independently, depending on the available space. A PCI board for example has space for up to four HOLA SLink inputs on the front side. A CompactPCI <sup>3</sup> system may carry up to seven 3 or 6 HU boards, each with four or eight links.

This bus-based scenario is very popular within the ATLAS community and a number of various prototypes have been developed and tested. They are summarised section 2.3.3. The bus-based approach is similar to the component used in other experiments. The main difference is the major technology update by using modern PCs and the PCI bus. Furthermore the ATLAS component has an increased complexity due to the level 2 event data requests (sequential selection).

## 2.3.2 Cost Modelling

Since the ATLAS readout subsystem will be a huge system, processing and buffering data from 1600 sources and answering requests from two large PC farms over Gigabit Ethernet, the overall system costs are an important issue. A number of architectural choices have been discussed within the community and several of them have been presented in the last paragraph.

<sup>&</sup>lt;sup>3</sup>CompactPCI is a PCI standard variant for industrial applications. It defines a bus system equal to PCI but with a alternative connector used within 6 HU crates. CompactPCI boards may be 3 or 6 HU

Many different components have been proposed including a number of custom hardware components. Their costs have to be estimated with the goal to get a complete overview of the price of a full system for the various architectural options.

This cost modelling has been done in the ATLAS community [Mor03] and is summarised and partly extended here. It tries to calculate the prices for the scenarios presented in the previous section 2.3.1 which are:

- The ROB-on-the-ROD scenario

- The scenarios using 3, 6 or 9 HU ROB boards with one Ethernet output per ROL input in a simple crate with only a power supply. Each ROB board has one Gigabit Ethernet output per ROL input.

- The scenarios with "grouping" 3, 6 or 9 HU ROB boards in a simple crate with only a power supply. Each board has N HOLA SLink inputs (see previous section for the specific number), two Gigabit Ethernet outputs, and performs local event building on request data.

- The bus-based scenario with PCI based ROB boards in a standard PC (ROS-PC).

A VME based scenario, as used in many other experiments (see section 2.2), has not been taken into account because prototyping effort has shown that the ATLAS requirements can not be met (see next section 2.3.3).

The prices assumed for the various components are listed in Table 2.4. For all custom components prices have been obtained from [Mor03]. No difference is made between the price for the simple 3, 6, or 9 HU boards and the "grouping" boards which perform local event building. The 3 HU is assumed to be equal to a PCI ROB board.

| Component                       | Price | Source       |

|---------------------------------|-------|--------------|

|                                 | [EUR] |              |

| ROBs                            |       |              |

| ROB-on-the-ROD module           | 400   | [Mor03]      |

| 3 HU board (with 2 ROBs)        | 1500  | equal to PCI |

| 6 HU board (with 5 ROBs)        | 4500  | [Mor03]      |

| 9 HU board (with 8 ROBs)        | 7500  | [Mor03]      |

| PCI ROBIN board (4 SLinks)      | 1500  | [Mor03]      |

| Switches                        |       |              |

| 16-Port Switch (price per port) | 80    | [Alt]        |

| Crates (simple, no bus system)  |       |              |

| 6 HU (with power supply)        | 700   | [RSC]        |

| 9 HU (with power supply)        | 800   | [RSC]        |

| PC                              |       |              |

| standard PC with 4 PCI segments | 1500  | [Mor03]      |

Table 2.4:

The prices for various components used for the different ROS scenarios 2.3.1.

This leads to the costing estimations for a complete system listed in Table 2.5. The presented model neglects a number of topics. It should only support the design choice with a raw price estimation. The omitted topics are:

- Influence of the scenarios to other parts of the ATLAS DAQ (SFI or level 2 farm size, number of switches for the level 2, SFI farm, ...).

- Cable costs.

- The cost of racks.

| Scenario       | ROB    | Crates | Switch | Estimated System |

|----------------|--------|--------|--------|------------------|

|                | Boards | PCs    | Ports  | cost [EUR]       |

| ROB-on-the-ROD | 1600   | Х      | 1800   | 784.000          |

| Simple 3 HU    | 800    | 50     | 1800   | 1.379.000        |

| Simple 6 HU    | 320    | 20     | 1800   | 1.598.000        |

| Simple 9 HU    | 200    | 13     | 1800   | 1.653.100        |

| Grouping 3 HU  | 540    | 20     | Х      | 837.200          |

| Grouping 6 HU  | 200    | 13     | Х      | 909.100          |

| Grouping 9 HU  | 133    | 9      | Х      | 1.004.700        |

| PC ROS         | 400    | 133    | Х      | 799.000          |

Table 2.5: The estimated costing of a complete ROS for the different scenarios. The prices for the components have been taken from Table 2.4. 2.3.1.

For the first four scenarios a large number of switches are necessary which connect the ROBs to the level 2 and SFI farm. Each of them is considered to have 16 ports. Two uplinks are counted per 16-port switch and added to the 1600 ports necessary to connect the ROBs. This leads to a network with 1800 ports. No switches are added to the remaining three scenarios because the ports are intended to be already present in the level 2 and SFI farm switch (which is not taken into account here). Depending on the ROS grouping factor (the number of ROLs per ROS component) a number of ports, in the order of 200 - 300, must be present in the level 2 and SFI farm switch. This is equal to the previously mentioned number of up-links and makes the model consistent.

With this calculation the ROB-on-the-ROD scenario is the cheapest closely followed by the PC ROS. Since the PC ROS approach performs partial local event building, it reduces the SFI farm contrary to the ROB-on-the-ROD scenario. This gives the PC ROS an advantage even though it is not the most cost effective solution.

## 2.3.3 Previous Implementation Approaches

During the planning phase of the ATLAS DAQ system a number of approaches for the readout subystem has been investigated. All of them follow the bus based scenario presented in the last section. Three buses have been evaluated: VME, PCI and CompactPCI.

In all cases a custom ROB module with the evaluated bus interface has been developed which is called ROBIN (readout buffer Input). It is based in most cases on a microcontroller and a FPGA with additional buffer memory storing the event data from the readout links.

## **CERN VME ROS**

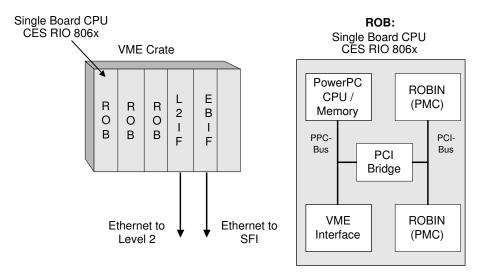

The VME ROS implementation shown in Figure 2.6 has been developed at CERN [CFJ<sup>+</sup>00]. It is based on a number of CES RIO 8062 [CES] single board computers running LynxOS.

These CPUs are contained in a VME crate and have different tasks. There are CPUs acting as an interface to the level 2 farm (L2IF) and the SFI event builder farm (EBIF). Other CPUs act as ROBs receiving and buffering data from the RODs. Event data is moved by the VME bus between the ROB boards and the interface boards.

Figure 2.6: VME ROS implementation with single board computers in a VME crate [CFJ<sup>+</sup>00].

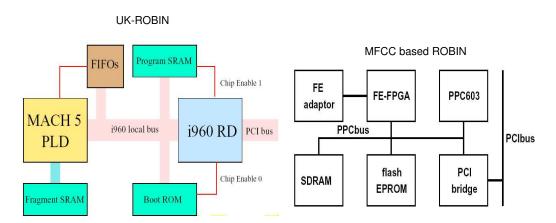

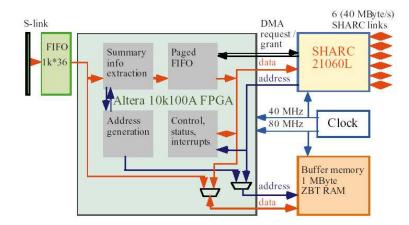

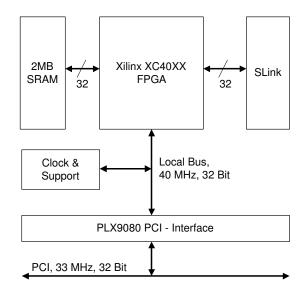

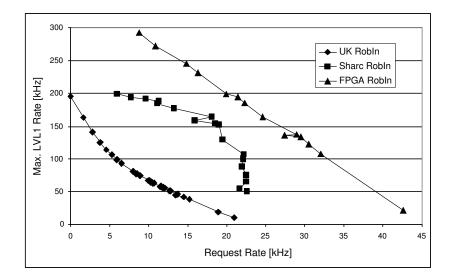

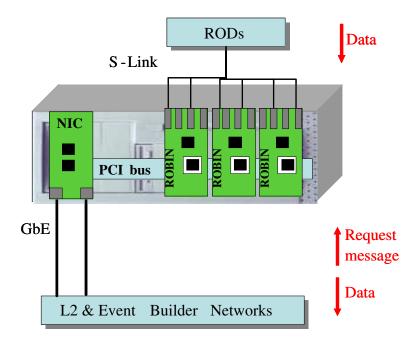

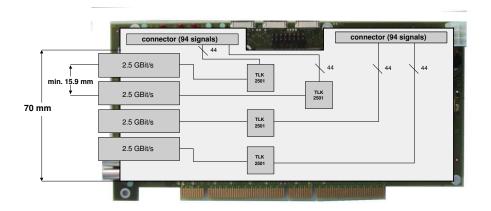

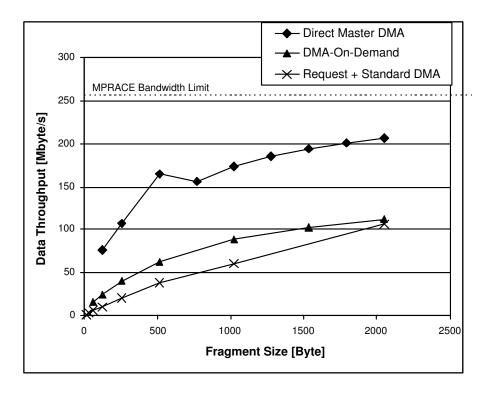

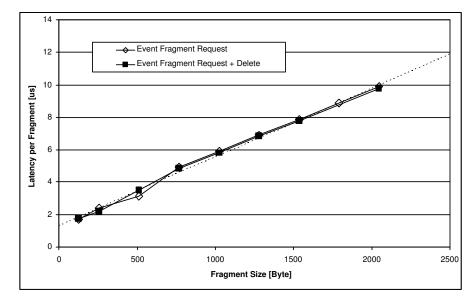

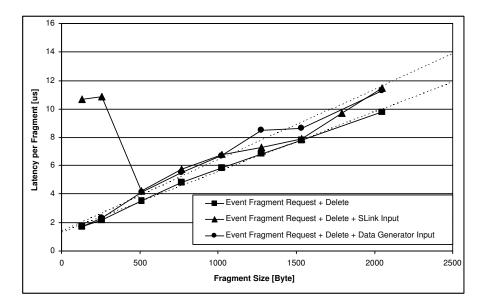

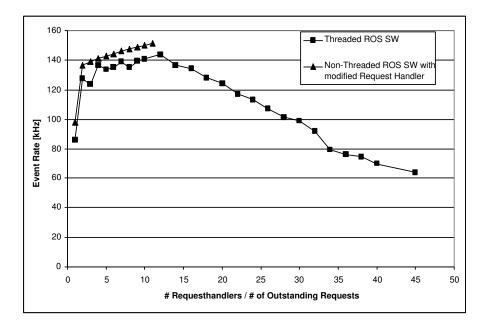

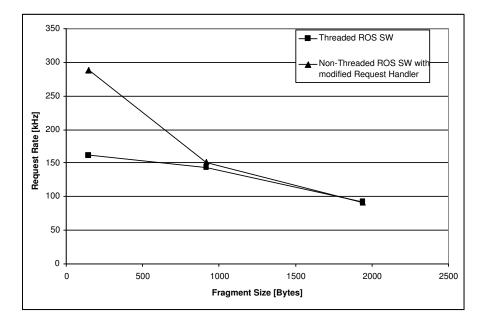

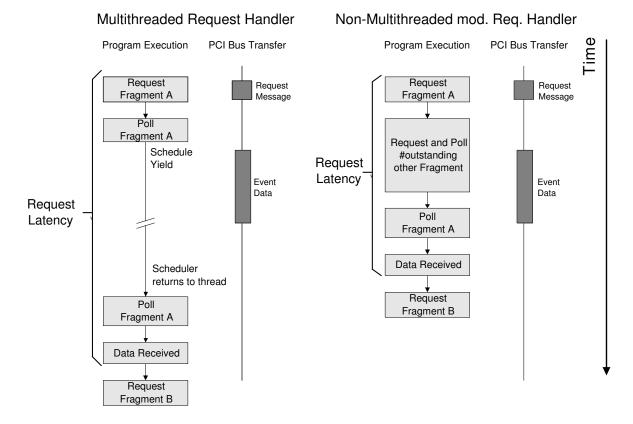

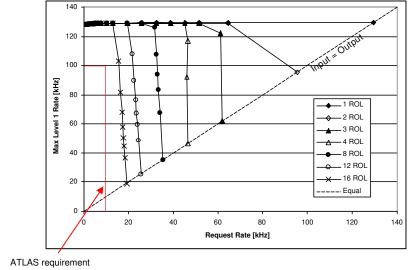

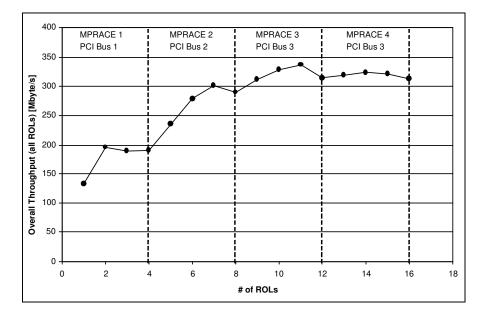

The RIO 8062 single board computer is based on a PowerPC 604e CPU and contains a PCI bus with two PMC (PCI Mezzanine Card) format slots. These are used to carry two ROBIN boards for receiving and buffering the data from one ROL. Two options have been tested: one based on another single board computer, the RIO MFCC 8441, and the UK-ROBIN. Both are schematically shown in Figure 2.7.