## Architecture and Prototype of a Real-Time Processor Farm Running at 1 MHz

Inauguraldissertation zur Erlangung des akademischen Grades eines Doktors der Naturwissenschaften der Universität Mannheim

vorgelegt von Alexander Walsch, Master of Science aus Günzburg

Mannheim, 2002

Dekan: Professor Dr. Herbert Popp, Universität Mannheim

Referent: Professor Dr. Volker Lindenstruth, Universität Heidelberg Korreferent: Professor Dr. Reinhard Männer, Universität Mannheim

Tag der mündlichen Prüfung: 6. November 2002

# Abstract

Triggers are key components in large scale high energy physics experiments. Nowadays experiments produce data at a rate of several TByte/s, which is more than any storage system can handle. Not all of the data produced is of importance and as a matter of fact only a tiny amount of all events are interesting to the experiment. Thus, data has to be reduced in real-time. This is commonly done by pipelined trigger systems.

The Level-1 trigger of the LHCb experiment is a hardware/software based system built around standard components whenever possible. The trigger is the second stage in the LHCb trigger pipeline having an average input of 1 MHz and a bandwidth requirement of more than 4 GByte/s. The input data is initially split amongst several input feeds with sub-events being as small as 128 Byte. Data have to be sent to a compute node which runs a track finding algorithm and produces a result message at a MHz rate.

The system uses a high-speed network available off-the-shelf which connects commodity PCs. The interface to the NIC is PCI.

The thesis gives an overview of the different networking requirements that have to be met to satisfy the LHCb boundary conditions. The requirements of the project do not allow to use common data transfer methods. However, based on a shared memory architecture a new method of transferring data is introduced. The method uses additional reconfigurable logic which allows to send data in bursts over the PCI bus directly into the network inducing almost no overhead.

Based on the Scalable Coherent Interface, tests concerning speed, throughput, latency, and scalability are presented. Based on the latest simulation results done at CERN, an approximate system size is calculated and a basic timing analysis of the system is given. The system is characterized by multiple nodes sending to one single receiver. Therefore, the Level-1 trigger is prone to network congestion since the receiving node can not handle the aggregate input data rate. However, a hardware based data scheduling mechanism, the TagNet, is introduced which avoids congestion in the system.

A 30 node prototype is presented which has been built around Linux PCs connected by an SCI network. The system is able to process data with a MHz rate. Sub-events have been chosen to be as small as 128 Byte. Data transfer has been scheduled by a basic implementation of the TagNet. The system has been used to prove basic functionality and to measure important input parameters concerning the system.

# Zusammenfassung

Trigger Systeme sind Schlüsselkomponenten in modernen Hochenergie Physik Experimenten. Gegenwärtige Experimente erzeugen Datenraten, die einige TByte/s betragen. Kein Speicher kann diese Datenmenge aufnehmen. Zweitens sind auch nicht alle Daten relevant. Nur ein kleiner Bruchteil der Ereignisse sind für das Experiment von Bedeutung. Deshalb entwickelt man Trigger Systeme. Diese reduzieren die Datenmenge, indem sie nur die relevanten Daten selektieren. Am Ende ist die Datenrate so gering, dass man auf Band schreiben kann.

Trigger Systeme sind häufig mehrstufig aufgebaut. Der Level-1 Trigger des LHCb Experiments am CERN ist die zweite Stufe eines vierstufigen Systems und hat eine Eingangsrate von 1 MHz. Die Gesammtbandbreite, die das System bereitstellen muss, beträgt voraussichtlich 4 GByte/s. Die Eingangsdaten sind verteilt und nur 128 Byte im Durchschnitt. Alle Daten, die zu einem Ereignis gehören, müssen an einen bestimmten Rechner gesendet werden.

Das System benutzt ein Hochgeschwindigkeits Netzwerk, das kommerziell erhältlich ist. Als Schnittstelle zwischen Rechner und Netzwerk ist PCI vorgesehen.

Diese Arbeit beschäftigt sich mit den Anforderungen an das Netzwerk, die erfüllt werden müssen, damit es für LHCb in Frage kommt. Auf einer Shared Memory Architektur basierend wird eine neue Art der Datenübertragung erarbeitet, die externe rekonfigurierbare Logik verwendet und sehr gut zum verschicken von kleinen Datenblöcken geeignet ist.

Basierend auf der SCI Technologie werden Tests vorgestellt, die Geschwindigkeit, Durchsatz, Latenz und Skalierbarkeit diskutieren. Die Grösse des endgültigen Systems wird anhand Simulationsdaten berechnet und eine Zeitanalyse vorgestellt.

Da ein Datenempfänger eine Eingangsbandbreite von 4 GByte/s nicht empfangen kann, muss der Datentransfer in Stufen stattfinden. Deshalb wird ein Netzwerk vorgestellt, das die Daten orchestriert, um Netzwerküberlastungen vorzubeugen.

Die erarbeiteten Konzepte werden anhand eines 30 Knoten Prototyps vorgestellt. Der Prototyp besteht aus Linux PCs, die durch ein SCI Netzwerk verbunden sind. Das System kann Datenblöcke, die nur 128 Byte gross sind, mit einer MHz Rate verarbeiten. Der Datentransfer wird durch eine vorläufige Version des Orchestrierungs Netzwerks gesteuert.

# Contents

| 1        | Intr | roduction 1                                 |

|----------|------|---------------------------------------------|

|          | 1.1  | High Energy Physics Experiments             |

|          | 1.2  | High Energy Physics at CERN                 |

|          | 1.3  | Trigger Systems                             |

|          |      | 1.3.1 The HERA-B Trigger System             |

|          |      | 1.3.2 The BaBar Trigger System              |

|          | 1.4  | Motivation of this Thesis                   |

| <b>2</b> | The  | e LHCb Experiment 9                         |

|          | 2.1  | Physics Introduction                        |

|          | 2.2  | The Large Hadron Collider                   |

|          | 2.3  | The LHCb Detector                           |

|          | 2.4  | The LHCb Trigger System                     |

| 3        | The  | e LHCb Level-1 Trigger 15                   |

|          | 3.1  | Vertex Locator                              |

|          | 3.2  | Front-End Electronics                       |

|          | 3.3  | Readout Units (RUs) and Network             |

|          | 3.4  | Track Finding Algorithm                     |

|          | 3.5  | Trigger Output                              |

| 4        | LH   | Cb Level-1 Trigger Networking 23            |

|          | 4.1  | LHCb Networking Requirements                |

|          | 4.2  | The Peripheral Component Interconnect (PCI) |

|          |      | 4.2.1 PCI Overview                          |

|          |      | 4.2.2 PCI Bus Protocol                      |

|          |      | 4.2.3 PCI Timing Diagram                    |

|          |      | 4.2.4 Interrupts                            |

|          | 4.3  | High-speed, Low Latency Interconnects       |

|          |      | 4.3.1 Scalability                           |

|          |      | 4.3.2 Input/Output Models                   |

|          |      | 4.3.3 Protocol Overhead                     |

|          |      | 4.3.4 Memory Models                         |

|          | 4.4  | The Scalable Coherent Interface (SCI)       |

|          |      | 4.4.1 Concepts of SCI                       |

|          |      | 4.4.2 SCI Logical Layer                     |

|          |      | 4.4.3 The Dolphin Implementation            |

ii CONTENTS

|   | 4.5  | Traffic Shaping and Network Congestion       | 46  |

|---|------|----------------------------------------------|-----|

| 5 | Peri | formance of the Scalable Coherent Interface  | 49  |

|   | 5.1  | Software initiated Data Transfer             | 49  |

|   |      | 5.1.1 Point-to-Point Bandwidth               | 49  |

|   |      | 5.1.2 Maximum Performance Tests              | 51  |

|   |      | 5.1.3 Synchronization by Remote Interrupts   | 55  |

|   |      | 5.1.4 Minimum Data Packet Latency            | 55  |

|   | 5.2  | Hardware initiated Data Transfer             |     |

|   | J    | 5.2.1 Increasing Performance by using FPGAs  | 58  |

|   |      | 5.2.2 Non-Interleaved Transfer Mode          | 59  |

|   |      | 5.2.3 Interleaved Transfer Mode              | 63  |

|   | 5.3  | Large SCI Ringlets                           | 64  |

| _ |      |                                              |     |

| 6 |      | el-1 Trigger General Architecture            | 65  |

|   | 6.1  | Level-1 Trigger System Architecture Overview | 65  |

|   |      | 6.1.1 Network Feeds (RUs)                    | 66  |

|   |      | 6.1.2 Compute Nodes (CNs)                    | 68  |

|   | 6.2  | Network Topology and Size                    | 69  |

|   | 6.3  | Network Traffic                              | 70  |

|   |      | 6.3.1 Routing                                | 70  |

|   |      | 6.3.2 Scheduled Data Transfer                | 70  |

|   | 6.4  | Level-1 Decision Unit Interface              | 73  |

|   | 6.5  | Timing                                       | 73  |

| 7 | The  | Level-1 Trigger Prototype                    | 77  |

|   | 7.1  | Baseline Architecture                        | 77  |

|   | 7.2  | Network Feeds                                | 79  |

|   |      | 7.2.1 Data Scheduling and TagNet Prototype   | 79  |

|   |      | 7.2.2 DMA Logic                              | 82  |

|   | 7.3  | Global Shared Memory                         | 87  |

|   | 7.4  | Data Transfer                                | 88  |

|   |      | 7.4.1 Transfer Order                         | 88  |

|   |      | 7.4.2 Data Format                            | 88  |

|   | 7.5  | Data Integrity                               | 89  |

|   | 7.6  | The Level-1 Decision Unit Interface          | 92  |

|   | 7.7  | System Performance                           | 94  |

|   | 7.8  | System Frequency                             | 95  |

|   | 7.9  | Scalability                                  | 96  |

|   |      | 7.9.1 Non-Scheduled Transfer                 | 97  |

|   |      | 7.9.2 Scheduled Transfer                     | 98  |

|   | 7.10 | B-Link Performance                           |     |

|   |      | System Latency                               |     |

|   |      | Fault Tolerance                              |     |

|   |      |                                              |     |

| 8 | Sun  | nmary and Outlook                            | 105 |

|          | ••• |

|----------|-----|

| CONTENTS | 111 |

|          |     |

| $\mathbf{A}$ | Implementation                              | 109   |

|--------------|---------------------------------------------|-------|

|              | A.1 Design Flow                             | . 109 |

|              | A.2 TagNet Implementation                   | . 109 |

|              | A.3 Virtual to Physical Address Translation | . 110 |

| В            | Contents of the CD                          | 113   |

| $\mathbf{C}$ | Glossary                                    | 115   |

| A            | cknowledgments                              | 117   |

| Bi           | bliography                                  | 119   |

| In           | dex                                         | 123   |

# List of Figures

| 1.1<br>1.2<br>1.3 | CERN as seen from above. Figure from [3]                                                                                                      | 2<br>3<br>4     |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 2.1               | Polar angles of the b- and $\overline{\text{b}}$ -hadrons calculated by the PYTHIA event generator.                                           |                 |

|                   | Figure from LHCb TP [1]                                                                                                                       | 10              |

| 2.2               | Schematic drawing of the LHCb detector as seen from above. Figure from the                                                                    |                 |

|                   | VELO TDR [8]                                                                                                                                  | 11              |

| 2.3               | LHCb trigger system stages including latencies and suppression rates                                                                          | 12              |

| 3.1               | Arrangement of the detector stations along the beam axis. The interaction region $(\pm \sigma)$ is depicted as well. Figure from VELO TDR [8] | 16              |

| 3.2               | Schematic view of a R- and $\Phi$ - measuring sensor. Figure from VELO TDR                                                                    |                 |

|                   | [8]                                                                                                                                           | 17              |

| 3.3               | Front-end electronics architecture. Figure from VELO TDR [8]                                                                                  | 17              |

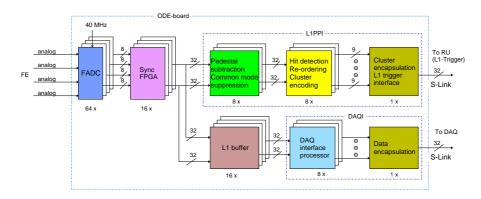

| 3.4               | Block diagram of the off detector electronics. Figure from [15]                                                                               | 18              |

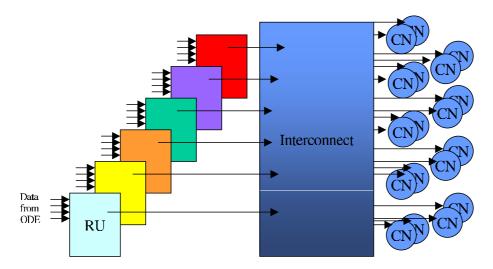

| 3.5               | Abstract view of the LHCb Level-1 Trigger                                                                                                     | 20              |

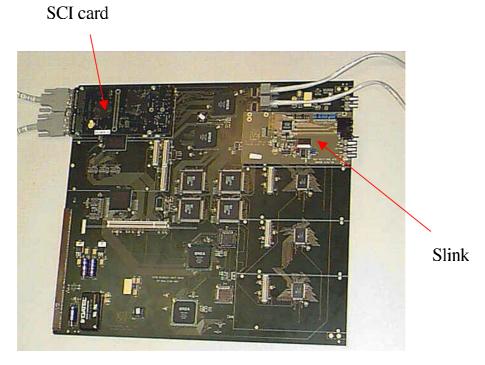

| 3.6               | RU as implemented at CERN. The on-board processor is not shown. Figure from [19]                                                              | 20              |

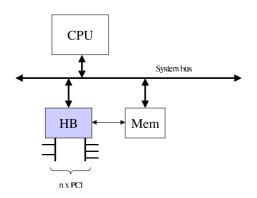

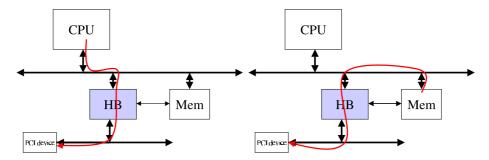

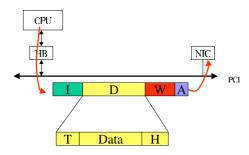

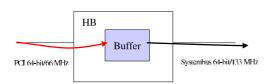

| 4.1               | Modern chipset architecture with the host bridge (HB) being the external I/O controller                                                       | 25              |

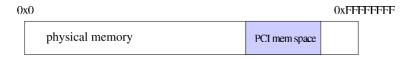

| 4.2               | Example physical address space                                                                                                                | $\frac{25}{26}$ |

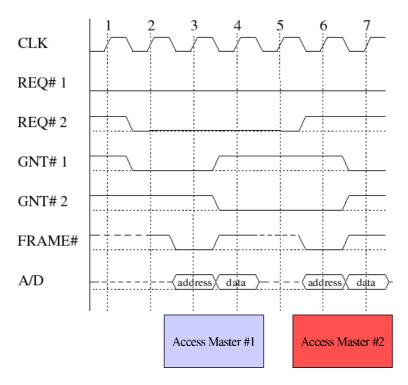

| 4.2               | PCI bus arbitration. Figure from [24]                                                                                                         | $\frac{20}{28}$ |

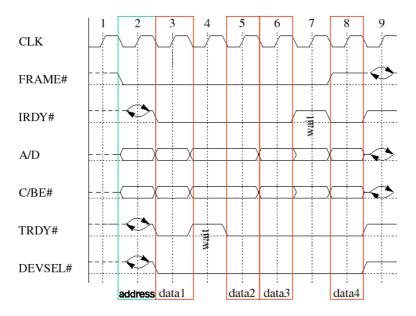

| 4.4               | PCI write transaction. Figure from [24]                                                                                                       | 29              |

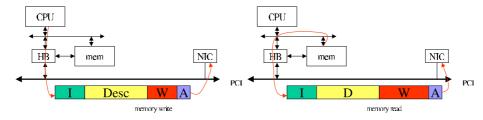

| 4.5               | Left: Data path for programmed I/O. Right: Data path for DMA                                                                                  | $\frac{23}{31}$ |

| 4.6               | Overhead PIO mode. The CPU is sending data to the NIC                                                                                         | 33              |

| 4.7               | Overhead DMA mode. Left: Setup of the DMA controller. The CPU is sending a                                                                    | 00              |

| 1.1               | DMA descriptor to the NIC. Right: The NIC fetches data out of memory which                                                                    |                 |

|                   | implies more wait cycles on the PCI bus than in case of writing to memory                                                                     | 33              |

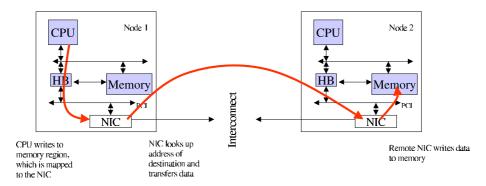

| 4.8               | Write operation to a remote memory region                                                                                                     | 34              |

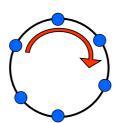

| 4.9               | SCI topologies                                                                                                                                | 35              |

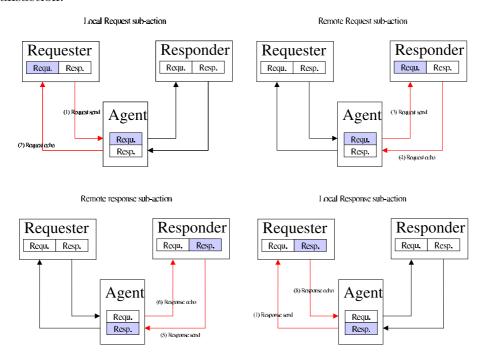

| 4.10              | SCI transaction phases.                                                                                                                       | 37              |

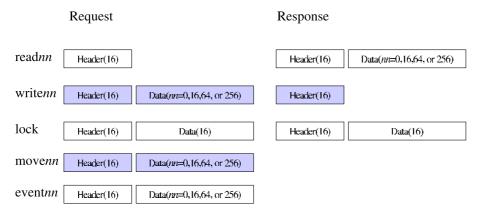

| 4.11              | Transaction types.                                                                                                                            | 38              |

| 4.12              |                                                                                                                                               | 39              |

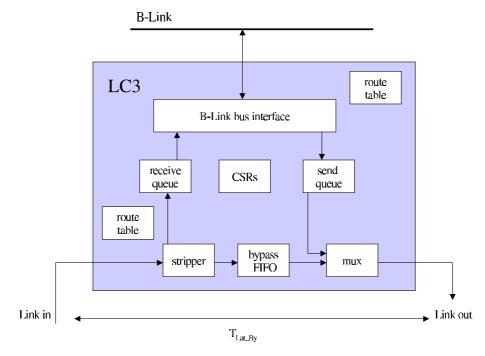

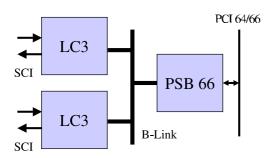

|                   | Block diagram of the link controller chip LC3                                                                                                 | 41              |

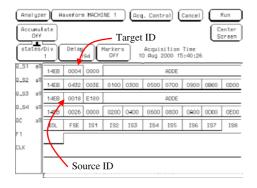

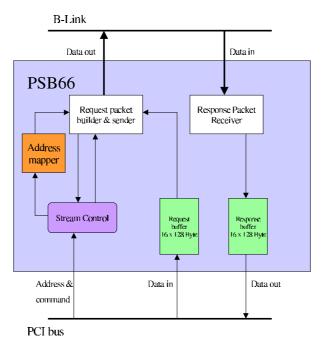

|                   | SCI trace of a request-send packet                                                                                                            | 42              |

|                   | Simplified block diagram of the Dolphin PSB66.                                                                                                | 43              |

vi LIST OF FIGURES

| 4.16 | Block diagram of the Dolphin SCI card. In the sketch two LC3s are connected by the B-Link bus which allows a two-dimensional topology                                                                                                                                                                                       | 45 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

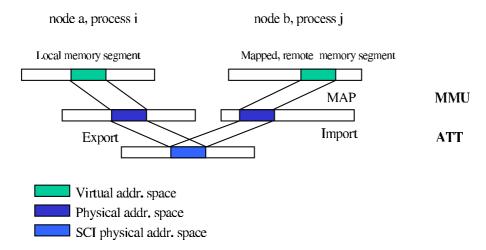

| 4.17 | Address spaces and address translations in SCI clusters                                                                                                                                                                                                                                                                     | 45 |

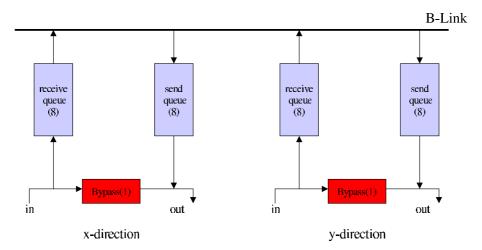

| 4.18 | Packet buffers in SCI cards                                                                                                                                                                                                                                                                                                 | 46 |

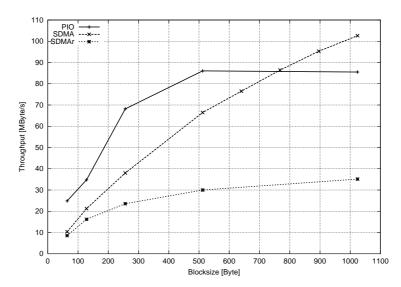

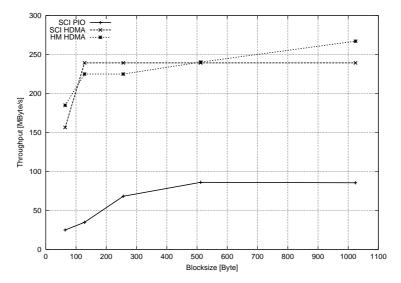

| 5.1  | The point-to-point bandwidth results obtained with PIO and SDMA for block sizes less than 1024 byte                                                                                                                                                                                                                         | 50 |

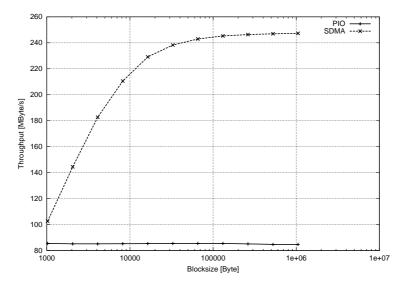

| 5.2  | The point-to-point bandwidth results obtained with PIO and SDMA for block sizes between 1024 byte and 1 MByte on a logarithmic scale                                                                                                                                                                                        | 51 |

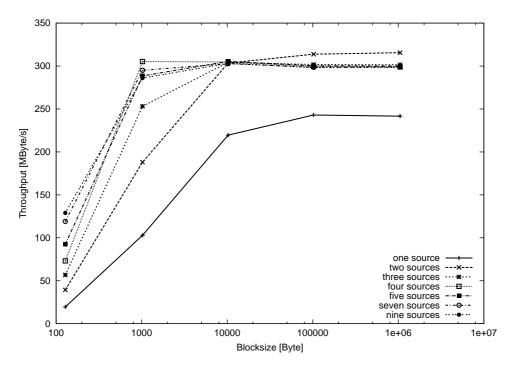

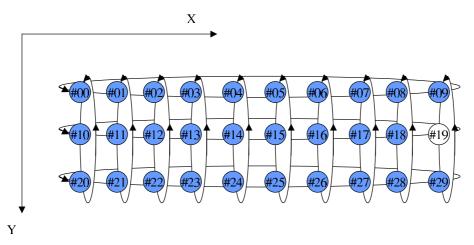

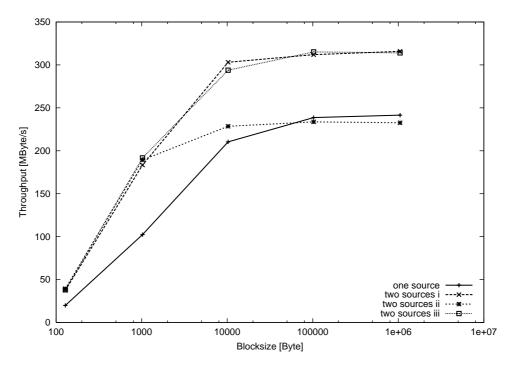

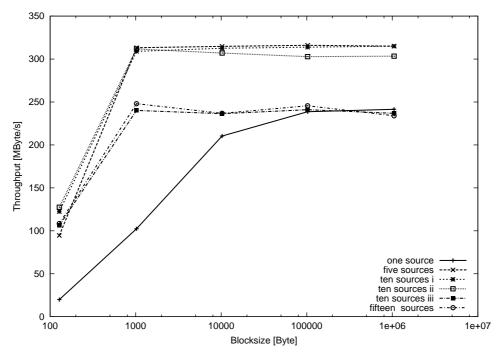

| 5.3  | Performance measured on the receiving node with different numbers of data sources                                                                                                                                                                                                                                           | 52 |

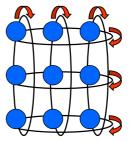

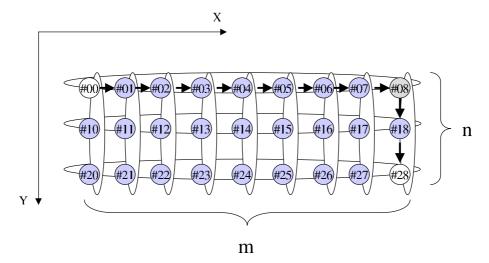

| 5.4  | 2D-torus as used for the benchmark tests presented. Always the same node has been used as receiver. It is depicted as a blanc circle. Direction of SCI data packets                                                                                                                                                         |    |

|      | is depicted by the arrows.                                                                                                                                                                                                                                                                                                  | 53 |

| 5.5  | Maximum performance measured on node #19, the receiving node, with one data sources and two data sources                                                                                                                                                                                                                    | 53 |

| 5.6  | Maximum performance measured on node #19 with a variable number of data sources                                                                                                                                                                                                                                             | 54 |

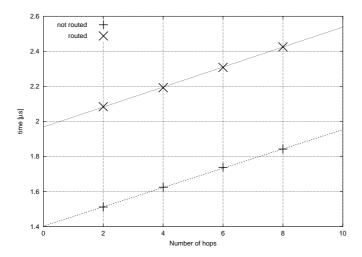

| 5.7  | PCI-to-PCI latency measured as explained in the text. Paths, which include route nodes are labeled routed data                                                                                                                                                                                                              | 56 |

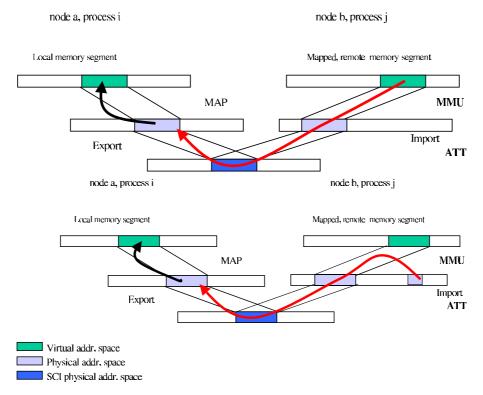

| 5.8  | Longest data path in a $9 \times 3$ torus. Data is sent from node #00 to node #28 via route node #08. The arrows depict the flow of the SCI data packet                                                                                                                                                                     | 57 |

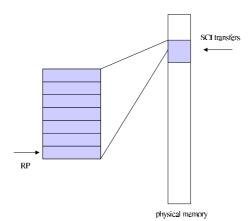

| 5.9  | Data transfer using HDMA (bottom) compared to common transfer (top). Local and remote physical memory regions are of equal size. The size of the physical memory region associated with the HDMA engine which is depicted on the right of the bottom figure is not important for the data transfer since it is only used to |    |

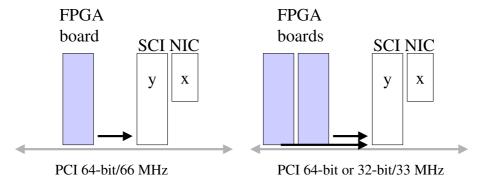

| 5.10 | configure the HDMA engine via PCI                                                                                                                                                                                                                                                                                           | 58 |

| 0.20 | dem mode operation solution on the right side                                                                                                                                                                                                                                                                               | 59 |

| 5.11 | FPGA initiated transfer vs. PIO for block sizes less than 1024 Byte as measured in a point-to-point connection. The different curves are explained in the text                                                                                                                                                              | 60 |

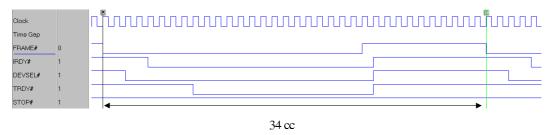

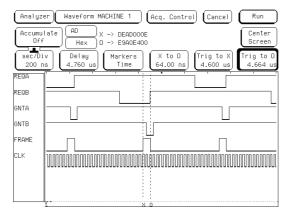

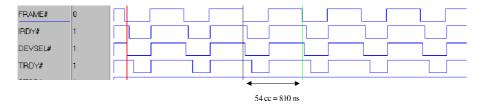

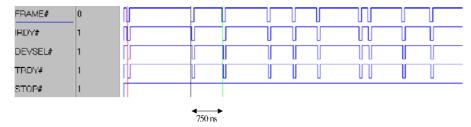

| 5.12 | PCI trace of a 128 Byte HDMA transfer as seen on a 64-bit/66 MHz bus. The total transaction time equals 34 clock cycles                                                                                                                                                                                                     | 60 |

| 5.13 | Sketch of the PCI cycles of a DMA transfer as seen on a 64-bit/66 MHz bus. The cycles can also be seen on the PCI trace in figure $5.12$                                                                                                                                                                                    | 61 |

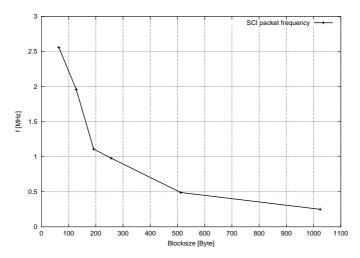

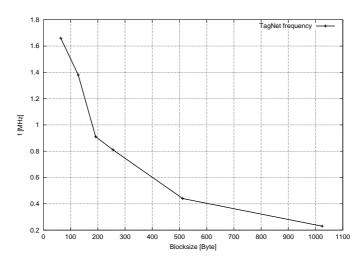

| 5.14 | Packet frequency in MHz as measured for block sizes less than 1024 Byte on the sending node                                                                                                                                                                                                                                 | 61 |

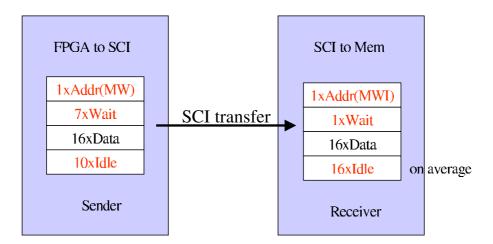

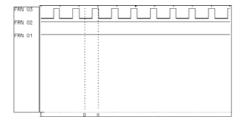

| 5.15 | Sketch of PCI cycles as measured on receiving and sending node of an 128 Byte SCI transaction                                                                                                                                                                                                                               | 62 |

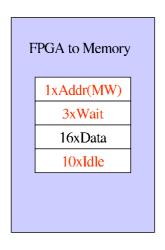

| 5.16 | Sketch of PCI cycles of a 128 Byte transaction into local memory                                                                                                                                                                                                                                                            | 62 |

|      | The hostbridge buffers the incoming data such that it can issue a burst on the system bus                                                                                                                                                                                                                                   | 63 |

| 5.18 | PCI trace of an interleaved transaction. The idle time in between bursts is reduced to a minimum of 1 clock cycle                                                                                                                                                                                                           | 63 |

| 5.19 | PCI cycles for one DMA transfer as seen on a 32-bit/33 MHz bus using the PCI 64/33 SCI card.                                                                                                                                                                                                                                | 64 |

LIST OF FIGURES vii

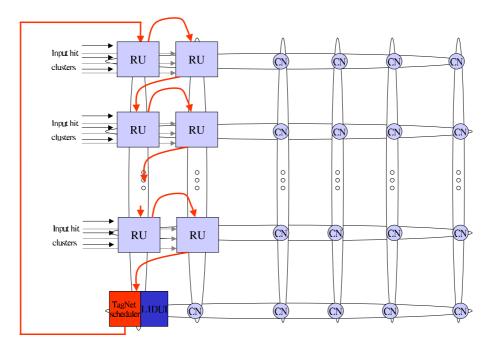

| 6.1 | The Level-1 architecture as discussed in this chapter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 66       |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

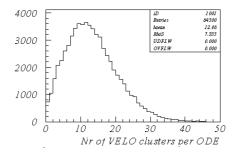

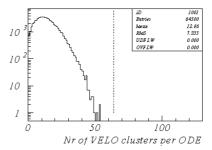

| 6.2 | Number of VELO clusters per ODE (13 on average). Minimum bias events with Level-0 decision applied have been used as input data for simulation. Noise is not                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | C        |

|     | included. Data has been taken from [42]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 67       |

| 6.3 | Number of VELO clusters per event (1286 on average). Noise is not included. Data has been taken from [42].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 67       |

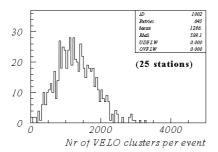

| 6.4 | Left: Processing time for 2D track search vs. number of R clusters for $B \to \pi^+\pi^-$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |

|     | Right: Time for full tracking. The plots have been taken from [45]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 68       |

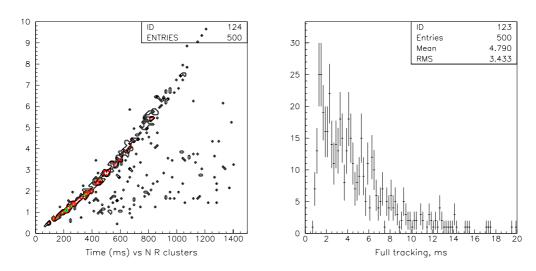

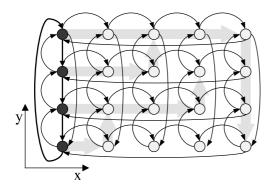

| 6.5 | Dimensional routing in a $5 \times 4$ torus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 70       |

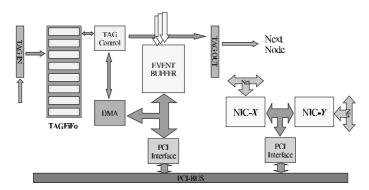

| 6.6 | Under the control of the TagNet data is moved by a DMA engine from the event buffers to the SCI NIC card without CPU intervention                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 71       |

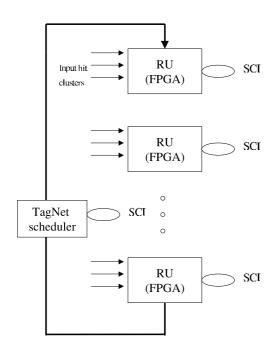

| 6.7 | The TagNet connecting the RUs and the TagNet Scheduler. Both TagNet slave and TagNet scheduler logic is implemented in FPGAs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 72       |

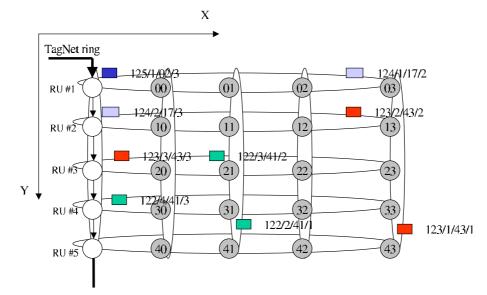

| 6.8 | Several fractions of a few events moving through a part of the torus. Data belonging to the same event is depicted in the same color. The packets are tagged by event/RU/Dest/timestep giving the ID, source RU, destination node and the time                                                                                                                                                                                                                                                                                                                                                                                                     |          |

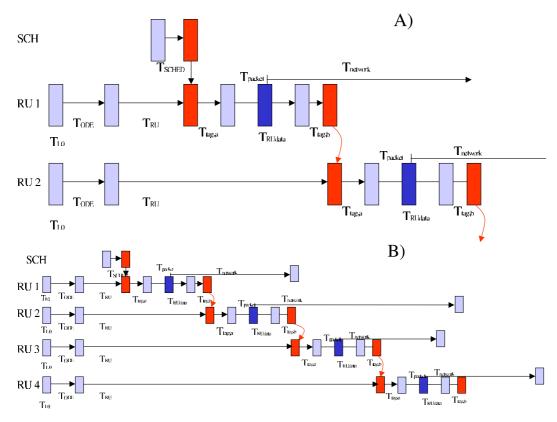

| 6.9 | step at which they have entered the network. The scheduler is not shown A) The sequence of certain operations during the transport phase for the first 2 RUs. Deviating from the text $T_{RUdata}$ has been split into the time to transport the first packet $(T_{packet})$ and the remaining time. $T_{tag}$ is divided into two parts, $T_{taga}$ for decoding the tag and setting up the remote DMA transfer and $T_{tagb}$ for forwarding the tag. B) Looking at the emerging pattern for 4 RUs the accumulation of the non-overlapping components becomes clear. Since order of delivery is not guaranteed packets might overtake each other | 72<br>74 |

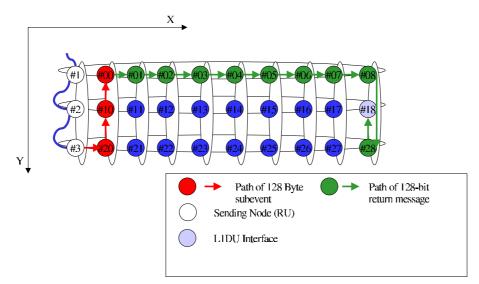

| 7.1 | 30 nodes out of 32 Linux computers are connected to a $10 \times 3$ torus. The picture on the right shows the SCI cabling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 78       |

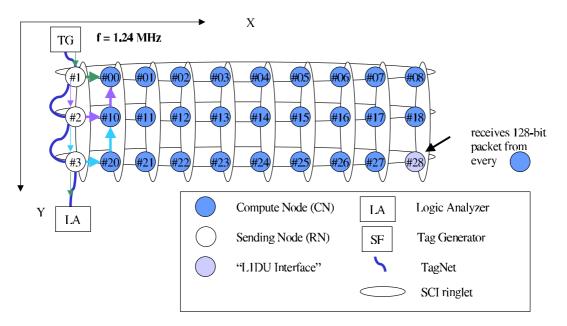

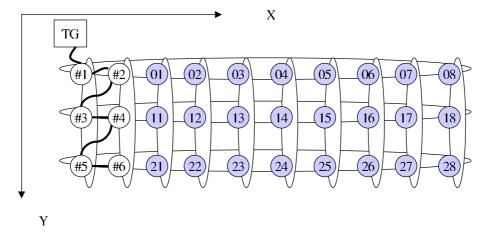

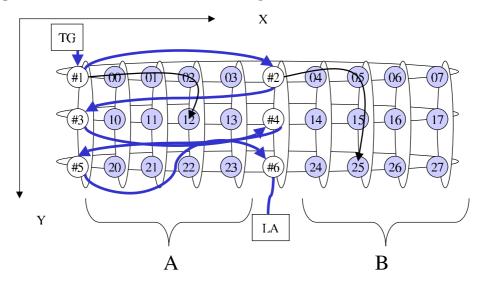

| 7.2 | This figure shows the current setup in Heidelberg. 30 nodes are connected by the Scalable Coherent Interface and form a two-dimensional torus topology. The three nodes to the left are mockup input feeds connected by a basic implementation of the scheduling network TagNet. The node labeled L1DU Interface receives 128-bit                                                                                                                                                                                                                                                                                                                  |          |

|     | result messages from every compute node                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 79       |

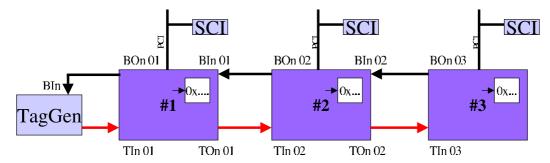

| 7.3 | The picture shows the setup for a mockup RU as used in the system presented                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 80       |

| 7.4 | The three sending nodes (RUs) also depicted on the left in figure 7.2 are connected by the TagNet links. The node numbers refer to the numbers introduced in figure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

|     | 7.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 81       |

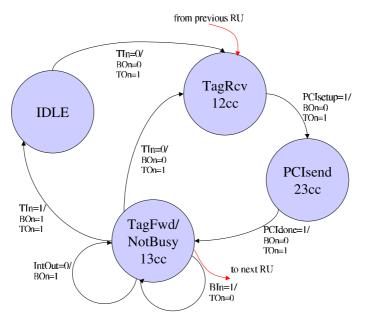

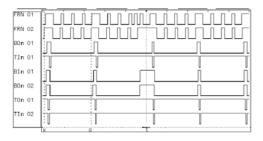

| 7.5 | Finite state machine of the TagNet logic. Using the terms introduced in 6.5, $T_{taga}$ accounts to 12 clock cycles and $T_{tagb}$ to 13 clock cycles. The time spent in the PCIsend state is identical to $T_{RUdata}$ with its duration being defined by the assertion period of the PCI FRAME# signal. Only when the internal output buffer is empty (IntOut=0) the BOn signal is deasserted, thus avoiding buffer overflow.                                                                                                                                                                                                                    | 81       |

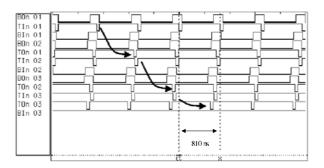

| 7.6 | This logic analyzer screen shot shows the tag flow as measured with three RUs. The first RU receives a tag (TIn 01), asserts its busy signal (BOn 01) during an ongoing transfer, and forwards the tag to the adjacent node (TOn 01) after the PCI transaction has been finished. The nodes are connected as depicted in figure 7.4                                                                                                                                                                                                                                                                                                                | 82       |

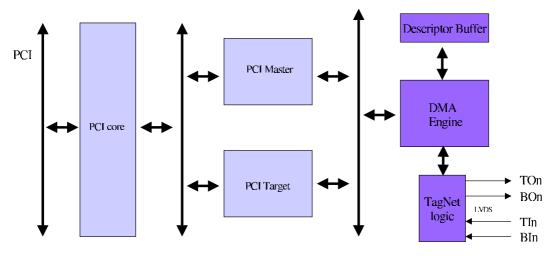

| 7.7 | Schematic of DMA logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

viii LIST OF FIGURES

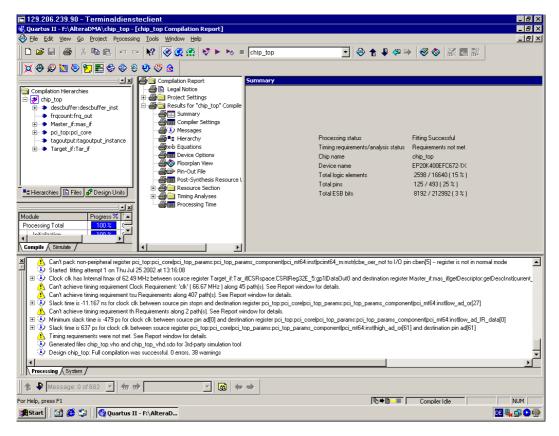

| 7.8  | Output of the design software as provided by Altera. It reveals that only 15% of the logic is used | 83       |

|------|----------------------------------------------------------------------------------------------------|----------|

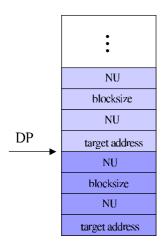

| 7.9  | Layout of the descriptor buffer. Up to 64 different descriptors can be stored at                   | 06       |

| 1.0  | this point which is sufficient for the current system size. After each transfer the                |          |

|      | - · · · · · · · · · · · · · · · · · · ·                                                            | 84       |

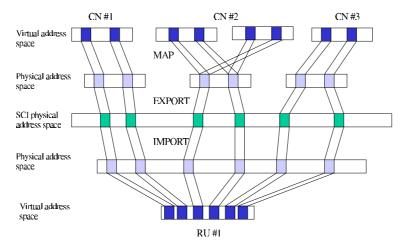

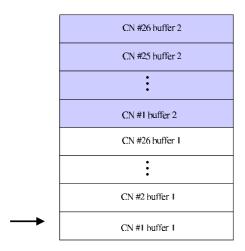

| 7.10 | Every single compute node can export $m$ chunks of memory. The figure shows three                  | _        |

|      | compute nodes exporting two memory regions each as an example. Afterwards                          |          |

|      | the RUs import all exported regions. CN #2 runs two processes which map the                        |          |

|      | memory regions into their virtual address space to have access to data sent via SCI.               | 87       |

| 7.11 | During the initialization phase every RU imports the memory regions exported by                    |          |

|      | the compute nodes. This is done by software and results in 52 virtual addresses                    |          |

|      | when 26 CNs export two memory regions each. After those addresses have been                        |          |

|      | translated to physical addresses they are transferred to the DMA engines' descrip-                 |          |

|      | tor buffer located in the FPGA. The figure shows a snapshot of some descriptor                     |          |

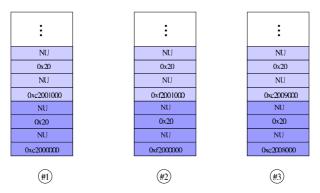

|      | buffer entries after initialization. Descriptor entries labeled NU are not in use. $$ . $$ .       | 88       |

| 7.12 | Since no scheduler has been implemented so far the order in which remote nodes                     |          |

|      | are accessed is set by the order of descriptors. The figure shows the descriptor                   |          |

|      | order in a buffer. The read pointer is depicted to the left. It is incremented every               |          |

| 7 10 |                                                                                                    | 89       |

| 7.13 | A 64-bit mockup data word as transferred every PCI data cycle. The least signif-                   | 00       |

| 714  |                                                                                                    | 89<br>90 |

|      | Flow diagram of the algorithm checking the incoming data packets                                   | 90       |

| 1.10 | ~ · · · · · · · · · · · · · · · · · · ·                                                            | 91       |

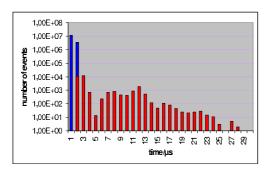

| 7.16 | A time histogram shows that in 76% of all loops the event data is successfully                     | J        |

| 1.10 | checked within $1\mu s$ . After $2\mu s$ 99.87% of all data is checked successfully. The part      |          |

|      |                                                                                                    | 92       |

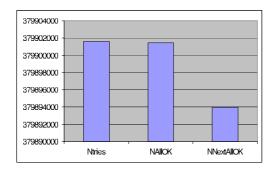

| 7.17 | 2 0 0                                                                                              | 93       |

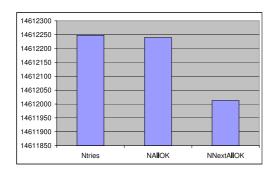

|      | The Level-1 Decision Unit Interface collects data coming from 26 CNs and calcu-                    |          |

|      | lates some statistics. All nodes executed a total of 379901605 loops, verified almost              |          |

|      | 100% of all data as valid and the next in line                                                     | 93       |

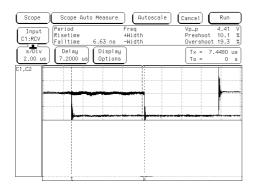

| 7.19 | The figure shows a PCI trace of 128 Byte bursts in one of the sending nodes. The                   |          |

|      | send frequency in the trace is 1.24 MHz                                                            | 94       |

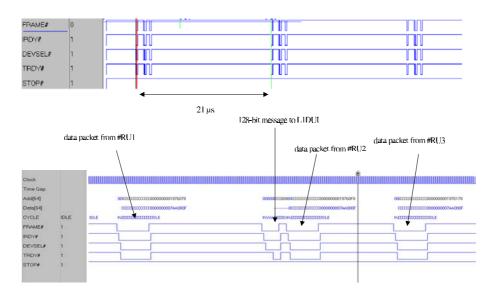

| 7.20 | The figure shows a PCI trace in one of the receiving nodes. The trace shows a                      |          |

|      | setup for N = 26 resulting in $T_{idle} = 21 \mu s$ on the top PCI trace. The bottom               |          |

|      | measurement shows a zoomed PCI trace, which shows the data packets coming                          |          |

|      | from the different RUs and the 128-bit result message sent to the Level-1 Decision                 | 0.5      |

| 7.01 |                                                                                                    | 95       |

| 1.21 | The figure shows a PCI trace in the Level-1 Decision Unit Interface. The PCI                       | 95       |

| 7 22 | traffic shows asynchronous behavior                                                                | 90       |

| 1.44 | The time periods measured differ by 14 clock cycles compared to the data presented                 |          |

|      | - · · · · · · · · · · · · · · · · · · ·                                                            | 96       |

| 7.23 | One RU sends 128 Byte of data with the maximum frequency of 1.96 MHz. The                          |          |

| 3    | - · ·                                                                                              | 97       |

| 7.24 | Two RU try to send 128 Byte of data with the maximum frequency of 1.96 Mhz                         |          |

|      | · · · · · · · · · · · · · · · · · · ·                                                              | 97       |

LIST OF FIGURES ix

| 7.25 | After the third RU starts sending the data rate on two RUs drops significantly    | . 97  |

|------|-----------------------------------------------------------------------------------|-------|

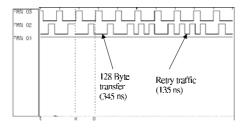

| 7.26 | Two RUs share a horizontal ringlet and try to send with 128 Byte of data with a   |       |

|      | rate close to 2 MHz. The PCI FRAME# signal is analyzed and shows retry traffic    |       |

|      | for the RU presented by FRN 02. However, aggregate maximum transfer rates of      |       |

|      | up to 478 MByte/s payload can be observed                                         | . 98  |

| 7.27 | Two RUs share a horizontal ringlet and are connected by the TagNet. The SCI       |       |

|      | cabling is chosen such that packets sent by RU#2 have to traverse the bypass FIFO |       |

|      | of RU#1                                                                           | . 98  |

| 7.28 | Retry traffic caused by bypass traffic. RU#1 has to issue retries which is due to |       |

| ,    | bypass traffic originating from RU#2                                              | . 99  |

| 7.29 | No retry traffic can be observed by adjusting the bypass traffic frequency. The   |       |

| 1.20 | sustained bandwidth accounts to 432 MByte/s                                       | . 99  |

| 7 30 | Displacing the RUs minimizes SCI bypass buffer occupancy on the node further      | . 00  |

| 1.00 | downstream. The direction of request-send packets is depicted by two example      |       |

|      | transfers                                                                         | . 99  |

| 7.31 |                                                                                   | . 33  |

| 1.51 | width measured is 478 MByte/s whereas the average bandwidth over a long time      |       |

|      | interval is 472 MByte/s which is due to the overhead implied by the TagNet imple- |       |

|      | mentation. The block size has been set to 4096 Byte with the network load being   |       |

|      | · · · · · · · · · · · · · · · · · · ·                                             | 100   |

| 7 22 | balanced                                                                          | . 100 |

| 1.52 | Two RUs being displaced send into the same partition. The trace shows retry       | 100   |

| 7 22 | traffic at a total bandwidth of 453 MByte/s and a block size of 512 Byte          | . 100 |

| 7.33 | y i                                                                               |       |

|      | can be observed. The aggregate bandwidth is 453 MByte/s with the block size       | 101   |

| 7.04 | being 512 Byte                                                                    | . 101 |

| 7.34 | Aggregate bandwidth for two CNs in a ringlet. The maximum bandwidth achieved      |       |

|      | is 478 MByte/s. The measurement has been taking on the receiving sides. The       |       |

|      | aggregate data packet frequency is 3.92 MHz with the data size being 128 Byte.    |       |

|      | Sending nodes are CN 01 and CN 02 whereas CN 04 and CN 05 are receivers (see      |       |

|      | figure 7.27)                                                                      | . 101 |

| 7.35 |                                                                                   |       |

|      | route node. The maximum bandwidth observed has been 450 MByte/s. Sending          |       |

|      | nodes are CN 01 and CN 02 whereas CN 13 and CN 23 are receivers (see figure       |       |

|      | 7.27)                                                                             |       |

|      | Packet path for system latency measurements                                       |       |

| 7.37 | Latency as measured with two PCI tracers                                          | . 103 |

| Λ 1  | Flat ribbon cables have been used to connect the boards                           | 110   |

| A.1  | Flat Hodon capies have been used to connect the boards                            | . 110 |

# List of Tables

| 4.1 | LC3 packet types as described in [31]                                  | 42  |

|-----|------------------------------------------------------------------------|-----|

| 5.1 | Average synchronization time in busy and idle mode                     | 55  |

| 5.2 | Line parameters for the fit lines shown in figure 5.7. The parameter x |     |

|     | denotes the number of hops                                             | 56  |

| 5.3 | Results of Packet Latency measurements as shown in figure 5.7          | 56  |

| 7.1 | TagNet signals, direction, and meaning                                 | 80  |

| 7.2 | Address space of DMA logic                                             | 85  |

| 7.3 | 128-bit message sent to the Level-1 Decision Unit Interface            | 92  |

| 7.4 | System Latency for the setup shown in figure 7.36                      | 103 |

| A.1 | Assignment of the RX and TX channels                                   | 110 |

# Chapter 1

# Introduction

Trigger systems are widely used in high energy physics experiments to reduce the tremendous amount of data by event selection and filtering in real-time. Taking the LHCb experiment as an example,  $10^{12}$   $b\bar{b}$  pairs are created in one year. The total number of interactions can be calculated to be  $4\times10^{14}$ . However, due to the small branching ratios for interesting B decays of  $10^{-5}$  or less and the limited detector acceptance the events that contain valuable physics information have to be extracted. This happens by pipelined trigger systems. The first trigger stage selects events based on part of the event data. All subsequent trigger stages take those events and apply different, specialized algorithms to reduce background events.

This thesis describes the requirements of the LHCb Level-1 trigger, the second of four trigger stages. A networked cluster of PCs is used to run the trigger algorithm. The farm has to process one event every microsecond with the total bandwidth required being about 4 GByte/s.

## 1.1 High Energy Physics Experiments

Accelerator experiments in high energy physics are characterized by interaction of particles, particle production, and particle decay. Production and decay have different probabilities which are described by Quantum Mechanics and observed in particle detectors.

Taking the LHCb experiment as an example, protons collide with a frequency of 40 MHz. The interaction point, the primary vertex, can be measured with a resolution of  $49\mu m$  along the beam axis using a silicon vertex detector. The experiment is intended to measure decay probabilities of B-mesons. Those particles decay a few mm apart, at the secondary vertex, and are measured with a resolution of  $225\mu m$  along the beam axis. About  $10^{12}$   $b\bar{b}$  pairs are expected in one year of data taking  $(10^7 s)$  [1]. However, due to limited detector acceptance and small branching ratios of the order of  $10^{-5}$  or less, only a small fraction of events are stored for offline analysis. The LHCb trigger system will select and filter this fraction of interesting events from the large number of events producing b quarks and other pp events in real-time.

#### 1.2 High Energy Physics at CERN

CERN is the Organization for Nuclear Research and the world's largest particle physics center. The word "CERN" is a French abbreviation and stands for "Convention Européene de la Recherche Nucléaire". CERN has been founded in 1954 being one of the first European joint ventures. From the original 12 signatories to the CERN convention, membership has grown to 20. More than 6500 scientists, which amounts to more than half of the world's particle physicists, come to CERN doing their research. 500 universities and over 80 nationalities are represented. One of the collaborating institutes is the "Kirchhoff-Insitut für Physik" in Heidelberg, Germany. Its responsibility is, among others, to build a small, but important part for one of the upcoming accelerator experiments the Level-1 trigger for the LHCb experiment.

However, the challenge imposed by the experiments is not only an attracting place for particle physicists. Computer scientists and engineers from around the world contribute to the electronics and computer systems required by the experiments to handle the huge amount of data. Sometimes even every days life is affected by results achieved by the people working at CERN. The most famous example is certainly the invention of the World Wide Web by Tim Berners-Lee in 1989. The original proposal can be found under [2].

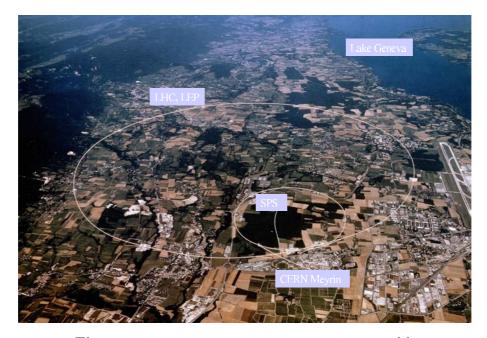

Currently a new accelerator, the LHC<sup>1</sup>, is installed in the place of the LEP<sup>2</sup>. Figure 1.1 shows an aerial view of the area. The large circle demonstrates the path which accelerated particles will take. Its circumference is about 27 km. CERN is located close to Geneva in Switzerland. However, more than half of the area covered by the accelerator ring is located in France.

Figure 1.1: CERN as seen from above. Figure from [3].

<sup>&</sup>lt;sup>1</sup>LHC: Large Hadron Collider.

<sup>&</sup>lt;sup>2</sup>Large Electron Positron Collider

Originally the LHC experiments have been scheduled to take their first data in the year 2005. However, because of delays the experiments will start in the year 2007.

Four new LHC experiments, each having its own detector, are currently under construction:

- **ALICE**: The aim is to study the physics of strongly interacting matter at extreme energy densities, where the formation of a new phase of matter, the quark-gluon plasma, is expected.

- ATLAS: A general purpose experiment having the main effort to discover the Higgs particle<sup>3</sup>.

- CMS: A general purpose experiment looking into physics beyond the Standard Model and into discovery of the Higgs.

- LHCb: Precision Measurements of CP violation and rare decays.

Figure 1.2 shows the location of the four LHC experiments. All detectors are located about 100 m underneath the surface. The LHCb experiment, which is the one of interest in this thesis, is depicted on the right bottom.

# Cleaning Tile Injection Future constructions Existing underground buildings

#### Layout of the LEP tunnel including future LHC infrastructures.

Figure 1.2: Location of LHC experiments. Figure from [3].

## 1.3 Trigger Systems

The data rate of nowadays experiments is in the TByte/s range exceeding the capabilities of storage systems today and in the foreseeable future. Secondly, but even more impor-

<sup>&</sup>lt;sup>3</sup>The Higgs Particle or Higgs Boson is associated to the origin of mass.

tant, not all data are of interest for physics offline analysis. Therefore, the data has to be analyzed and successively reduced in real-time. Events that are valuable for physics analysis are kept whilst events which are not relevant are discarded. However, this makes the trigger system to the most crucial part in the experiment since any failure results in loss of valuable physics data or even in wrong interpretation of results. Triggering is commonly done by pipelined systems. Usually systems like that have three or four pipeline stages.

The first stage in the system selects events by analyzing a part of the total data stream coming from the detector. Only events that have been selected are analyzed by the other trigger stages. The following trigger stages reject those remaining events based on a filtering algorithm looking for specific characteristics. Therefore, the data rate is successively reduced such that final storage on tape is feasible. The last trigger stage usually analyzes all data associated with an event while the other stages deal with a subset. Every pipeline stage applies the same principle; data are kept in a buffer and a copy or subset of it are analyzed by the trigger logic. However, since buffers are not of infinite size a trigger decision has to be made in time to avoid a buffer overflow. Thus, the trigger decision has to be broadcast within a certain latency window.

Trigger logic can be implemented either in hardware or software. Software solutions are often desired to stay flexible during the runtime of the experiment. However, software is usually not feasible for front-end trigger stages since the latency requirements can not be met.

Upon a positive trigger decision the buffered data are forwarded to the next trigger stage. Since a large fraction is rejected both the overall amount of data and the data rate are reduced such that storage on tape for final analysis is feasible.

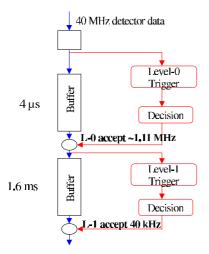

Figure 1.3 shows how data are successively reduced by the LHCb Level-0 and Level-1 trigger systems by applying the principle explained above.

**Figure 1.3:** Sample trigger logic and buffering scheme.

Taking the LHCb experiment as an example the suppression factor of the first trigger stage, the Level-0, is 40, reducing the event rate from 40 MHz to 1 Mhz. During analysis the Level-0 input data is kept in a buffer. However, the maximum latency is  $4\mu s$ . After a Level-0 accept the accepted events are analyzed by the Level-1 trigger which accepts events at 40 kHz. The data are buffered for 1.6 ms which is the total time that can be used by

hardware and software being in the Level-1 latency path. Therefore, two important tasks have to be fulfilled when designing a trigger stage:

- The hardware, e.g. networks, busses, have to cope with the data rate.

- The overall latency requirements have to be met.

The LHCb experiment will look at certain asymmetries in the decay of the B-meson. However, similar experiments are running at the moment. Before the LHCb trigger system is introduced in chapter 2 the trigger systems of the high energy physics experiments HERA-B [4] at DESY<sup>4</sup>, and BaBar [5] at SLAC<sup>5</sup> are described briefly.

#### 1.3.1 The HERA-B Trigger System

The HERA-B trigger system comprises four trigger stages which successively reduce the input rate and look for physics information. However, there is also a pre-trigger stage involved that does not reduce the data rate but rather chooses a region of interest.

The following stages are involved:

- The Level-1 Trigger (First Level Trigger, FLT) consists of a network of roughly 100 custom-built massively parallel and pipelined processors. It receives the initial detector data at a rate of 10 MHz and must deliver a suppression of 200 with a latency of  $12\mu s$ .

- The Level-2 Trigger (Second Level Trigger, SLT) handles an input rate of 50 kHz. It is a software based trigger running on a compute farm of 240 Linux PCs. It reaches a suppression factor of 100, which results in an output rate of 500 Hz. The average processing time is about 4 ms.

- The Level-3 Trigger (Third Level Trigger, TLT) is executed on the same compute farm and reduces the rate by a factor of 10. It is the first trigger stage that has access to all event data whilst the FLT and SLT see only part of the entire data stream. The latency has been set to 100 ms.

- The Level-4 Trigger (Fourth Level Trigger, 4LT) is implemented on a different compute farm using 200 CPUs. The data rate is reduced by a factor of 2.5 before data is stored on magnetic tape.

#### 1.3.2 The BaBar Trigger System

The BaBar trigger is a two-level hierarchy trigger. The Level-1 trigger has been implemented in hardware whilst the Level-3 trigger is a software approach:

• The Level-1 trigger is configured to have an output rate of less than 2 kHz with triggers typically produced within  $11 - 12\mu s$ . The trigger data are processed by three specialized hardware processors.

<sup>&</sup>lt;sup>4</sup>DESY: Deutsches Elektronen Synchrotron located in Hamburg, Germany.

<sup>&</sup>lt;sup>5</sup>SLAC: Stanford Linear Accelerator Center located at Stanford University n Menlo Park, CA.

• The Level-3 trigger is running on an online computer farm with access to the complete event data. The output rate of the Level-3 trigger has been set to less than 100 Hz. There is no Level-2 trigger involved in data analysis.

#### 1.4 Motivation of this Thesis

This thesis describes the requirements of the LHCb Level-1 trigger and the work that has been done to build a first prototype. The Level-1 trigger is the second of four trigger stages and has been planned as a software trigger to stay flexible during the runtime of the experiment. Usually experiments like this run for about 15 years.

The trigger receives a new event being more than 4 kByte in size every microsecond. Therefore, the trigger system requires a sophisticated network solution. A second boundary condition that has been set on the trigger stage is a tight latency requirement. In 1999 the latency had been agreed to be  $256\mu s$ . However, since events are queued both at the input stage and the processor the latency has been increased to 1.6 ms in 2001.

A software based trigger could be built around processors that compute a trigger result in parallel. However, additional communication overhead as imposed by MPI<sup>6</sup>, e.g., suggests to favor a single processor solution. Therefore, the trigger is planned as a cluster of PCs with each CPU running a process that analyzes one complete event. However, delay in data analysis must be avoided. Delay of data analysis of one microsecond means one additional CPU and thus additional cost of 3k Euro. Upon completion of analysis a result message is sent to a central trigger supervisor.

The incoming event is initially scattered amongst some input feeds with the fragment size being not more than 200 Byte<sup>7</sup> on average. All fragments have to be delivered to a specific compute node. Upon arrival of the complete event the software starts to process the data. Since the total input data stream equals 4 GByte/s, the data must be scheduled since the receiving node can not handle incoming data at such rate.

The requirements on the trigger can be summarized as follows:

- A system has to be built that allows transmission of event fragments with a MHz rate. Since event fragments are small this part has been considered as the most crucial part of the system.

- Event fragments have to reach a specific target without causing network congestion.

- The system should use standard components whenever possible. The amount of custom built electronics should be minimized.

- The trigger issues an output message in chronological order with a MHz rate.

The network under investigation is a shared memory based solution, which can transfer messages without any software overhead; the Scalable Coherent Interface (SCI). However, to satisfy the MHz requirement of the LHCb Level-1 trigger a method which has been named hardware initiated DMA (HDMA) has been invented. HDMA uses an external

<sup>&</sup>lt;sup>6</sup>Message Passing Interface

<sup>&</sup>lt;sup>7</sup>This number has been used as assumption in 1999.

DMA engine, which is located on the same PCI bus, to push data into a shared memory region. This transfer scheme is also called device-to-device copy. Therefore, DMA logic has been implemented in an FPGA with PCI interface. The first FPGA that has been used was an ORCA<sup>8</sup> chip by Lucent [6]. Results looked very promising when ORCA FPGAs were used in tandem mode as explained in 5.2.3. However, when modern motherboards providing a 66 MHz/64-bit PCI bus arrived on the market using the ORCA chips was not making sense anymore since the internal logic could not be clocked at 66 MHz. Another drawback was the internal 32-bit data bus of the ORCA chip feeding the external 64-bit PCI bus. Thus, everything had to be transferred to faster FPGAs. It has been decided to use Altera APEX<sup>9</sup> devices. The vast majority of the results in this thesis is based on Altera chips.

<sup>&</sup>lt;sup>8</sup>OR3TP12 FPSC

<sup>&</sup>lt;sup>9</sup>APEX20KE

## Chapter 2

# The LHCb Experiment

The LHCb experiment studies CP violation on neutral B-mesons. A spectrometer is used to detect particle tracks. To get the best possible physics performance, it covers low polar angles up to 300 mrad. The detector reconstructs B-decay vertices with a resolution being in the micrometer range. Different sub-detectors provide particle information which is analyzed by the trigger system. The four stage pipelined trigger successively reduces the data rate from 40 MHz to 200 Hz such that it can be written on tape for offline analysis.

#### 2.1 Physics Introduction

The LHCb experiment is dedicated to the study of CP violation in hadronic systems which originate from b-quarks. CP violation can be observed in decay asymmetries of the neutral B-meson. CP violation has first been observed in the neutral kaon system. In the Standard Model of particle physics the mixing of quarks is described by the Cabibbo-Kobayashi-Maskawa (CKM) matrix. The CKM matrix has four free parameters, three Euler angles, and one complex phase. The latter allows CP violation to occur within the Standard Model. CP violation in the kaon system is tiny and implies theoretical uncertainties. However, the Standard Model predicts large effects in the B-meson system.

## 2.2 The Large Hadron Collider

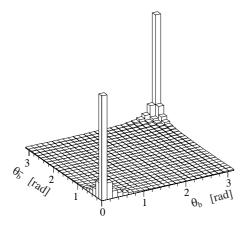

The Large Hadron Collider (LHC) is a high luminosity proton-proton collider with a center of mass energy of 14 TeV. Luminosity is a magnitude which corresponds to the number of particle interactions at the collision point. Compared to other experiments that are in operation or under construction, LHCb will be the richest source for B-mesons. Figure 2.1 shows the polar angles  $\theta$  at which b and  $\overline{b}$ -hadrons have to be expected. The depicted maxima suggest that the LHCb detector should cover low polar angles. The polar angle is defined with respect to the beam axis in the pp center-of-mass system.

The LHCb experiment plans to run with an average luminosity of  $2 \times 10^{32} cm^{-2} s^{-1}$ . However, LHCb's luminosity is less compared to Belle  $(4.6 \times 10^{33} cm^{-2} s^{-1})$  [7] and BaBar

Figure 2.1: Polar angles of the band b-hadrons calculated by the PYTHIA event generator. Figure from LHCb TP [1]

$(7.25 \times 10^{33} cm^{-2} s^{-1})$  [5] since events with multiple interactions should be minimized. Events at LHCb are characterized by proton-proton (pp) interactions, which produce about  $10^{12} b\bar{b}$  pairs in one year. The LHCb detector is designed to exploit the large number of b-hadrons produced in order to make precision studies of CP asymmetries and rare decays in B-meson systems. However, the amount of interesting events is in the order of  $10^{-5}$  or less and thus, requiring an effective trigger system.

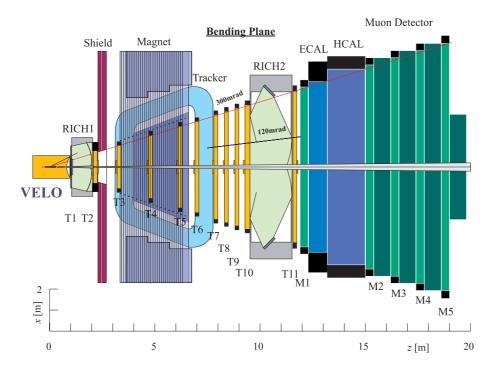

#### 2.3 The LHCb Detector

The LHCb detector is a single-arm spectrometer with a forward angular coverage from 10 mrad to 300 mrad in horizontal projection and to 250 mrad in the vertical projection [1]. The layout of the spectrometer is shown in figure 2.2.

The detector can reconstruct B-decay vertices with a resolution in the micrometer range and provides particle identification for charged particles. A high performance trigger, which is optimized to select events with B-mesons efficiently, is foreseen. Based on particles with large transverse momentum and displaced secondary vertices a trigger decision is made.

LHCb comprises a number of different sub-detectors. Parts of the detector are outlined briefly:

- The beam pipe around the interaction point is divided into two conical sections. The first leads through RICH1 and has an opening angle of 25 mrad, the second section has a 10 mrad opening angle.

- The Vertex Locator (VELO) features a series of silicon stations placed along the beam direction. It is used to provide precise measurements of track coordinates close to the interaction region. It is discussed in more detail in 3.1.

- Two Ring Image Cherenkov Detectors identify charged particles over the momentum range 1-150 GeV/c. The upstream detector (RICH1) contains both a silicon aerogel and a  $C_4F_{10}$  gas radiator whilst RICH2, located downstream behind the magnet, contains a  $CF_4$  radiator. Three different radiators are used to cover the full momentum range.

**Figure 2.2:** Schematic drawing of the LHCb detector as seen from above. Figure from the VELO TDR [8].

- The spectrometer dipole magnet is located close to the interaction region to minimize its size. Magnets are used to bend charged particle tracks depending on their momentum and charge.

- The tracking system (T1-T9) consists out of a series of stations containing Inner (IT) and Outer Tracker (OT) components. The tracker provides track reconstruction and precise momentum measurement for charged particles.

- The calorimeter system comprises a scintillator pad detector (SPD), a preshower detector (PS), an electromagnetic calorimeter (ECAL), and a hadron calorimeter (HCAL). The purpose of the calorimeter system is to provide identification of electrons and hadrons for trigger and offline analysis, with measurement of position and energy.

- The muon detector (M1-M5) provides muon identification and Level-0 trigger information.

The detector is presented as foreseen in the LHCb TP [1]. However, the latest developments in the LHCb experiment do foresee a detector which implies reduced material budget — the LHCb light detector. Changes to the detector will also affect the Level-1 trigger input since it is planned to have a magnetic field in the VELO to get momentum information. A special station called TT1 is also foreseen as Level-1 input. However, the amount of data and the data rate, which are very important boundary conditions, do not change.

#### 2.4 The LHCb Trigger System

The detector produces a total data rate of 40 TByte/s and thus exceeds capabilities of present network architectures and storage media. LHCb implements a selective four stage trigger system that analyzes the sub-detectors in different trigger stages. Events with B-mesons can be distinguished from other inelastic pp interactions by the presence of secondary vertices and particles with high transverse momentum  $p_T$ . Figure 2.3 shows the different stages of the LHCb trigger system.

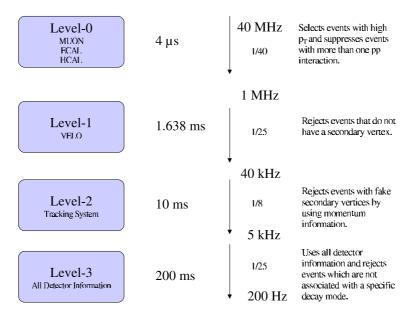

Figure 2.3: LHCb trigger system stages including latencies and suppression rates.

The pipeline comprises the following stages:

- Level-0 comprises three high  $p_T$  triggers, which operate on muons, electrons, and hadrons. Additionally a pile-up veto is issued, which suppresses events with more than one pp interaction. The Level-0 operates on the bunch-crossing frequency of 40.08 MHz. The maximum Level-0 output rate is limited by the Level-0 derandomizer and accounts to 1.11 MHz. The latency of the Level-0 is set to be 4.0  $\mu s$ .

- The Level-1 selects events, which have a secondary vertex. The Level-1 operates at Level-0 output rate of 1.11 MHz and reduces the event rate to 40 kHz. The Level-1 overall latency has been set to 1.638 ms. The Level-1 trigger is discussed in chapter 3.

- The **Level-2** eliminates events with fake secondary vertices by using momentum information. The Level-2 operates at the Level-1 output rate and achieves a suppression factor of 8. Its latency is about 10 ms.

- The Level-3 uses all detector information and selects events, which are associated with specific b-hadron decay modes. Level-3 has a latency of about 200 ms and accepts events at the data recording rate of 200 Hz.

A specific feature of LHCb is the fact that Level-0 and Level-1 trigger decisions are transmitted by the TFC. The TFC also distributes the LHC reference clock which runs at 40 MHz. The clock is used to drive all the electronics such that a synchronous readout is possible. Control commands which are used to reset the front-end electronics or to recover from an error condition are also transferred by the TFC. In case of a calibration event the TFC has to guarantee that triggers corresponding to calibration events are accepted. The TFC distribution network is based on the Trigger, Timing, and Control (TTC) network developed by the RD12 experiment [9]. The network transmits the information over an optical channel. If a device depends on timing information it must incorporate a TTC receiver chip (TTCrx).

# Chapter 3

# The LHCb Level-1 Trigger

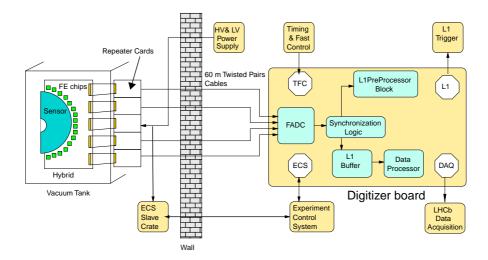

The Vertex Locator is the data source for the Level-1 trigger. It is comprised of a number of silicon stations which allow precision measurements of charged particle tracks around the interaction region. The detector is read out by front-end chips in a radiation environment. The data gets digitized and preprocessed by the Off Detector Electronics and is finally sent to the input stage of the Level-1 processor farm. The Readout Units assemble sub-events out of data belonging to the same event and send that data to a specific compute node. The input rate is 1 MHz on average with peak values up to 1.11 MHz.

A track finding algorithm performs its track finding task once all sub-events have arrived. Upon completion of the algorithm a result message is sent to the Level-1 Decision Unit which produces the 40 kHz output signal.

#### 3.1 Vertex Locator

The vertex locator is the data source for the Level-1 trigger. Furthermore, a second source of input will be part of the final system; the trigger tracker TT1 will provide momentum information. TT1 will be a full Si tracker composed of two half-stations being located between RICH1 and the magnet (see figure 2.2 for location of the RICH1 and the magnet). The final detector layout is changed at the time of writing. Some information which is more current than figure 2.2 can be obtained from a talk by Tatsuya Nakada given for the LHCC<sup>1</sup> referees [10].

The vertex locator (VELO) provides information for precise reconstruction of charged particle tracks around the interaction region. Displaced secondary vertices are a significant sign of b-hadron decay and thus vital to the experiment. The detector features a series of silicon stations which are placed along the beam axis. It is the only detector which also provides some backwards information which is used to separate events with more than one primary vertex. The location of the VELO within the LHCb detector can be seen in figure 2.2.

<sup>&</sup>lt;sup>1</sup>Large Hadron Collider Committee

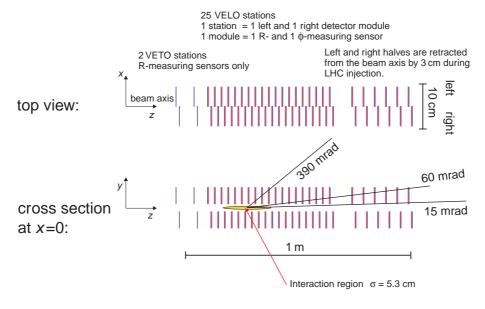

Since the geometry of the VELO is not final at the time of writing the design as described in the VELO TDR [8] is discussed instead. The final geometry will probably have less stations which reduces the amount of data that has to be handled by the Level-1 trigger. However, since the trigger tracker has been introduced as an additional input the final amount of data does not change significantly. The TDR VELO comprises 25 stations each providing an R and  $\phi$  measurement. The arrangement of the disc-shaped stations is shown in figure 3.1.

Figure 3.1: Arrangement of the detector stations along the beam axis. The interaction region  $(\pm \sigma)$  is depicted as well. Figure from VELO TDR [8]

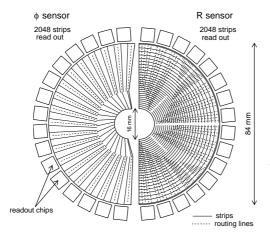

The two stations depicted on the left are exclusively R measuring stations and part of the Level-0 pile-up veto system. The TDR VELO is located outside the magnetic field which implies straight tracks. However, in the final VELO design the detector will most likely be placed in a magnetic field to gain momentum information. Detector information is read out by analyzing the 204.800 analog readout channels. One VELO station is made of four half-circular silicon sensors covering the left and right part and measuring R and  $\Phi$  respectively. Figure 3.2 shows a schematic view of a R- and  $\Phi$ - measuring sensor.

The R-measuring sensor has azimuthal strips at constant radius whilst the  $\Phi$ -measuring sensor has radial strips with a stereo angle to resolve track finding ambiguities. Both sensor types span 182° and have variable strip pitches. The R-sensor has strip pitches from  $40\mu m$  up to  $92\mu m$  whilst the  $\Phi$ -sensor has strip pitches from  $37\mu m$  to  $98 \mu m$ . The innermost radius for both sensor types is 8 mm and the outermost radius 42 mm. The detector has a low occupancy of less than 1%. Test-beam measurements have shown R-sensor resolutions in between  $3.6\mu m$  and  $4.6\mu m$  depending on the strip pitch and the track angle[8].

Figure 3.2 also shows the 16 front-end chips mounted on one sensor. Every front-end chip will read out 128 channels in a radiation environment. Currently two candidates do exist that are under study:

• The SCTA\_VELO, a chip derived from the SCT128A [11] developed for ATLAS [12].

3.1. Vertex Locator

Figure 3.2: Schematic view of a Rand  $\Phi$ - measuring sensor. Figure from VELO TDR [8]

• The BEETLE chip [13] developed in the ASIC laboratory of the Kirchhoff-Institut für Physik in Heidelberg [14].